- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄384279 > EDE2508ABSE-5C-E (ELPIDA MEMORY INC) 256M bits DDR2 SDRAM PDF資料下載

參數(shù)資料

| 型號: | EDE2508ABSE-5C-E |

| 廠商: | ELPIDA MEMORY INC |

| 元件分類: | DRAM |

| 英文描述: | 256M bits DDR2 SDRAM |

| 中文描述: | 32M X 8 DDR DRAM, 0.5 ns, PBGA60 |

| 封裝: | ROHS COMPLIANT, FBGA-60 |

| 文件頁數(shù): | 29/66頁 |

| 文件大?。?/td> | 708K |

| 代理商: | EDE2508ABSE-5C-E |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁當前第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁

EDE2508ABSE, EDE2516ABSE

Preliminary Data Sheet E0573E30 (Ver. 3.0)

29

DLL Enable/Disable

The DLL must be enabled for normal operation. DLL enable is required during power up initialization, and upon

returning to normal operation after having the DLL disabled. The DLL is automatically disabled when entering self-

refresh operation and is automatically re-enabled upon exit of self-refresh operation. Any time the DLL is enabled

(and subsequently reset), 200 clock cycles must occur before a read command can be issued to allow time for the

internal clock to be synchronized with the external clock. Failing to wait for synchronization to occur may result in a

violation of the tAC or tDQSCK parameters.

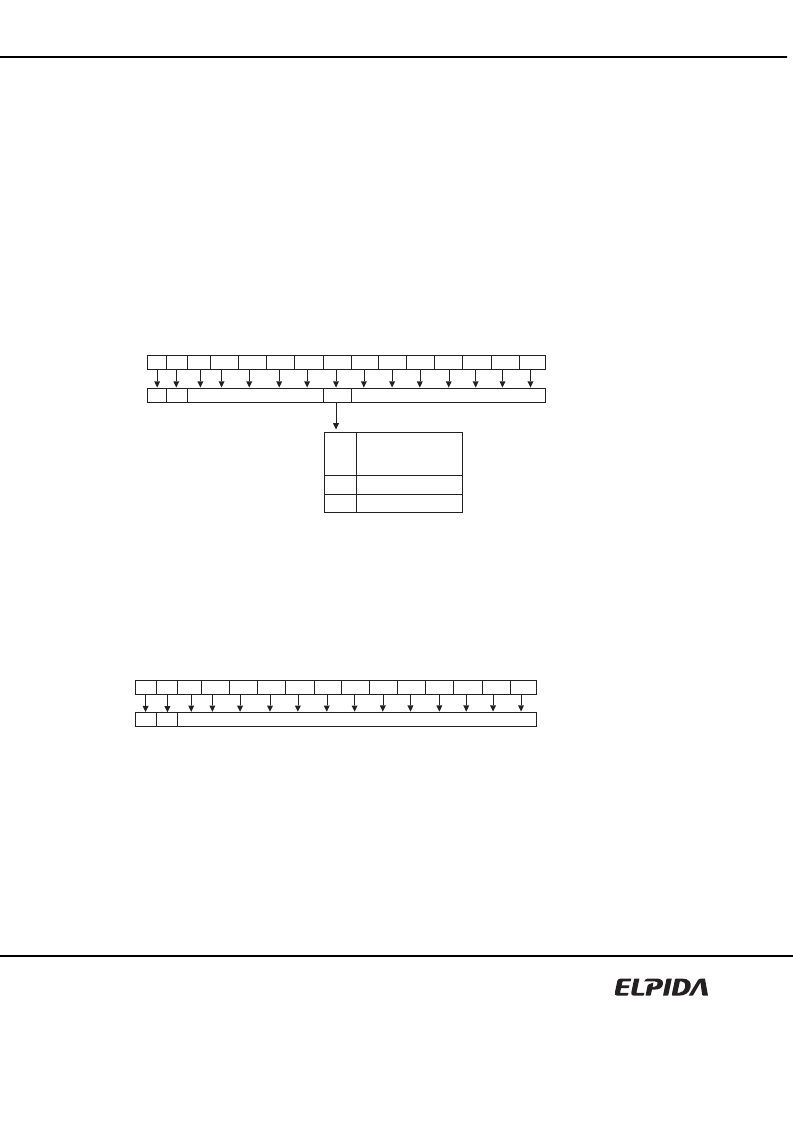

EMRS(2) Programming

*1

The extended mode register (2) controls refresh related features. The default value of the extended mode register

(2) is not defined, therefore the extended mode register (2) must be written after power-up for proper operation. The

extended mode register (2) is written by asserting low on CS, /RAS, /CAS, /WE, high on BA1 and low on BA0, while

controlling the states of address pins A0 to A12. The DDR2 SDRAM should be in all bank precharge with CKE

already high prior to writing into the extended mode register (2). The mode register set command cycle time (tMRD)

must be satisfied to complete the write operation to the extended mode register (2). Mode register contents can be

changed using the same command and clock cycle requirements during normal operation as long as all banks are in

the precharge state.

Address field

Extended mode register (2)

0*

1

0*

1

SRF

A11

A10

A9

A8

A7

A6

A5

A4

A3

A2

A1

A0

0

1

BA1 BA0 A12

A7

0

1

High Temperature

Self-refresh rate

Enable

Disable

Enable (Optional)

Note: 1 The rest bits in EMRS (2) is reserved for future use and all bits in EMRS (2) except A7, BA0 and BA1

must be programmed to 0 when setting the extended mode register (2) during initialization.

EMRS(2)

EMRS(3) Programming: Reserved

*1

Extended Mode Register(3)

0*

1

1

1

Address Field

A11

A10

A9

A8

A7

A6

A5

A4

A3

A2

A1

A0

BA1 BA0 A12

Note : 1. EMRS (3) is reserved for future use and all bits except BA0 and BA1 must be programmed

to 0 when setting the mode register during initialization.

EMRS(3)

相關PDF資料 |

PDF描述 |

|---|---|

| EDE2516ABSE-5C-E | 256M bits DDR2 SDRAM |

| EDE2508ABSE-6C-E | 256M bits DDR2 SDRAM |

| EDE2516ABSE-6C-E | 256M bits DDR2 SDRAM |

| EDE2508ABSE-6E-E | 256M bits DDR2 SDRAM |

| EDE2516ABSE-6E-E | 256M bits DDR2 SDRAM |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| EDE2508ABSE-6C-E | 制造商:ELPIDA 制造商全稱:Elpida Memory 功能描述:256M bits DDR2 SDRAM |

| EDE2508ABSE-6E-E | 制造商:ELPIDA 制造商全稱:Elpida Memory 功能描述:256M bits DDR2 SDRAM |

| EDE2508ABSE-GE | 制造商:ELPIDA 制造商全稱:Elpida Memory 功能描述:256M bits DDR2 SDRAM for HYPER DIMM |

| EDE2508ABSE-GE-E | 制造商:ELPIDA 制造商全稱:Elpida Memory 功能描述:256M bits DDR2 SDRAM for HYPER DIMM |

| EDE2508ACSE | 制造商:ELPIDA 制造商全稱:Elpida Memory 功能描述:256M bits DDR2 SDRAM |

發(fā)布緊急采購,3分鐘左右您將得到回復。