- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄19325 > EP2AGX45DF29I3N (Altera)IC ARRIA II GX FPGA 45K 780FBGA PDF資料下載

參數(shù)資料

| 型號: | EP2AGX45DF29I3N |

| 廠商: | Altera |

| 文件頁數(shù): | 70/90頁 |

| 文件大小: | 0K |

| 描述: | IC ARRIA II GX FPGA 45K 780FBGA |

| 產(chǎn)品培訓(xùn)模塊: | Three Reasons to Use FPGA's in Industrial Designs |

| 標(biāo)準(zhǔn)包裝: | 4 |

| 系列: | Arria II GX |

| LAB/CLB數(shù): | 1805 |

| 邏輯元件/單元數(shù): | 42959 |

| RAM 位總計(jì): | 3517440 |

| 輸入/輸出數(shù): | 364 |

| 電源電壓: | 0.87 V ~ 0.93 V |

| 安裝類型: | 表面貼裝 |

| 工作溫度: | -40°C ~ 100°C |

| 封裝/外殼: | 780-BBGA |

| 供應(yīng)商設(shè)備封裝: | 780-FBGA(29x29) |

| 其它名稱: | 544-2701 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁當(dāng)前第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁

1–64

Chapter 1: Device Datasheet for Arria II Devices

Switching Characteristics

December 2013

Altera Corporation

Table 1–54 lists the high-speed I/O timing for Arria II GZ devices.

fHSDR (data rate)

SERDES factor

J = 3 to 10

945

945

740

640

Mbps

SERDES factor

J = 2 (using

DDR registers)

Mbps

SERDES factor

J = 1 (using

SDR registers)

Mbps

Soft-CDR PPM

tolerance

Soft-CDR

mode

—

300

—

300

—

300

—

300

PPM

DPA run length

DPA mode

—

10,000

—

10,000

—

10,000

—

10,000

UI

Sampling

window (SW)

Non-DPA mode

—

300

—

300

—

350

—

400

ps

Notes to Table 1–53:

(1) fHSCLK_IN = fHSDR / W. Use W to determine the supported selection of input reference clock frequencies for the desired data rate.

(2) Applicable for interfacing with DPA receivers only. For interfacing with non-DPA receivers, you must calculate the leftover timing margin in the

receiver by performing link timing closure analysis. For Arria II GX transmitter to Arria II GX non-DPA receiver, the maximum supported data

rate is 945 Mbps. For data rates above 840 Mbps, perform PCB trace compensation by adjusting the PCB trace length for LVDS channels to

improve channel-to-channel skews.

(3) The minimum and maximum specification depends on the clock source (for example, PLL and clock pin) and the clock routing resource you

use (global, regional, or local). The I/O differential buffer and input register do not have a minimum toggle rate.

(4) The specification is only applicable under the influence of core noise.

(5) Applicable for true LVDS using dedicated SERDES only.

(6) Dedicated SERDES and DPA features are only available on the right banks.

(7) You must calculate the leftover timing margin in the receiver by performing link timing closure analysis. You must consider the board skew

margin, transmitter channel-to-channel skew, and the receiver sampling margin to determine the leftover timing margin.

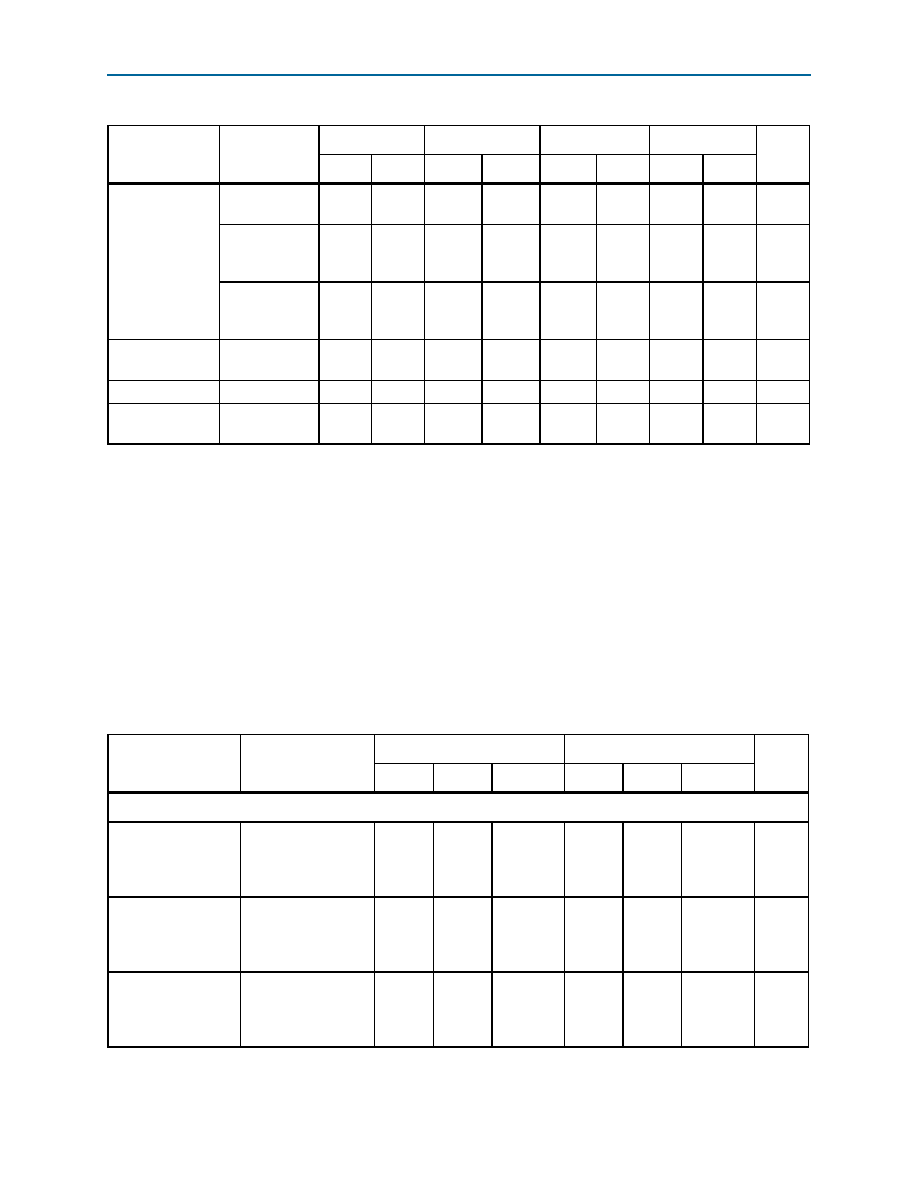

Table 1–53. High-Speed I/O Specifications for Arria II GX Devices (Part 4 of 4)

Symbol

Conditions

I3

C4

C5,I5

C6

Unit

Min

Max

Min

Max

Min

Max

Min

Max

Table 1–54. High-Speed I/O Specifications for Arria II GZ Devices (Note 1), (2), (10) (Part 1 of 3)

Symbol

Conditions

C3, I3

C4, I4

Unit

Min

Typ

Max

Min

Typ

Max

Clock

fHSCLK_in (input clock

frequency) true

differential I/O

standards

Clock boost factor

W = 1 to 40 (3)

5

—

717

5

—

717

MHz

fHSCLK_in (input clock

frequency) single

ended I/O standards

Clock boost factor

W = 1 to 40 (3)

5

—

717

5

—

717

MHz

fHSCLK_in (input clock

frequency) single

ended I/O standards

Clock boost factor

W = 1 to 40 (3)

5

—

420

5

—

420

MHz

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| ASM25DRMT-S288 | CONN EDGECARD 50POS .156 EXTEND |

| EPF10K100ARC240-1N | IC FLEX 10KA FPGA 100K 240-RQFP |

| RAC10-12DA-ST | CONV AC/DC 90-264VAC +/-12V .38A |

| TACL105K010RTL | CAP TANT 1UF 10V 10% 0603 |

| TCN75-5.0MOAG | IC TEMP SENSOR SRL 5.0V 8SOIC |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| EP2AGX45DF29I5 | 功能描述:FPGA - 現(xiàn)場可編程門陣列 FPGA - Arria II GX 1805 LABs 364 IOs RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 柵極數(shù)量: 邏輯塊數(shù)量:943 內(nèi)嵌式塊RAM - EBR:1956 kbit 輸入/輸出端數(shù)量:128 最大工作頻率:800 MHz 工作電源電壓:1.1 V 最大工作溫度:+ 70 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FBGA-256 |

| EP2AGX45DF29I5N | 功能描述:FPGA - 現(xiàn)場可編程門陣列 FPGA - Arria II GX 1805 LABs 364 IOs RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 柵極數(shù)量: 邏輯塊數(shù)量:943 內(nèi)嵌式塊RAM - EBR:1956 kbit 輸入/輸出端數(shù)量:128 最大工作頻率:800 MHz 工作電源電壓:1.1 V 最大工作溫度:+ 70 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FBGA-256 |

| EP2AGX65CU17C4 | 功能描述:FPGA - 現(xiàn)場可編程門陣列 FPGA - Arria II GX 2530 LABs 156 IOs RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 柵極數(shù)量: 邏輯塊數(shù)量:943 內(nèi)嵌式塊RAM - EBR:1956 kbit 輸入/輸出端數(shù)量:128 最大工作頻率:800 MHz 工作電源電壓:1.1 V 最大工作溫度:+ 70 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FBGA-256 |

| EP2AGX65CU17C4N | 功能描述:FPGA - 現(xiàn)場可編程門陣列 FPGA - Arria II GX 2530 LABs 156 IOs RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 柵極數(shù)量: 邏輯塊數(shù)量:943 內(nèi)嵌式塊RAM - EBR:1956 kbit 輸入/輸出端數(shù)量:128 最大工作頻率:800 MHz 工作電源電壓:1.1 V 最大工作溫度:+ 70 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FBGA-256 |

| EP2AGX65CU17C5 | 功能描述:FPGA - 現(xiàn)場可編程門陣列 FPGA - Arria II GX 2530 LABs 156 IOs RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 柵極數(shù)量: 邏輯塊數(shù)量:943 內(nèi)嵌式塊RAM - EBR:1956 kbit 輸入/輸出端數(shù)量:128 最大工作頻率:800 MHz 工作電源電壓:1.1 V 最大工作溫度:+ 70 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FBGA-256 |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。