- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄19312 > EP4S100G5F45I2N (Altera)IC STRATIX IV GT 530K 1932FBGA PDF資料下載

參數(shù)資料

| 型號(hào): | EP4S100G5F45I2N |

| 廠商: | Altera |

| 文件頁(yè)數(shù): | 6/82頁(yè) |

| 文件大小: | 0K |

| 描述: | IC STRATIX IV GT 530K 1932FBGA |

| 產(chǎn)品培訓(xùn)模塊: | Stratix IV FPGAs Three Reasons to Use FPGA's in Industrial Designs |

| 特色產(chǎn)品: | Stratix? IV Series FPGAs |

| 標(biāo)準(zhǔn)包裝: | 3 |

| 系列: | STRATIX® IV GT |

| LAB/CLB數(shù): | 21248 |

| 邏輯元件/單元數(shù): | 531200 |

| RAM 位總計(jì): | 28033024 |

| 輸入/輸出數(shù): | 781 |

| 電源電壓: | 0.92 V ~ 0.98 V |

| 安裝類型: | 表面貼裝 |

| 工作溫度: | -40°C ~ 100°C |

| 封裝/外殼: | 1932-BBGA |

| 供應(yīng)商設(shè)備封裝: | 1932-FBGA(45x45) |

| 其它名稱: | 544-2637 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)當(dāng)前第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)

Chapter 1: DC and Switching Characteristics for Stratix IV Devices

1–6

Electrical Characteristics

March 2014

Altera Corporation

Stratix IV Device Handbook

Volume 4: Device Datasheet and Addendum

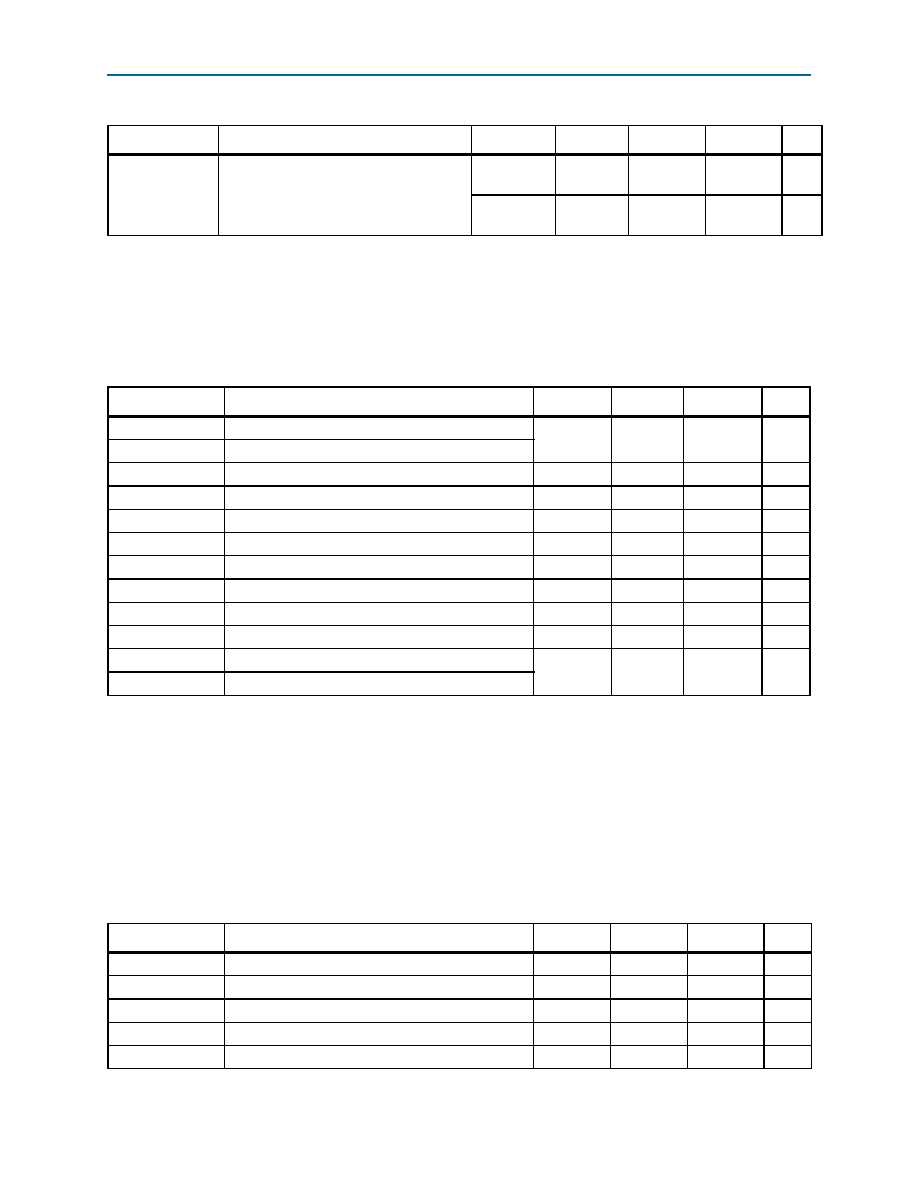

Table 1–7 lists the transceiver power supply recommended operating conditions for

Stratix IV GX devices.

Table 1–8 lists the recommended operating conditions for the Stratix IV GT

transceiver power supply.

tRAMP

Power supply ramp time

Normal POR

(PORSEL=0)

0.05

—

100

ms

Fast POR

(PORSEL=1)

0.05

—

4

ms

Notes to Table 1–6:

(1) If you do not use the volatile security key, you may connect the VCCBAT to either GND or a 3.0-V power supply.

(2) VCCPD must be 2.5 V when VCCIO is 2.5, 1.8, 1.5, or 1.2 V. VCCPD must be 3.0 V when VCCIO is 3.0 V.

Table 1–6. Recommended Operating Conditions for Stratix IV Devices (Part 2 of 2)

Symbol

Description

Condition

Minimum

Typical

Maximum

Unit

Table 1–7. Transceiver Power Supply Operating Conditions for Stratix IV GX Devices (1)

Symbol

Description

Minimum

Typical

Maximum

Unit

VCCA_L

Transceiver high voltage power (left side)

2.85/2.375

3.15/2.625

V

VCCA_R

Transceiver high voltage power (right side)

VCCHIP_L

Transceiver HIP digital power (left side)

0.87

0.9

0.93

V

VCCHIP_R

Transceiver HIP digital power (right side)

0.87

0.9

0.93

V

VCCR_L

Receiver power (left side)

1.045

1.1

1.155

V

VCCR_R

Receiver power (right side)

1.045

1.1

1.155

V

VCCT_L

Transmitter power (left side)

1.045

1.1

1.155

V

VCCT_R

Transmitter power (right side)

1.045

1.1

1.155

V

VCCL_GXBLn (3)

Transceiver clock power (left side)

1.05

1.1

1.15

V

VCCL_GXBRn (3)

Transceiver clock power (right side)

1.05

1.1

1.15

V

VCCH_GXBLn (3)

Transmitter output buffer power (left side)

1.33/1.425

1.47/1.575

V

VCCH_GXBRn (3)

Transmitter output buffer power (right side)

Notes to Table 1–7:

(1) Transceiver power supplies do not have power-on-reset (POR) circuitry. After initial power-up, violating the transceiver power supply operating

conditions could lead to unpredictable link behavior.

(2) VCCA_L/R must be connected to a 3.0-V supply if the clock multiplier unit (CMU) phase-locked loop (PLL), receiver clock data recovery (CDR),

or both, are configured at a base data rate > 4.25 Gbps. For data rates up to 4.25 Gbps, you can connect VCCA_L/R to either 3.0 V or 2.5 V.

(3) n = 0, 1, 2, or 3.

(4) VCCH_GXBL/R must be connected to a 1.4-V supply if the transmitter channel data rate is > 6.5 Gbps. For data rates up to 6.5 Gbps, you can

connect VCCH_GXBL/R to either 1.4 V or 1.5 V.

Table 1–8. Transceiver Power Supply Operating Conditions for Stratix IV GT Devices (Part 1 of 2) (1), (2)

Symbol

Description

Minimum

Typical

Maximum

Unit

VCCA_L

Transceiver high voltage power (left side)

3.17

3.3

3.43

V

VCCA_R

Transceiver high voltage power (right side)

3.17

3.3

3.43

V

VCCHIP_L

Transceiver HIP digital power (left side)

0.92

0.95

0.98

V

VCCHIP_R

Transceiver HIP digital power (right side)

0.92

0.95

0.98

V

VCCR_L

Receiver power (left side)

1.15

1.2

1.25

V

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| RMA43DRMH | CONN EDGECARD 86POS .125 SQ WW |

| KA79L15AZTA | IC REG LDO -15V .1A TO-92 |

| RW2-4809D/B | CONV DC/DC 2W 36-72VIN +/-09VOUT |

| RSA43DRMD | CONN EDGECARD 86POS .125 SQ WW |

| ECM06DCWS | CONN EDGECARD 12POS DIP .156 SLD |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| EP4S100G5F45I3 | 功能描述:FPGA - 現(xiàn)場(chǎng)可編程門陣列 FPGA - Stratix IV 21248 LABs 781 IOs RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 柵極數(shù)量: 邏輯塊數(shù)量:943 內(nèi)嵌式塊RAM - EBR:1956 kbit 輸入/輸出端數(shù)量:128 最大工作頻率:800 MHz 工作電源電壓:1.1 V 最大工作溫度:+ 70 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FBGA-256 |

| EP4S100G5F45I3N | 功能描述:FPGA - 現(xiàn)場(chǎng)可編程門陣列 FPGA - Stratix IV 21248 LABs 781 IOs RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 柵極數(shù)量: 邏輯塊數(shù)量:943 內(nèi)嵌式塊RAM - EBR:1956 kbit 輸入/輸出端數(shù)量:128 最大工作頻率:800 MHz 工作電源電壓:1.1 V 最大工作溫度:+ 70 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FBGA-256 |

| EP4S100G5H40C2NES1 | 制造商:Altera Corporation 功能描述:IC FPGA 654 I/O 1517HBGA |

| EP4S100G5H40I1 | 功能描述:FPGA - 現(xiàn)場(chǎng)可編程門陣列 FPGA - Stratix IV 21248 LABs 781 IOs RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 柵極數(shù)量: 邏輯塊數(shù)量:943 內(nèi)嵌式塊RAM - EBR:1956 kbit 輸入/輸出端數(shù)量:128 最大工作頻率:800 MHz 工作電源電壓:1.1 V 最大工作溫度:+ 70 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FBGA-256 |

| EP4S100G5H40I1N | 功能描述:FPGA - 現(xiàn)場(chǎng)可編程門陣列 FPGA - Stratix IV 21248 LABs 781 IOs RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 柵極數(shù)量: 邏輯塊數(shù)量:943 內(nèi)嵌式塊RAM - EBR:1956 kbit 輸入/輸出端數(shù)量:128 最大工作頻率:800 MHz 工作電源電壓:1.1 V 最大工作溫度:+ 70 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FBGA-256 |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。