- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄4330 > EP4SGX110HF35C4 (Altera)IC STRATIX IV FPGA 110K 1152FBGA PDF資料下載

參數(shù)資料

| 型號: | EP4SGX110HF35C4 |

| 廠商: | Altera |

| 文件頁數(shù): | 75/82頁 |

| 文件大?。?/td> | 0K |

| 描述: | IC STRATIX IV FPGA 110K 1152FBGA |

| 產(chǎn)品培訓模塊: | Three Reasons to Use FPGA's in Industrial Designs |

| 標準包裝: | 3 |

| 系列: | Stratix® IV GX |

| LAB/CLB數(shù): | 4224 |

| 邏輯元件/單元數(shù): | 105600 |

| RAM 位總計: | 9793536 |

| 輸入/輸出數(shù): | 488 |

| 電源電壓: | 0.87 V ~ 0.93 V |

| 安裝類型: | 表面貼裝 |

| 工作溫度: | 0°C ~ 85°C |

| 封裝/外殼: | 1152-BBGA |

| 供應(yīng)商設(shè)備封裝: | 1152-FBGA(27x27) |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁當前第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁

Chapter 1: DC and Switching Characteristics for Stratix IV Devices

1–69

Glossary

March 2014

Altera Corporation

Stratix IV Device Handbook

Volume 4: Device Datasheet and Addendum

November 2009

4.0

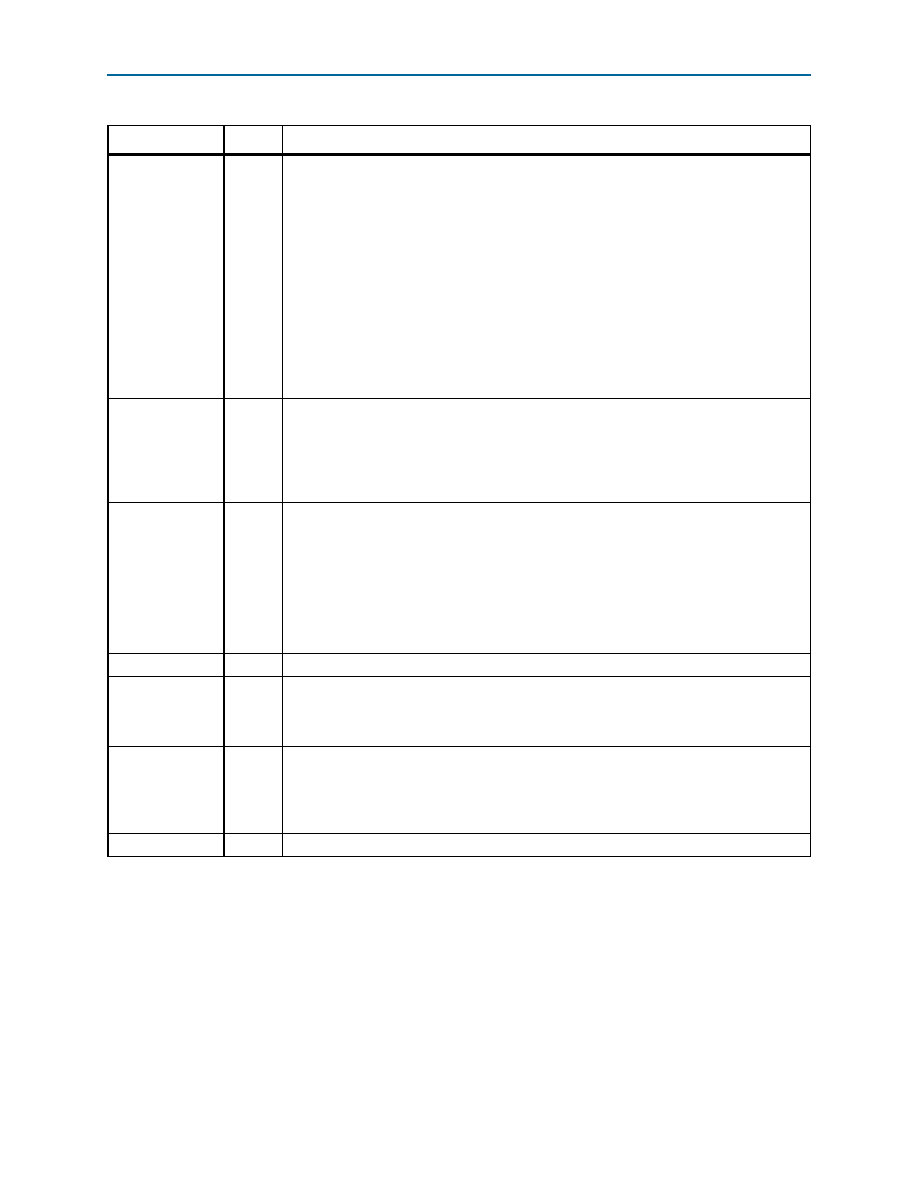

■ Added Table 1–9, Table 1–15, Table 1–38, and Table 1–39.

■ Added Figure 1–5 and Figure 1–6.

■ Added the “Transceiver Datapath PCS Latency” section.

■ Updated the “Electrical Characteristics”, “Operating Conditions”, and “I/O Timing”

sections.

■ All tables updated except Table 1–16, Table 1–24, Table 1–25, Table 1–26, Table 1–27,

Table 1–33, Table 1–34, and Table 1–45.

■ Updated Figure 1–2 and Figure 1–3.

■ Updated Equation 1–1.

■ Deleted Table 1-28, Table 1-29, Table 1-30, Table 1-42, Table 1-43, and Table 1-44.

■ Minor text edits.

June 2009

3.1

■ Added “Preliminary Specifications” to the footer of each page.

■ Updated Table 1–1, Table 1–2, Table 1–7, Table 1–10, Table 1–11, Table 1–12,

Table 1–21, Table 1–22, Table 1–23, Table 1–25, Table 1–37, Table 1–38, Table 1–39,

Table 1–40, and Table 1–44.

■ Minor text edits.

March 2009

3.0

■ Replaced Table 1–31 and Table 1–37.

■ Updated Table 1–1, Table 1–2, Table 1–5, Table 1–19, Table 1–41, Table 1–44,

Table 1–45, Table 1–49, and Table 1–51.

■ Added Table 1–21, Table 1–46, and Table 1–47

■ Added Figure 1–3.

■ Removed “Timing Model”, “Preliminary and Final Timing”, “I/O Timing Measurement

Methodology”, “I/O Default Capacitive Loading”, and “Referenced Documents” sections.

December 2008

2.1

Minor changes.

November 2008

2.0

■ Minor text edits.

■ Updated Table 1–19, Table 1–32, Table 1–34 - Table 1–39.

■ Minor text edits.

August 2008

1.1

■ Updated Table 1–1, Table 1–2, Table 1–4, Table 1–5, and Table 1–26.

■ Removed figures from “Transceiver Performance Specifications” on page 1–10 that are

repeated in the glossary.

■ Minor text edits and an additional note to Table 1–26.

May 2008

1.0

Initial release.

Table 1–55. Document Revision History (Part 3 of 3)

Date

Version

Changes

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| RMM43DRAN | CONN EDGECARD 86POS R/A .156 SLD |

| EP1S60B956C6N | IC STRATIX FPGA 60K LE 956-BGA |

| EP1S60F1508C6N | IC STRATIX FPGA 60K LE 1508-FBGA |

| A54SX32-1CQ256 | IC FPGA SX 48K GATES 256-CQFP |

| RSM43DRAH | CONN EDGECARD 86POS R/A .156 SLD |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| EP4SGX110HF35C4N | 功能描述:FPGA - 現(xiàn)場可編程門陣列 FPGA - Stratix IV GX 4224 LABs 488 IOs RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 柵極數(shù)量: 邏輯塊數(shù)量:943 內(nèi)嵌式塊RAM - EBR:1956 kbit 輸入/輸出端數(shù)量:128 最大工作頻率:800 MHz 工作電源電壓:1.1 V 最大工作溫度:+ 70 C 安裝風格:SMD/SMT 封裝 / 箱體:FBGA-256 |

| EP4SGX110HF35I3 | 功能描述:FPGA - 現(xiàn)場可編程門陣列 FPGA - Stratix IV GX 4224 LABs 488 IOs RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 柵極數(shù)量: 邏輯塊數(shù)量:943 內(nèi)嵌式塊RAM - EBR:1956 kbit 輸入/輸出端數(shù)量:128 最大工作頻率:800 MHz 工作電源電壓:1.1 V 最大工作溫度:+ 70 C 安裝風格:SMD/SMT 封裝 / 箱體:FBGA-256 |

| EP4SGX110HF35I3N | 功能描述:FPGA - 現(xiàn)場可編程門陣列 FPGA - Stratix IV GX 4224 LABs 488 IOs RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 柵極數(shù)量: 邏輯塊數(shù)量:943 內(nèi)嵌式塊RAM - EBR:1956 kbit 輸入/輸出端數(shù)量:128 最大工作頻率:800 MHz 工作電源電壓:1.1 V 最大工作溫度:+ 70 C 安裝風格:SMD/SMT 封裝 / 箱體:FBGA-256 |

| EP4SGX110HF35I4 | 功能描述:FPGA - 現(xiàn)場可編程門陣列 FPGA - Stratix IV GX 4224 LABs 488 IOs RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 柵極數(shù)量: 邏輯塊數(shù)量:943 內(nèi)嵌式塊RAM - EBR:1956 kbit 輸入/輸出端數(shù)量:128 最大工作頻率:800 MHz 工作電源電壓:1.1 V 最大工作溫度:+ 70 C 安裝風格:SMD/SMT 封裝 / 箱體:FBGA-256 |

| EP4SGX110HF35I4N | 功能描述:FPGA - 現(xiàn)場可編程門陣列 FPGA - Stratix IV GX 4224 LABs 488 IOs RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 柵極數(shù)量: 邏輯塊數(shù)量:943 內(nèi)嵌式塊RAM - EBR:1956 kbit 輸入/輸出端數(shù)量:128 最大工作頻率:800 MHz 工作電源電壓:1.1 V 最大工作溫度:+ 70 C 安裝風格:SMD/SMT 封裝 / 箱體:FBGA-256 |

發(fā)布緊急采購,3分鐘左右您將得到回復。