- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄19352 > EPF6016AQC208-2 (Altera)IC FLEX 6000 FPGA 16K 208-PQFP PDF資料下載

參數(shù)資料

| 型號: | EPF6016AQC208-2 |

| 廠商: | Altera |

| 文件頁數(shù): | 26/52頁 |

| 文件大小: | 0K |

| 描述: | IC FLEX 6000 FPGA 16K 208-PQFP |

| 產(chǎn)品培訓模塊: | Three Reasons to Use FPGA's in Industrial Designs |

| 標準包裝: | 144 |

| 系列: | FLEX 6000 |

| LAB/CLB數(shù): | 132 |

| 邏輯元件/單元數(shù): | 1320 |

| 輸入/輸出數(shù): | 171 |

| 門數(shù): | 16000 |

| 電源電壓: | 3 V ~ 3.6 V |

| 安裝類型: | 表面貼裝 |

| 工作溫度: | 0°C ~ 85°C |

| 封裝/外殼: | 208-BFQFP |

| 供應(yīng)商設(shè)備封裝: | 208-PQFP(28x28) |

| 產(chǎn)品目錄頁面: | 602 (CN2011-ZH PDF) |

| 其它名稱: | 544-1272 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁當前第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁

32

Altera Corporation

FLEX 6000 Programmable Logic Device Family Data Sheet

Notes to tables:

(1)

(2)

Minimum DC input is –0.5 V. During transitions, the inputs may undershoot to –2.0 V or overshoot to 7.0 V for

input currents less than 100 mA and periods shorter than 20 ns.

(3)

Numbers in parentheses are for industrial-temperature-range devices.

(4)

Maximum VCC rise time to 100 ms. VCC must rise monotonically.

(5)

Typical values are for TA = 25° C and VCC = 5.0 V.

(6)

These values are specified under the FLEX 6000 Recommended Operating Conditions shown in Table 12 on

(7)

The IOH parameter refers to high-level TTL or CMOS output current.

(8)

The IOL parameter refers to low-level TTL, PCI, or CMOS output current. This parameter applies to open-drain pins

as well as output pins.

(9)

Capacitance is sample-tested only.

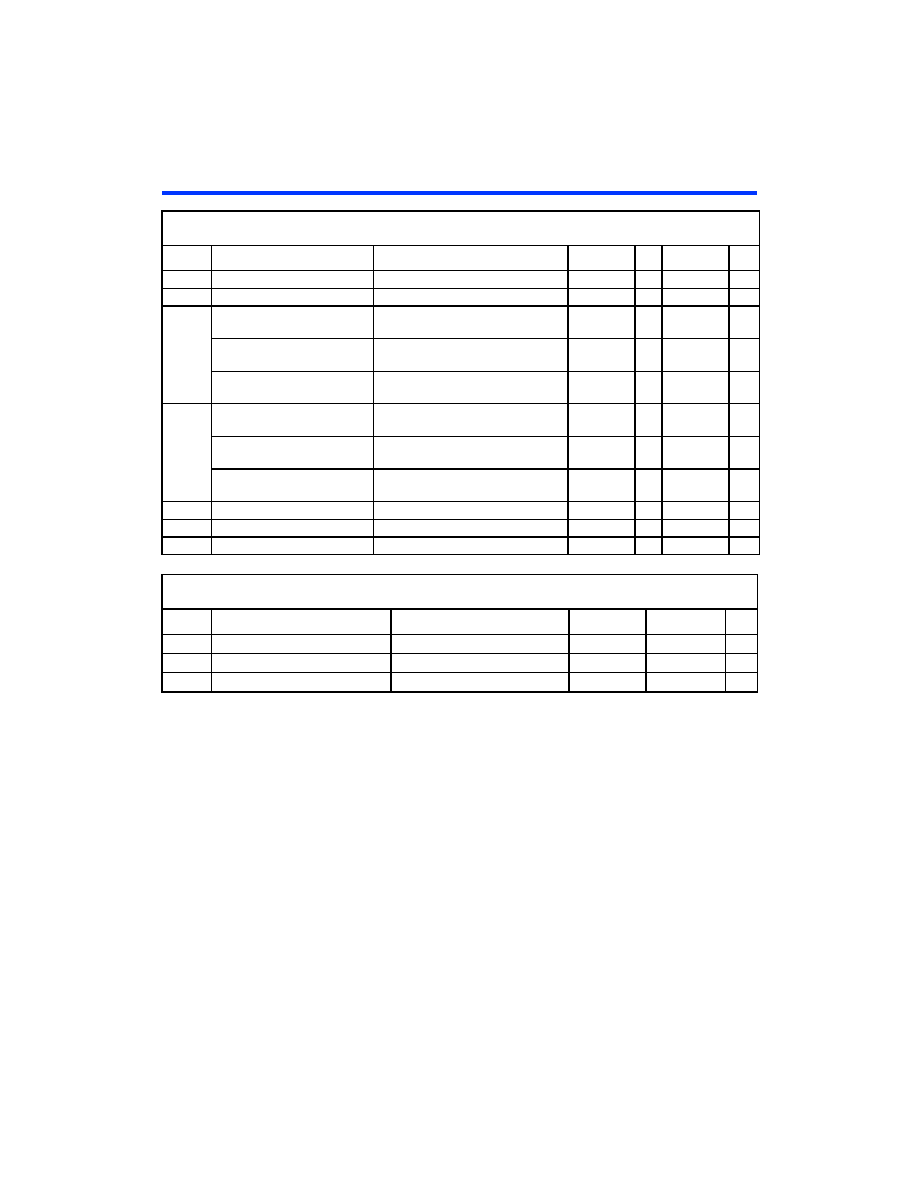

Table 13. FLEX 6000 5.0-V Device DC Operating Conditions

Symbol

Parameter

Conditions

Min

Typ

Max

Unit

VIH

High-level input voltage

2.0

VCCINT + 0.5

V

VIL

Low-level input voltage

–0.5

0.8

V

VOH

5.0-V high-level TTL output

voltage

2.4

V

3.3-V high-level TTL output

voltage

2.4

V

3.3-V high-level CMOS output

voltage

VCCIO –0.2

V

VOL

5.0-V low-level TTL output

voltage

0.45

V

3.3-V low-level TTL output

voltage

0.45

V

3.3-V low-level CMOS output

voltage

0.2

V

II

Input pin leakage current

–10

10

A

IOZ

–40

40

A

ICC0

VCC supply current (standby)

VI = ground, no load

0.5

5

mA

Table 14. FLEX 6000 5.0-V Device Capacitance

Symbol

Parameter

Conditions

Min

Max

Unit

CIN

Input capacitance for I/O pin

VIN = 0 V, f = 1.0 MHz

8pF

CINCLK

Input capacitance for dedicated input VIN = 0 V, f = 1.0 MHz

12

pF

COUT

Output capacitance

VOUT = 0 V, f = 1.0 MHz

8pF

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| VI-BND-CY-F3 | CONVERTER MOD DC/DC 85V 50W |

| CAT3649HV3-GT2 | IC LED DVR QUAD 6CH 16TQFN |

| VJ1206A750JBAAT4X | CAP CER 75PF 50V 5% NP0 1206 |

| GMC49DRAS | CONN EDGECARD 98POS R/A .100 SLD |

| GBC05DRXS-S734 | CONN EDGECARD 10POS DIP .100 SLD |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| EPF6016AQC208-2N | 功能描述:FPGA - 現(xiàn)場可編程門陣列 FPGA - Flex 6000 132 LABs 171 IOs RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 柵極數(shù)量: 邏輯塊數(shù)量:943 內(nèi)嵌式塊RAM - EBR:1956 kbit 輸入/輸出端數(shù)量:128 最大工作頻率:800 MHz 工作電源電壓:1.1 V 最大工作溫度:+ 70 C 安裝風格:SMD/SMT 封裝 / 箱體:FBGA-256 |

| EPF6016AQC208-3 | 功能描述:FPGA - 現(xiàn)場可編程門陣列 FPGA - Flex 6000 132 LABs 171 IOs RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 柵極數(shù)量: 邏輯塊數(shù)量:943 內(nèi)嵌式塊RAM - EBR:1956 kbit 輸入/輸出端數(shù)量:128 最大工作頻率:800 MHz 工作電源電壓:1.1 V 最大工作溫度:+ 70 C 安裝風格:SMD/SMT 封裝 / 箱體:FBGA-256 |

| EPF6016AQC208-3N | 功能描述:FPGA - 現(xiàn)場可編程門陣列 FPGA - Flex 6000 132 LABs 171 IOs RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 柵極數(shù)量: 邏輯塊數(shù)量:943 內(nèi)嵌式塊RAM - EBR:1956 kbit 輸入/輸出端數(shù)量:128 最大工作頻率:800 MHz 工作電源電壓:1.1 V 最大工作溫度:+ 70 C 安裝風格:SMD/SMT 封裝 / 箱體:FBGA-256 |

| EPF6016AQI208-2 | 功能描述:IC FLEX 6000 FPGA 16K 208-PQFP RoHS:否 類別:集成電路 (IC) >> 嵌入式 - FPGA(現(xiàn)場可編程門陣列) 系列:FLEX 6000 產(chǎn)品變化通告:XC4000(E,L) Discontinuation 01/April/2002 標準包裝:24 系列:XC4000E/X LAB/CLB數(shù):100 邏輯元件/單元數(shù):238 RAM 位總計:3200 輸入/輸出數(shù):80 門數(shù):3000 電源電壓:4.5 V ~ 5.5 V 安裝類型:表面貼裝 工作溫度:-40°C ~ 100°C 封裝/外殼:120-BCBGA 供應(yīng)商設(shè)備封裝:120-CPGA(34.55x34.55) |

| EPF6016AQI2083 | 制造商:ALTERA 功能描述:New |

發(fā)布緊急采購,3分鐘左右您將得到回復。