- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄4182 > EPF6024ABI256-2 (Altera)IC FLEX 6000 FPGA 24K 256-BGA PDF資料下載

參數(shù)資料

| 型號(hào): | EPF6024ABI256-2 |

| 廠商: | Altera |

| 文件頁數(shù): | 32/52頁 |

| 文件大小: | 0K |

| 描述: | IC FLEX 6000 FPGA 24K 256-BGA |

| 標(biāo)準(zhǔn)包裝: | 40 |

| 系列: | FLEX 6000 |

| LAB/CLB數(shù): | 196 |

| 邏輯元件/單元數(shù): | 1960 |

| 輸入/輸出數(shù): | 218 |

| 門數(shù): | 24000 |

| 電源電壓: | 3 V ~ 3.6 V |

| 安裝類型: | 表面貼裝 |

| 工作溫度: | -40°C ~ 100°C |

| 封裝/外殼: | 256-BBGA |

| 供應(yīng)商設(shè)備封裝: | 256-BGA(27x27) |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁當(dāng)前第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁

38

Altera Corporation

FLEX 6000 Programmable Logic Device Family Data Sheet

microparameters, which are expressed as worst-case values. Using hand

calculations, these parameters can be used to estimate design

performance. However, before committing designs to silicon, actual

worst-case performance should be modeled using timing simulation and

parameters.

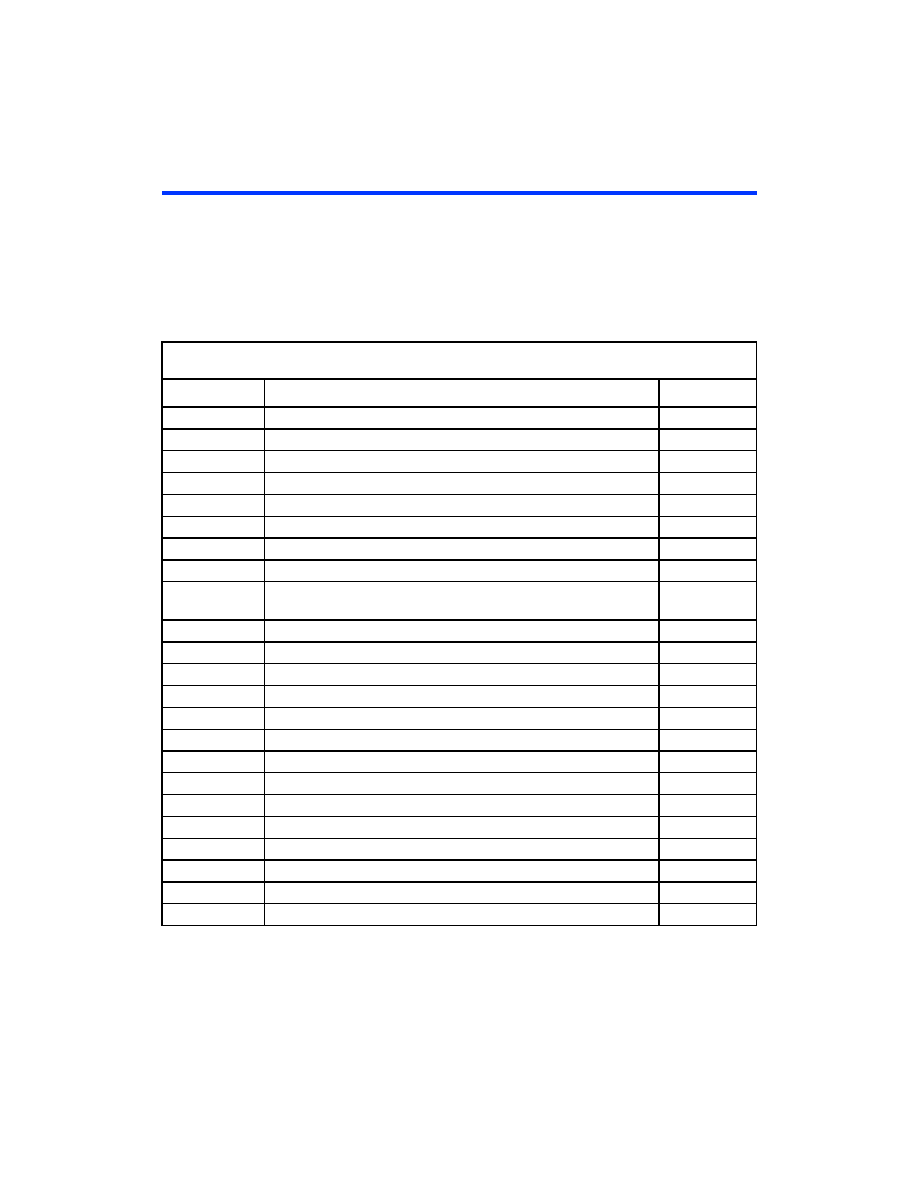

Table 19. LE Timing Microparameters

Symbol

Parameter

Conditions

tREG_TO_REG

LUT delay for LE register feedback in carry chain

tCASC_TO_REG

Cascade-in to register delay

tCARRY_TO_REG

Carry-in to register delay

tDATA_TO_REG

LE input to register delay

tCASC_TO_OUT

Cascade-in to LE output delay

tCARRY_TO_OUT

Carry-in to LE output delay

tDATA_TO_OUT

LE input to LE output delay

tREG_TO_OUT

Register output to LE output delay

tSU

LE register setup time before clock; LE register recovery time after

asynchronous clear

tH

LE register hold time after clock

tCO

LE register clock-to-output delay

tCLR

LE register clear delay

tC

LE register control signal delay

tLD_CLR

Synchronous load or clear delay in counter mode

tCARRY_TO_CARRY Carry-in to carry-out delay

tREG_TO_CARRY

Register output to carry-out delay

tDATA_TO_CARRY

LE input to carry-out delay

tCARRY_TO_CASC

Carry-in to cascade-out delay

tCASC_TO_CASC

Cascade-in to cascade-out delay

tREG_TO_CASC

Register-out to cascade-out delay

tDATA_TO_CASC

LE input to cascade-out delay

tCH

LE register clock high time

tCL

LE register clock low time

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| AMM28DTBT | CONN EDGECARD 56POS R/A .156 SLD |

| EPF6016AQI208-2 | IC FLEX 6000 FPGA 16K 208-PQFP |

| AMM28DTAT | CONN EDGECARD 56POS R/A .156 SLD |

| ABC60DRYI-S734 | CONN EDGECARD 120PS DIP .100 SLD |

| EP20K200FC484-3V | IC APEX 20KE FPGA 200K 484-BGA |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| EPF6024AFC256-1 | 功能描述:FPGA - 現(xiàn)場(chǎng)可編程門陣列 FPGA - Flex 6000 196 LABs 219 IOs RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 柵極數(shù)量: 邏輯塊數(shù)量:943 內(nèi)嵌式塊RAM - EBR:1956 kbit 輸入/輸出端數(shù)量:128 最大工作頻率:800 MHz 工作電源電壓:1.1 V 最大工作溫度:+ 70 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FBGA-256 |

| EPF6024AFC256-2 | 功能描述:FPGA - 現(xiàn)場(chǎng)可編程門陣列 FPGA - Flex 6000 196 LABs 219 IOs RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 柵極數(shù)量: 邏輯塊數(shù)量:943 內(nèi)嵌式塊RAM - EBR:1956 kbit 輸入/輸出端數(shù)量:128 最大工作頻率:800 MHz 工作電源電壓:1.1 V 最大工作溫度:+ 70 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FBGA-256 |

| EPF6024AFC256-2AA | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| EPF6024AFC256-3 | 功能描述:FPGA - 現(xiàn)場(chǎng)可編程門陣列 FPGA - Flex 6000 196 LABs 219 IOs RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 柵極數(shù)量: 邏輯塊數(shù)量:943 內(nèi)嵌式塊RAM - EBR:1956 kbit 輸入/輸出端數(shù)量:128 最大工作頻率:800 MHz 工作電源電壓:1.1 V 最大工作溫度:+ 70 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FBGA-256 |

| EPF6024AFI256-2 | 功能描述:IC FLEX 6000 FPGA 24K 256-FBGA RoHS:否 類別:集成電路 (IC) >> 嵌入式 - FPGA(現(xiàn)場(chǎng)可編程門陣列) 系列:FLEX 6000 產(chǎn)品變化通告:XC4000(E,L) Discontinuation 01/April/2002 標(biāo)準(zhǔn)包裝:24 系列:XC4000E/X LAB/CLB數(shù):100 邏輯元件/單元數(shù):238 RAM 位總計(jì):3200 輸入/輸出數(shù):80 門數(shù):3000 電源電壓:4.5 V ~ 5.5 V 安裝類型:表面貼裝 工作溫度:-40°C ~ 100°C 封裝/外殼:120-BCBGA 供應(yīng)商設(shè)備封裝:120-CPGA(34.55x34.55) |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。