- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄22145 > EPM7192EGI160-20 (Altera)IC MAX 7000 CPLD 192 160-PGA PDF資料下載

參數(shù)資料

| 型號(hào): | EPM7192EGI160-20 |

| 廠商: | Altera |

| 文件頁(yè)數(shù): | 22/66頁(yè) |

| 文件大小: | 0K |

| 描述: | IC MAX 7000 CPLD 192 160-PGA |

| 標(biāo)準(zhǔn)包裝: | 21 |

| 系列: | MAX® 7000 |

| 可編程類型: | 系統(tǒng)內(nèi)可編程 |

| 最大延遲時(shí)間 tpd(1): | 20.0ns |

| 電壓電源 - 內(nèi)部: | 4.5 V ~ 5.5 V |

| 邏輯元件/邏輯塊數(shù)目: | 12 |

| 宏單元數(shù): | 192 |

| 門數(shù): | 3750 |

| 輸入/輸出數(shù): | 124 |

| 工作溫度: | -40°C ~ 85°C |

| 安裝類型: | 表面貼裝 |

| 封裝/外殼: | 160-BBGA |

| 供應(yīng)商設(shè)備封裝: | 160-PBGA(39.6x39.6) |

| 包裝: | 托盤 |

| 產(chǎn)品目錄頁(yè)面: | 604 (CN2011-ZH PDF) |

| 其它名稱: | 544-2341 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)當(dāng)前第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)

Altera Corporation

29

MAX 7000 Programmable Logic Device Family Data Sheet

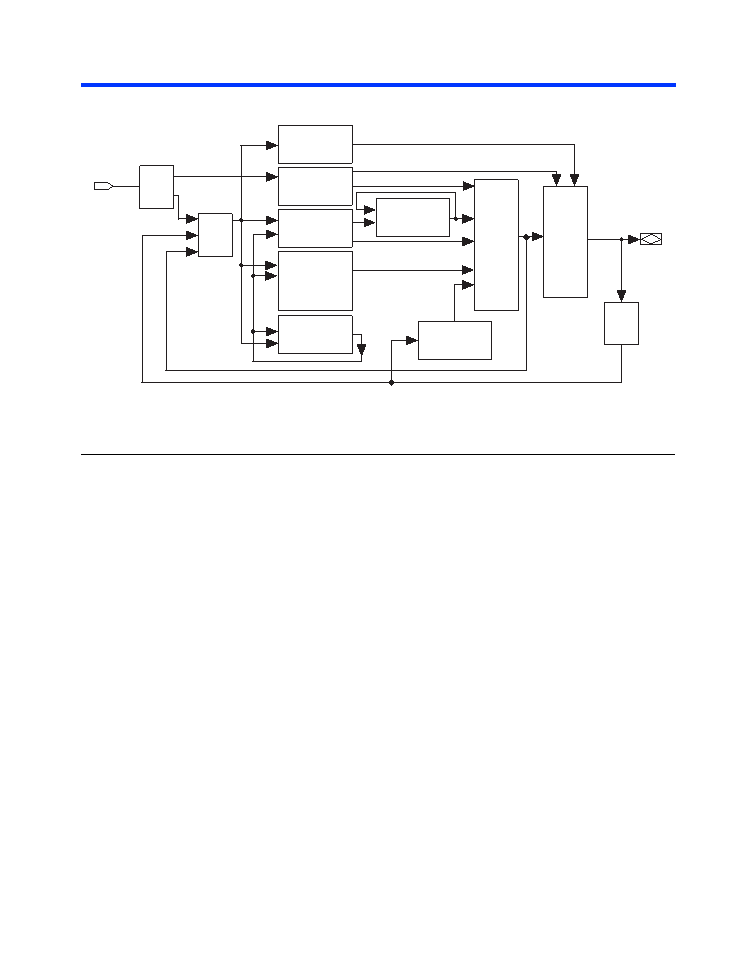

Figure 12. MAX 7000 Timing Model

Notes:

(1)

Only available in MAX 7000E and MAX 7000S devices.

(2)

Not available in 44-pin devices.

The timing characteristics of any signal path can be derived from the

timing model and parameters of a particular device. External timing

parameters, which represent pin-to-pin timing delays, can be calculated

as the sum of internal parameters. Figure 13 shows the internal timing

relationship of internal and external delay parameters.

f For more infomration, see Application Note 94 (Understanding MAX 7000

Logic Array

Delay

t LAD

Output

Delay

t OD3

t OD2

t OD1

t XZ

Z

t X1

t ZX2

t ZX3

Input

Delay

t IN

Register

Delay

t SU

t H

t PRE

t CLR

t RD

t COMB

t FSU

t FH

PIA

Delay

t PIA

Shared

Expander Delay

t SEXP

Register

Control Delay

t LAC

t IC

t EN

I/O

Delay

t IO

Global Control

Delay

t GLOB

Internal Output

Enable Delay

t IOE

Parallel

Expander Delay

t PEXP

Fast

Input Delay

t FIN

(1)

(2)

(1)

(2)

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| VI-2WL-CY-F1 | CONVERTER MOD DC/DC 28V 50W |

| EPM7512AEQC208-7N | IC MAX 7000 CPLD 512 208-PQFP |

| VI-2WJ-CY-F4 | CONVERTER MOD DC/DC 36V 50W |

| EPM7512AEQC208-7 | IC MAX 7000 CPLD 512 208-PQFP |

| TAJA156M004RNJ | CAP TANT 15UF 4V 20% 1206 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| EPM7192EGI160-7 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Electrically-Erasable Complex PLD |

| EPM7192EQC160-10 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Electrically-Erasable Complex PLD |

| EPM7192EQC16012 | 制造商:ALTERA 功能描述:* 制造商:Altera Corporation 功能描述: |

| EPM7192EQC160-12 | 功能描述:CPLD - 復(fù)雜可編程邏輯器件 CPLD - MAX 7000 192 Macro 124 IOs RoHS:否 制造商:Lattice 系列: 存儲(chǔ)類型:EEPROM 大電池?cái)?shù)量:128 最大工作頻率:333 MHz 延遲時(shí)間:2.7 ns 可編程輸入/輸出端數(shù)量:64 工作電源電壓:3.3 V 最大工作溫度:+ 90 C 最小工作溫度:0 C 封裝 / 箱體:TQFP-100 |

| EPM7192EQC160-15 | 功能描述:CPLD - 復(fù)雜可編程邏輯器件 CPLD - MAX 7000 192 Macro 124 IOs RoHS:否 制造商:Lattice 系列: 存儲(chǔ)類型:EEPROM 大電池?cái)?shù)量:128 最大工作頻率:333 MHz 延遲時(shí)間:2.7 ns 可編程輸入/輸出端數(shù)量:64 工作電源電壓:3.3 V 最大工作溫度:+ 90 C 最小工作溫度:0 C 封裝 / 箱體:TQFP-100 |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。