- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄19509 > EPM7512AEQI208-10 (Altera)IC MAX 7000 CPLD 512 208-PQFP PDF資料下載

參數(shù)資料

| 型號(hào): | EPM7512AEQI208-10 |

| 廠商: | Altera |

| 文件頁(yè)數(shù): | 13/64頁(yè) |

| 文件大小: | 0K |

| 描述: | IC MAX 7000 CPLD 512 208-PQFP |

| 標(biāo)準(zhǔn)包裝: | 72 |

| 系列: | MAX® 7000A |

| 可編程類型: | 系統(tǒng)內(nèi)可編程 |

| 最大延遲時(shí)間 tpd(1): | 10.0ns |

| 電壓電源 - 內(nèi)部: | 3 V ~ 3.6 V |

| 邏輯元件/邏輯塊數(shù)目: | 32 |

| 宏單元數(shù): | 512 |

| 門數(shù): | 10000 |

| 輸入/輸出數(shù): | 176 |

| 工作溫度: | -40°C ~ 85°C |

| 安裝類型: | 表面貼裝 |

| 封裝/外殼: | 208-BFQFP |

| 供應(yīng)商設(shè)備封裝: | 208-PQFP(28x28) |

| 包裝: | 托盤 |

| 其它名稱: | 544-2072 EPM7512AEQI208-10-ND |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)當(dāng)前第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)

20

Altera Corporation

MAX 7000A Programmable Logic Device Data Sheet

Note to tables:

(1)

EPM7128A and EPM7256A devices can only be programmed with an adaptive algorithm; users programming these

two devices on platforms that cannot use an adaptive algorithm should use EPM7128AE and EPM7256AE devices.

Programming

with External

Hardware

MAX 7000A devices can be programmed on Windows-based PCs with an

Altera Logic Programmer card, the MPU, and the appropriate device

adapter. The MPU performs continuity checks to ensure adequate

electrical contact between the adapter and the device.

f For more information, see the Altera Programming Hardware Data Sheet.

The Altera software can use text- or waveform-format test vectors created

with the Altera Text Editor or Waveform Editor to test the programmed

device. For added design verification, designers can perform functional

testing to compare the functional device behavior with the results of

simulation.

Data I/O, BP Microsystems, and other programming hardware

manufacturers provide programming support for Altera devices.

f For more information, see Programming Hardware Manufacturers.

IEEE Std.

1149.1 (JTAG)

Boundary-Scan

Support

MAX 7000A devices include the JTAG BST circuitry defined by IEEE Std.

1149.1. Table 8 describes the JTAG instructions supported by MAX 7000A

devices. The pin-out tables, available from the Altera web site

(http://www.altera.com), show the location of the JTAG control pins for

each device. If the JTAG interface is not required, the JTAG pins are

available as user I/O pins.

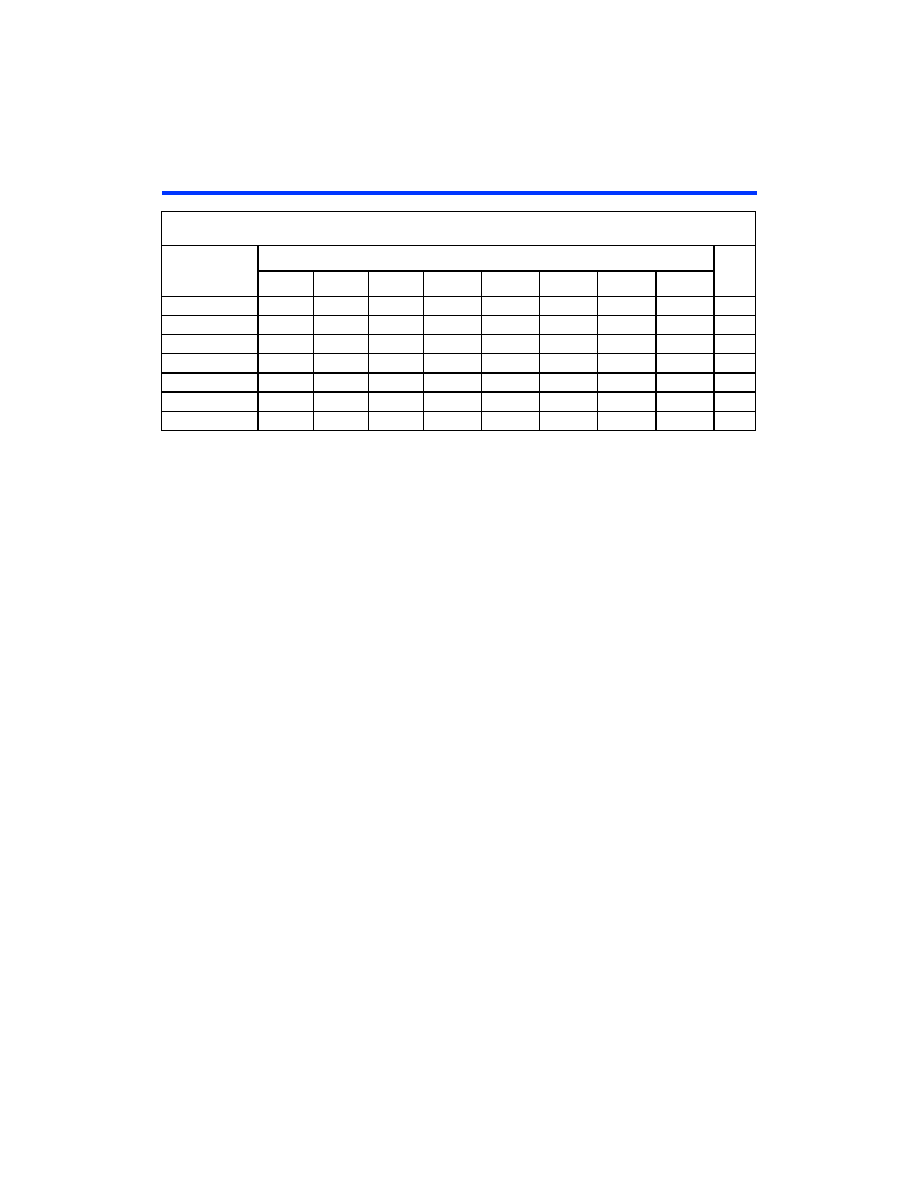

Table 7. MAX 7000A Stand-Alone Verification Times for Different Test Clock Frequencies

Device

fTCK

Units

10 MHz

5 MHz

2 MHz

1 MHz

500 kHz

200 kHz

100 kHz

50 kHz

EPM7032AE

0.00

0.01

0.02

0.04

0.09

0.18

0.36

s

EPM7064AE

0.01

0.02

0.04

0.07

0.18

0.35

0.70

s

EPM7128AE

0.01

0.02

0.04

0.07

0.14

0.34

0.68

1.36

s

EPM7256AE

0.02

0.03

0.08

0.15

0.30

0.75

1.49

2.98

s

EPM7512AE

0.03

0.06

0.15

0.30

0.60

1.49

2.97

5.94

s

EPM7128A (1)

0.08

0.14

0.29

0.56

1.09

2.67

5.31

10.59

s

EPM7256A (1)

0.13

0.24

0.54

1.06

2.08

5.15

10.27

20.51

s

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| EBM06DSUH | CONN EDGECARD 12POS DIP .156 SLD |

| VI-B4N-CY-F3 | CONVERTER MOD DC/DC 18.5V 50W |

| EPM7512AEBC256-10 | IC MAX 7000 CPLD 512 256-BGA |

| 1-745498-7 | CONN D-SUB PLUG 37P 22-26AWG AU |

| AP1122EG-U | IC REG LDO 1.2V 1A SOT223 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| EPM7512AEQI208-10N | 功能描述:CPLD - 復(fù)雜可編程邏輯器件 CPLD - MAX 7000 512 Macro 176 IOs RoHS:否 制造商:Lattice 系列: 存儲(chǔ)類型:EEPROM 大電池?cái)?shù)量:128 最大工作頻率:333 MHz 延遲時(shí)間:2.7 ns 可編程輸入/輸出端數(shù)量:64 工作電源電壓:3.3 V 最大工作溫度:+ 90 C 最小工作溫度:0 C 封裝 / 箱體:TQFP-100 |

| EPM7512AETC100-10 | 制造商:ALTERA 制造商全稱:Altera Corporation 功能描述:High-performance 3.3-V EEPROM-based programmable logic devices (PLDs) built on second-generation Multiple Array MatriX |

| EPM7512AETC14410 | 制造商:Altera Corporation 功能描述: |

| EPM7512AETC144-10 | 功能描述:CPLD - 復(fù)雜可編程邏輯器件 CPLD - MAX 7000 512 Macro 36 IOs RoHS:否 制造商:Lattice 系列: 存儲(chǔ)類型:EEPROM 大電池?cái)?shù)量:128 最大工作頻率:333 MHz 延遲時(shí)間:2.7 ns 可編程輸入/輸出端數(shù)量:64 工作電源電壓:3.3 V 最大工作溫度:+ 90 C 最小工作溫度:0 C 封裝 / 箱體:TQFP-100 |

| EPM7512AETC144-10N | 功能描述:CPLD - 復(fù)雜可編程邏輯器件 CPLD - MAX 7000 512 Macro 36 IOs RoHS:否 制造商:Lattice 系列: 存儲(chǔ)類型:EEPROM 大電池?cái)?shù)量:128 最大工作頻率:333 MHz 延遲時(shí)間:2.7 ns 可編程輸入/輸出端數(shù)量:64 工作電源電壓:3.3 V 最大工作溫度:+ 90 C 最小工作溫度:0 C 封裝 / 箱體:TQFP-100 |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。