- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄67429 > FD7745TE-FREQ-T500 (PLETRONICS INC) CRYSTAL OSCILLATOR, CLOCK, 12 MHz - 32 MHz, LVCMOS OUTPUT PDF資料下載

參數(shù)資料

| 型號: | FD7745TE-FREQ-T500 |

| 廠商: | PLETRONICS INC |

| 元件分類: | XO, clock |

| 英文描述: | CRYSTAL OSCILLATOR, CLOCK, 12 MHz - 32 MHz, LVCMOS OUTPUT |

| 封裝: | ROHS COMPLIANT, CERAMIC, LCC-14 |

| 文件頁數(shù): | 6/12頁 |

| 文件大小: | 185K |

| 代理商: | FD7745TE-FREQ-T500 |

FD77T Series Multi-Output

CMOS Clock Oscillator

February 2008

www.pletronics.com

425-776-1880

3

Three programmable control inputs, S0, S1 and S2, may be used to control various aspects of FD77T

operation including selection of alternative frequency set(s), selection of SSC functionality, output tri-state

and power-down.

Reference Oscillator

The Reference Oscillator is an AT cut quartz crystal based oscillator. This oscillator is very similar to the

Pletronics SM77xxH product oscillator. This signal is the lowest jitter and can be an output on Out1, Out2

or Out3 and can be divided down by the Divider #1. The user may specify any frequency between 12MHz

and 32MHz for this reference. All output frequencies are derived from (referenced to) this Reference

Oscillator.

Reference Oscillator - VCXO

The reference oscillator frequency can be modulated by the Vcontrol input, if the VCXO option is selected.

As this Reference Signal is the reference for all other parts of this circuit, all PLLs will be modulated also.

PLL Multipliers

There are 4 each independent PLL Multipliers and these can multiply the Reference Oscillator frequency

from 1 (bypass mode) to any value that is <=230MHz (the lowest frequency is the Reference Oscillator

frequency).

Each of the PLL Multipliers can have two setup options, 0 or 1, depending on which option is chosen and

set by the Sx control signals and the user’s definitions are stored in eePROM.

Spread Spectrum

Each PLL has its individual Spread Spectrum (SS) function that can be enabled. This permits the

modulation of the output frequency by a user-set amount. The modulation can be centered on the output

frequency or down side only. Which of the 1 of 8 SS settings is being used is set by the Sx input and the

user definition. The value is a percentage of the output frequency that will be modulated.

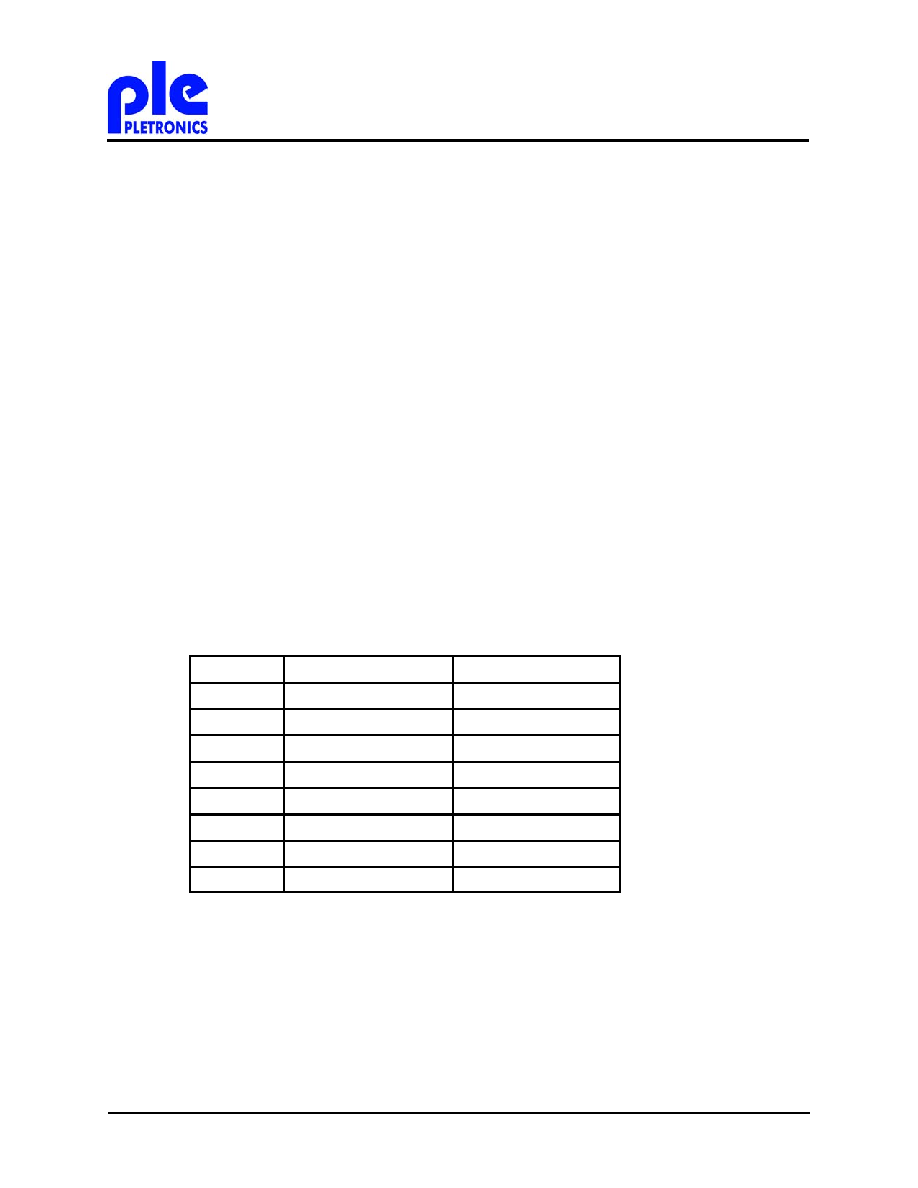

SS Option

Down Side Modulation

Centered Modulation

0

No SS

1

-0.25%

+

_0.25%

2

-0.50%

+

_0.50%

3

-0.75%

+

_0.75%

4

-1.00%

+

_1.00%

5

-1.25%

+

_1.25%

6

-1.50%

+

_1.50%

7

-2.00%

+

_2.00%

Divider Section

The dividers operate on the output of the PLLs. There are two dividers on each PLL that divide by 1

through 127, the value is user defined. There is only 1 setting allowed per divider. These are not set by the

Sx input state.

The dividers add very little jitter to the output signals.

Multiplexers

MUX #1 selects the input to the Divider #1, this can be the reference oscillator signal or the output from

PLL Multiplier #1. MUX #2 through MUX #7 connect various divider outputs to the output buffers.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| FD7744T-FREQ-T250 | CRYSTAL OSCILLATOR, CLOCK, 12 MHz - 32 MHz, LVCMOS OUTPUT |

| FD7745T-FREQ-T250 | CRYSTAL OSCILLATOR, CLOCK, 12 MHz - 32 MHz, LVCMOS OUTPUT |

| FE020C | 1-OUTPUT 20 W DC-DC REG PWR SUPPLY MODULE |

| FE020A | 1-OUTPUT 20 W DC-DC REG PWR SUPPLY MODULE |

| FE020B | 1-OUTPUT 20 W DC-DC REG PWR SUPPLY MODULE |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| FD7745TL-25.0M-PLE | 制造商:PLETRONICS 制造商全稱:Pletronics, Inc. 功能描述:Multi-Output CMOS Clock Oscillator |

| FD7745TL-25.0M-PLE-1K | 制造商:PLETRONICS 制造商全稱:Pletronics, Inc. 功能描述:Multi-Output CMOS Clock Oscillator |

| FD7745TL-25.0M-PLE-T250 | 制造商:PLETRONICS 制造商全稱:Pletronics, Inc. 功能描述:Multi-Output CMOS Clock Oscillator |

| FD7745TL-25.0M-PLE-T500 | 制造商:PLETRONICS 制造商全稱:Pletronics, Inc. 功能描述:Multi-Output CMOS Clock Oscillator |

| FD7745TLE-25.0M-PLE | 制造商:PLETRONICS 制造商全稱:Pletronics, Inc. 功能描述:Multi-Output CMOS Clock Oscillator |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。