- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄383014 > GS1545-CQR (Electronic Theatre Controls, Inc.) HDTV Serial Digital Equalizing Receiver PDF資料下載

參數(shù)資料

| 型號: | GS1545-CQR |

| 廠商: | Electronic Theatre Controls, Inc. |

| 英文描述: | HDTV Serial Digital Equalizing Receiver |

| 中文描述: | 串行數(shù)字高清晰度電視接收機(jī)均等 |

| 文件頁數(shù): | 8/19頁 |

| 文件大小: | 198K |

| 代理商: | GS1545-CQR |

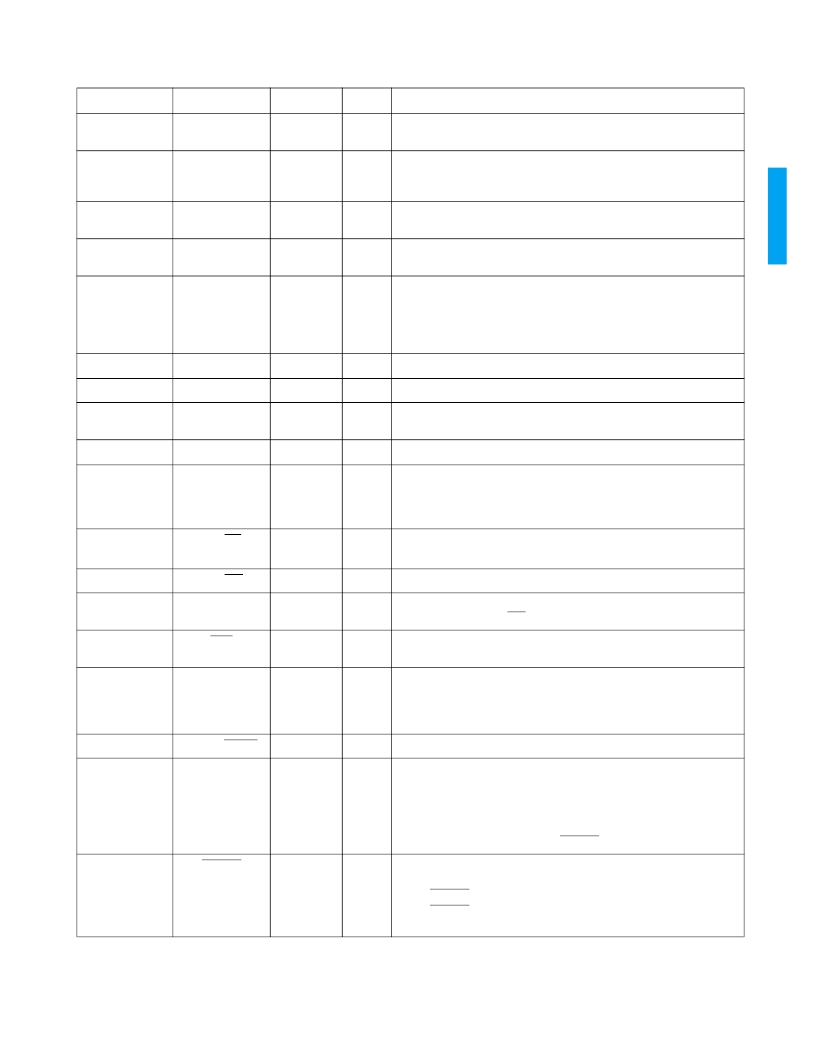

GENNUM CORPORATION

522 - 28 - 00

8

G

32, 33

SP_V

EE

Power

Input

Negative Supply

. Most negative power supply connection for the

parallel output stage.

34

PCLK_OUT

TTL

Output

Output Clock.

The device uses PCLK_OUT for clocking the output

data stream from DATA_OUT[19:0]. This clock is also used to clock

the data into the GS1500 HDTV Deformatter or GS1510 Deformatter.

35

PCLK_V

CC

Power

Input

Positive Supply.

Most positive supply connection for parallel clock

output stage.

36

PCLK_V

EE

Power

Input

Negative Supply.

Most negative power supply connection for parallel

clock output stage.

41, 42, 43, 44,

45, 46, 47, 48,

49, 50, 53, 54,

55, 56, 59, 60,

61, 62, 63, 64

DATA_OUT[19:0]

TTL

Output

Parallel Data Output Bus.

The device outputs a 20 bit parallel data

stream running at 74.25 or 74.25/1.001MHz on DATA_OUT[19:0].

DATA_OUT[19] is the MSB and DATA_OUT[0] is the LSB.

72

LFA_V

CC

Power

Input

Positive Supply

. Loop filter most positive power supply connection.

73

LFA

Analog

Output

Control Signal Output.

Control voltage for GO1515 VCO.

74

LBCONT

Analog

Input

Control Signal Input

. Used to provide electronic control of Loop

Bandwidth.

75

LFA_V

EE

Power

Input

Negative Supply

. Loop filter most negative power supply connection.

76

DFT_V

EE

Power

Input

Most negative power supply connection - enables the jitter

demodulator functionality. This pin should be connected to ground. If

left floating, the DM function is disabled resulting in a current saving of

340μA.

79, 80

DM, DM

Analog

Output

Test Signal

. Used for manufacturing test only.

These pins must be floating for normal operation.

81, 85

LFS, LFS

Analog

Input

Loop Filter Connections

.

86

IJI

Analog

Output

Status Signal Output

. Approximates the amount of excessive jitter on

the incoming DDI and DDI input.

89

VCO

Analog

Input

Control Signal Input

. Input pin is AC coupled to ground using a 50

transmission line.

91

VCO

Analog

Input

Control Signal Input.

Voltage controlled oscillator input. This pin is

connected to the output pin of the GO1515 VCO.

This pin must be connected to the GO1515 VCO output pin via a 50

transmission line.

93, 96

PLCAP, PLCAP

Analog

Input

Control Signal Input

. Phase lock detect time constant capacitor.

98

PLL_LOCK

TTL

Output

Status Indicator Signal

. This signal is a combination (logical AND) of

the carrier detect and phase lock signals.

When input is present and PLL is locked, the PLL_LOCK goes high

and the outputs are valid. When the PLL_LOCK output is low the data

output is muted (latched at the last state).

PLL_LOCK is independent of the BYPASS signal.

105

BYPASS

TTL

Input

Control Signal Input

. Selectable input that controls whether the input

signal is reclocked or passed through the chip.

When BYPASS is high; the input signal is reclocked.

When BYPASS is low; the input signal is passed through the chip and

not reclocked. Muting does not effect bypassed signal.

PIN DESCRIPTIONS (Continued)

NUMBER

SYMBOL

LEVEL

TYPE

DESCRIPTION

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| GS1881-IKA | Monolithic Video Sync Separators |

| GS1881-ITA | Monolithic Video Sync Separators |

| GS4881 | Monolithic Video Sync Separators |

| GS4881-CDA | Monolithic Video Sync Separators |

| GS4881-CKA | Monolithic Video Sync Separators |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| GS1545-CQRE3 | 制造商:Semtech Corporation 功能描述:High Performance integrated Equalizing Receiver 128-Pin MQFP 制造商:Semtech Corporation 功能描述:HD Equalizing Receiver |

| GS1550MD-EVK2-S2W-WEB | 制造商:GSC 功能描述:GS1550MD Evaluation Kit Includes the GS1550MD-EVB2-S2W-WEB Evaluation Board |

| GS1559 | 制造商:GENNUM 制造商全稱:GENNUM 功能描述:GS1559 HD-LINX-TM II Multi-Rate Deserializer with Loop-Through Cable Driver |

| GS1559_08 | 制造商:GENNUM 制造商全稱:GENNUM 功能描述:HD-LINX II Multi-Rate Deserializer with Loop-Through Cable Driver |

| GS1559-CB | 制造商:Semtech Corporation 功能描述: 制造商:Semtech Corporation 功能描述:HD/SD/ASI Receiver |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。