- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄370686 > HS9-82C37ARH-Q (INTERSIL CORP) Radiation Hardened CMOS High Performance Programmable DMA Controller PDF資料下載

參數(shù)資料

| 型號: | HS9-82C37ARH-Q |

| 廠商: | INTERSIL CORP |

| 元件分類: | 數(shù)學(xué)處理器 |

| 英文描述: | Radiation Hardened CMOS High Performance Programmable DMA Controller |

| 中文描述: | 4 CHANNEL(S), 5 MHz, DMA CONTROLLER, CDFP42 |

| 封裝: | METAL SEALED, CERAMIC, DFP-42 |

| 文件頁數(shù): | 6/28頁 |

| 文件大小: | 253K |

| 代理商: | HS9-82C37ARH-Q |

第1頁第2頁第3頁第4頁第5頁當前第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁

6

Specifications HS-82C37ARH

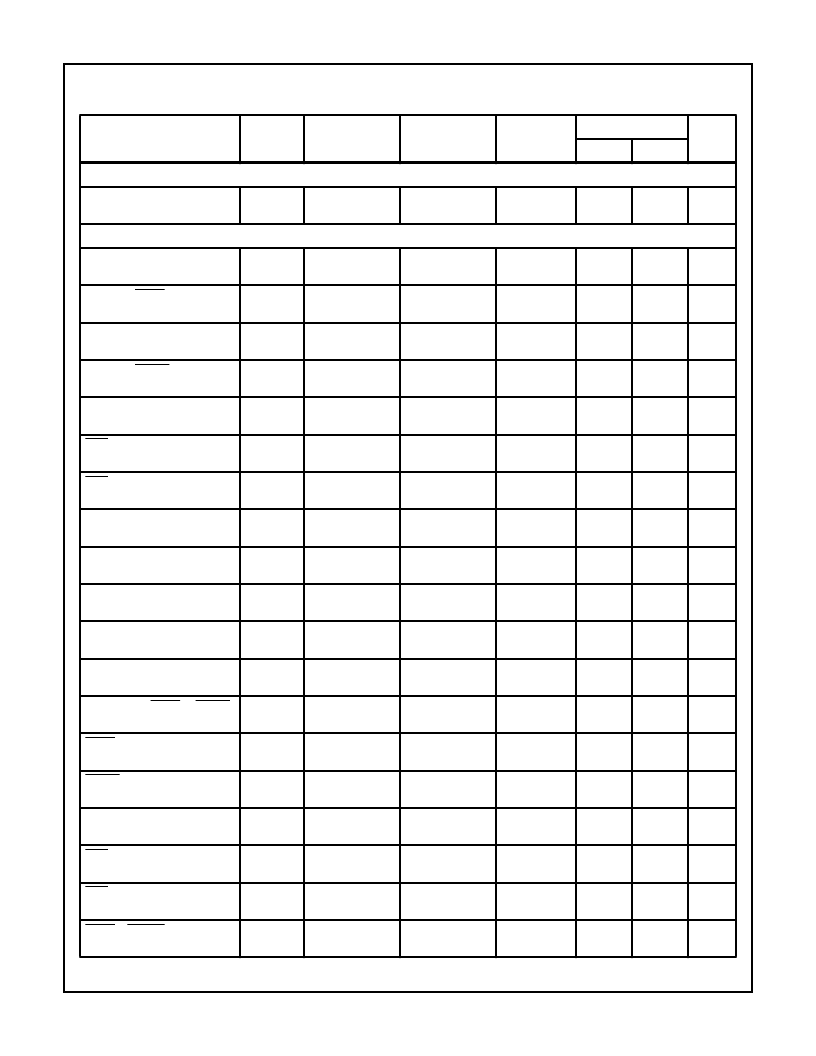

TABLE 2. AC ELECTRICAL PERFORMANCE CHARACTERISTICS

VCC = +5V

±

10%, GND = 0V, AC’s Tested at Worst Case VDD, Guaranteed Over Full Operating Range.

PARAMETER

SYMBOL

(NOTES 1, 2)

CONDITIONS

TEMPERATURE

SUBGROUP

LIMITS

UNITS

MIN

MAX

DMA (MASTER) MODE

AEN HIGH from CLK LOW (S1)

Delay Time

TCLAEH

VDD = 4.5V

+25

o

C, +125

o

C,

-55

o

C

9, 10, 11

175

ns

DMA (MASTER) MODE (Continued)

AEN LOW from CLK HIGH (SI)

Delay Time

TCHAEL

VDD = 4.5V

+25

o

C, +125

o

C,

-55

o

C

9, 10, 11

-

130

ns

ADR from READ HIGH Hold

Time

TRHAX

VDD = 4.5V

+25

o

C, +125

o

C,

-55

o

C

9, 10, 11

TCLCL-

100

-

ns

DB from ADSTB LOW Hold

Time

TSLDZ

VDD = 4.5V

+25

o

C, +125

o

C,

-55

o

C

9, 10, 11

TCLCH-

18

-

ns

ADR from WRITE HIGH Hold

Time

TWHAX

VDD = 4.5V

+25

o

C, +125

o

C,

-55

o

C

9, 10, 11

TCLCL-

50

-

ns

DACK Valid from CLK LOW

Delay Time

TCLDAV

VDD = 4.5V

+25

o

C, +125

o

C,

-55

o

C

9, 10, 11

-

170

ns

EOP HIGH from CLK HIGH

Delay Time

TCHIPH

VDD = 4.5V

+25

o

C, +125

o

C,

-55

o

C

9, 10, 11

-

170

ns

EOP LOW from CLK HIGH

Delay Time

TCHIPL

VDD = 4.5V

+25

o

C, +125

o

C,

-55

o

C

9, 10, 11

-

100

ns

ADR Stable from CLK HIGH

TCHAV

VDD = 4.5V

+25

o

C, +125

o

C,

-55

o

C

9, 10, 11

-

110

ns

DB to ADSTB LOW Setup Time

TDVSL

VDD = 4.5V

+25

o

C, +125

o

C,

-55

o

C

9, 10, 11

TCHCL

+10

-

ns

Clock HIGH Time

(Transitions 10ns)

TCHCL

VDD = 4.5V

+25

o

C, +125

o

C,

-55

o

C

9, 10, 11

70

-

ns

Clock LOW Time

(Transitions 10ns)

TCLCH

VDD = 4.5V

+25

o

C, +125

o

C,

-55

o

C

9, 10, 11

50

-

ns

CLK Cycle Time

TCLCL

VDD = 4.5V

+25

o

C, +125

o

C,

-55

o

C

9, 10, 11

200

-

ns

CLK HIGH to READ or WRITE

LOW Delay

TCHRWL

VDD = 4.5V

+25

o

C, +125

o

C,

-55

o

C

9, 10, 11

-

190

ns

READ HIGH from CLK HIGH

(S4) Delay Time

TCHRH

VDD = 4.5V

+25

o

C, +125

o

C,

-55

o

C

9, 10, 11

-

190

ns

WRITE HIGH from CLK HIGH

(S4) Delay Time

TCHWH

VDD = 4.5V

+25

o

C, +125

o

C,

-55

o

C

9, 10, 11

-

130

ns

HRQ Valid from CLK HIGH

Delay Time

TCHRQV

VDD = 4.5V

+25

o

C, +125

o

C,

-55

o

C

9, 10, 11

-

120

ns

EOP LOW to CLK LOW Setup

Time

TEPLCL

VDD = 4.5V

+25

o

C, +125

o

C,

-55

o

C

9, 10, 11

40

-

ns

EOP Pulse Width

TEPLEPH

VDD = 4.5V

+25

o

C, +125

o

C,

-55

o

C

9, 10, 11

220

-

ns

READ or WRITE Active from

CLK HIGH

TCHRWV

VDD = 4.5V

+25

o

C, +125

o

C,

-55

o

C

9, 10, 11

-

150

ns

Spec Number

518058

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| HS1-82C37ARH-8 | Radiation Hardened CMOS High Performance Programmable DMA Controller |

| HS9-82C37ARH-8 | Circular Connector; No. of Contacts:8; Series:; Body Material:Aluminum Alloy; Connecting Termination:Solder; Connector Shell Size:20; Circular Contact Gender:Socket; Circular Shell Style:Wall Mount Receptacle RoHS Compliant: No |

| HS9-82C37ARH | Radiation Hardened CMOS High Performance Programmable DMA Controller |

| HS9-9808RH | Converter IC |

| HS1-9808RH | Converter IC |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| HS9-82C54RH | 制造商:INTERSIL 制造商全稱:Intersil Corporation 功能描述:Radiation Hardened CMOS Programmable Interval Timer |

| HS9-82C54RH-8 | 制造商:Intersil Corporation 功能描述:PROGRAMMABLE TIMER SGL 24PIN CFLATPACK - Bulk |

| HS9-82C54RH-Q | 制造商:Intersil Corporation 功能描述:PROGRAMMABLE TIMER SGL 24CFPAK - Bulk |

| HS9-82C85RH | 制造商:INTERSIL 制造商全稱:Intersil Corporation 功能描述:Radiation Hardened CMOS Static Clock Controller/Generator |

| HS9-82C85RH/PROTO | 制造商:INTERSIL 制造商全稱:Intersil Corporation 功能描述:Radiation Hardened CMOS Static Clock Controller/Generator |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。