- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄17028 > HW-V5-PCIE2-UNI-G (Xilinx Inc)KIT DEV PCIEXPRESS GTX VIRTEX5 PDF資料下載

參數(shù)資料

| 型號: | HW-V5-PCIE2-UNI-G |

| 廠商: | Xilinx Inc |

| 文件頁數(shù): | 9/91頁 |

| 文件大?。?/td> | 0K |

| 描述: | KIT DEV PCIEXPRESS GTX VIRTEX5 |

| 產(chǎn)品培訓模塊: | PCI Express and Virtex® -5 FPGAs |

| 標準包裝: | 1 |

| 系列: | Virtex® -5 |

| 類型: | FPGA |

| 適用于相關產(chǎn)品: | Virtex?-5 FPGA |

| 所含物品: | 板,CD |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁當前第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁

Virtex-5 FPGA Data Sheet: DC and Switching Characteristics

DS202 (v5.3) May 5, 2010

Product Specification

17

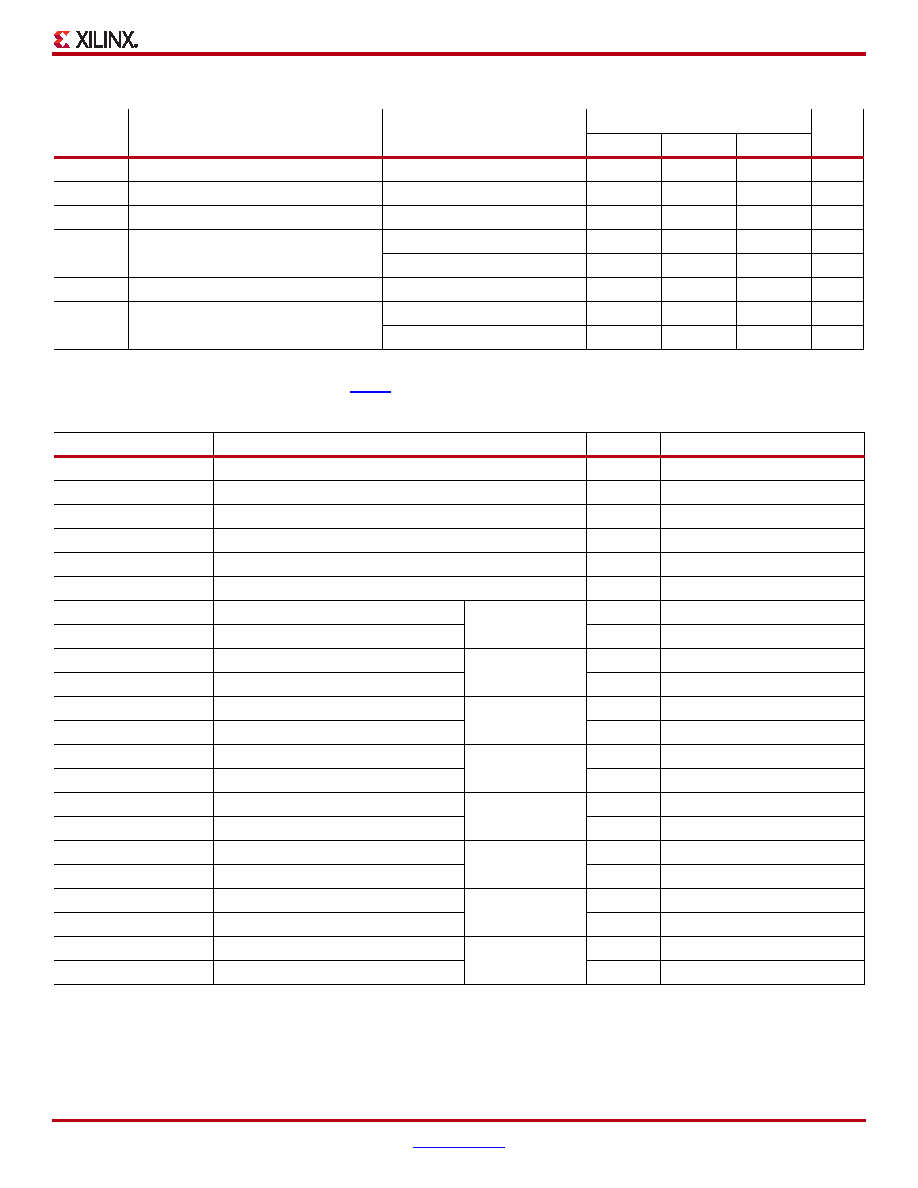

Table 33: GTP_DUAL Tile User Clock Switching Characteristics(1)

Symbol

Description

Conditions

Speed Grade

Units

-3

-2

-1

FTXOUT

TXOUTCLK maximum frequency

375

320

MHz

FRXREC

RXRECCLK maximum frequency

375

320

MHz

TRX

RXUSRCLK maximum frequency

375

320

MHz

TRX2

RXUSRCLK2 maximum frequency

RXDATAWIDTH = 0

350

320

MHz

RXDATAWIDTH = 1

187.5

160

MHz

TTX

TXUSRCLK maximum frequency

375

320

MHz

TTX2

TXUSRCLK2 maximum frequency

TXDATAWIDTH = 0

350

320

MHz

TXDATAWIDTH = 1

187.5

160

MHz

Notes:

1.

Clocking must be implemented as described in UG196: Virtex-5 FPGA RocketIO GTP Transceiver User Guide

Table 34: GTP_DUAL Tile Transmitter Switching Characteristics

Symbol

Description

Min

Typ

Max

Units

FGTPTX

Serial data rate range

0.1

FGTPMAX

Gb/s

TRTX

TX Rise time

140

ps

TFTX

TX Fall time

120

ps

TLLSKEW

TX lane-to-lane skew(1)

855

ps

VTXOOBVDPP

Electrical idle amplitude

20

mV

TTXOOBTRANS

Electrical idle transition time

40

ns

TJ3.75

Total Jitter(2)

3.75 Gb/s

0.35

UI

DJ3.75

Deterministic Jitter(2)

0.19

UI

TJ3.2

Total Jitter(2)

3.20 Gb/s

0.35

UI

DJ3.2

Deterministic Jitter(2)

0.19

UI

TJ2.5

Total Jitter(2)

2.50 Gb/s

0.30

UI

DJ2.5

Deterministic Jitter(2)

0.14

UI

TJ2.0

Total Jitter(2)

2.00 Gb/s

0.30

UI

DJ2.0

Deterministic Jitter(2)

0.14

UI

TJ1.25

Total Jitter(2)

1.25 Gb/s

0.20

UI

DJ1.25

Deterministic Jitter(2)

0.10

UI

TJ1.00

Total Jitter(2)

1.00 Gb/s

0.20

UI

DJ1.00

Deterministic Jitter(2)

0.10

UI

TJ500

Total Jitter(2)

500 Mb/s

0.10

UI

DJ500

Deterministic Jitter(2)

0.04

UI

TJ100

Total Jitter(2)

100 Mb/s

0.02

UI

DJ100

Deterministic Jitter(2)

0.01

UI

Notes:

1.

Using same REFCLK input with TXENPMAPHASEALIGN enabled for up to four consecutive GTP_DUAL sites.

2.

Using PLL_DIVSEL_FB = 2, INTDATAWIDTH = 1.

3.

All jitter values are based on a Bit-Error Ratio of 1e–12.

相關PDF資料 |

PDF描述 |

|---|---|

| CORE1553-SA | HARDWARE FOR IP CORE1553 |

| EBA28DRMS | CONN EDGECARD 56POS .125 SQ WW |

| AMM03DSEN | CONN EDGECARD 6POS .156 EYELET |

| VE-B50-EY | CONVERTER MOD DC/DC 5V 50W |

| STD17W-G | WIRE & CABLE MARKERS |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| HW-VID-KIT | 功能描述:可編程邏輯 IC 開發(fā)工具 Lattice Video Interface Kit RoHS:否 制造商:Altera Corporation 產(chǎn)品:Development Kits 類型:FPGA 工具用于評估:5CEFA7F3 接口類型: 工作電源電壓: |

| HW-VL1 | 制造商:IDEC CORPORATION 功能描述:BARRIER |

| HW-VL2 | 制造商:IDEC Corporation 功能描述:COVER;HW FNGR SAFE CONTAC CVR 制造商:IDEC CORPORATION 功能描述:HW FNGR SAFE CONTAC CVR |

| HW-VL3 | 制造商:IDEC Corporation 功能描述: 制造商:IDEC Corporation 功能描述:Replacs TW-VL3 FNGR SAF |

| HWW-X030T-10015Z-H1 | 制造商:P-TEC 制造商全稱:P-tec Corporation 功能描述:X30T RGB LED Wall Washers |

發(fā)布緊急采購,3分鐘左右您將得到回復。