- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄370806 > HYS72D64020GU-7F-B (INFINEON TECHNOLOGIES AG) RES 1.8K OHM 1/16W 5% 0402 SMD PDF資料下載

參數(shù)資料

| 型號(hào): | HYS72D64020GU-7F-B |

| 廠商: | INFINEON TECHNOLOGIES AG |

| 英文描述: | RES 1.8K OHM 1/16W 5% 0402 SMD |

| 中文描述: | 184引腳緩沖雙列內(nèi)存模組 |

| 文件頁(yè)數(shù): | 24/51頁(yè) |

| 文件大小: | 1356K |

| 代理商: | HYS72D64020GU-7F-B |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)當(dāng)前第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)

HYS[64/72]D[16x01/32x00/64x20][G/E]U-[5/6/7/8]-B

Unbuffered DDR SDRAM Modules

Electrical Characteristics

Data Sheet

24

V1.1, 2003-07

3.3

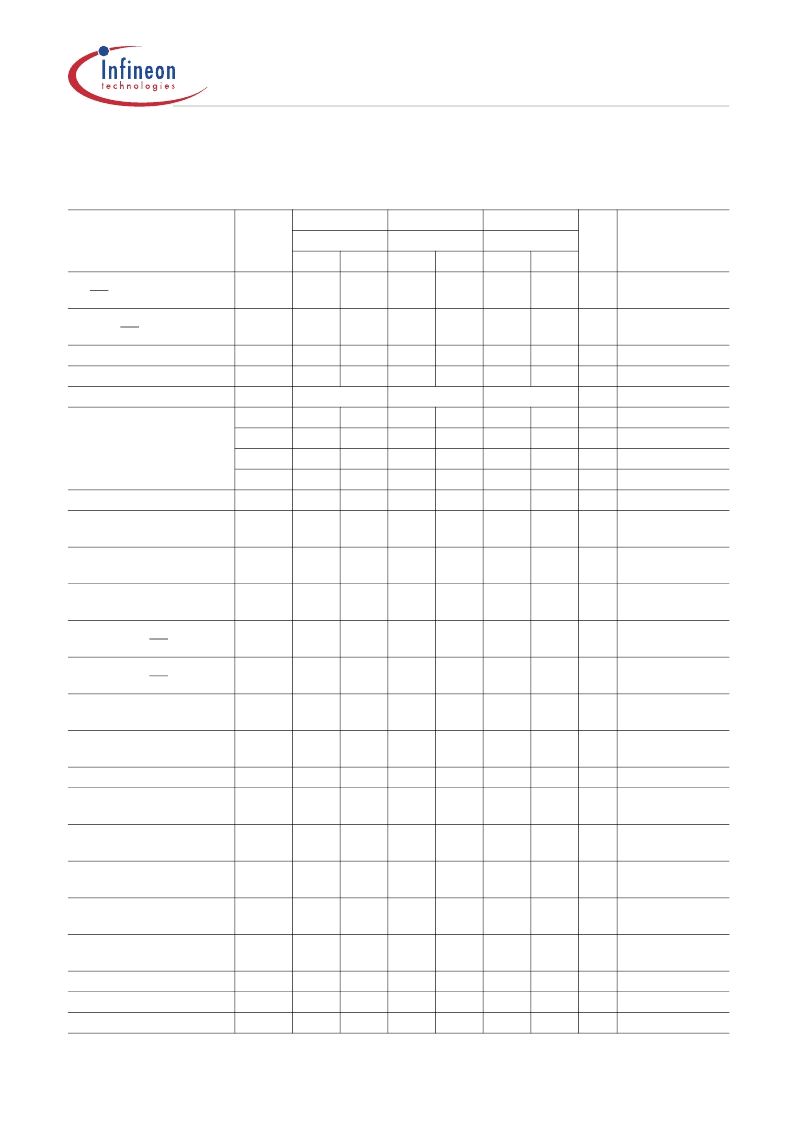

AC Characteristics

Table 15

Parameter

AC Timing - Absolute Specifications –8/–7/–7F

Symbol

–8

–7

–7F

Unit

Note/

Test Condition

1)

DDR200

Min.

–0.8

DDR266A

Min.

–0.75

DDR266

Min.

–0.75

Max.

+0.8

Max.

+0.75

Max.

+0.75

DQ output access time from

CK/CK

DQS output access time

from CK/CK

CK high-level width

CK low-level width

Clock Half Period

Clock cycle time

t

AC

ns

2)3)4)5)

t

DQSCK

–0.8

+0.8

–0.75

+0.75

–0.75

+0.75

ns

2)3)4)5)

t

CH

t

CL

t

HP

t

CK3

t

CK2.5

t

CK2

t

CK1.5

0.45

0.45

min. (

t

CL

,

t

CH

)

8

8

10

10

0.6

0.6

0.55

0.55

0.45

0.45

min. (

t

CL

,

t

CH

)

7

7

7.5

—

0.5

0.5

0.55

0.55

0.45

0.45

min. (

t

CL

,

t

CH

)

7

7

7.5

—

0.5

0.5

0.55

0.55

t

CK

t

CK

ns

ns

ns

ns

ns

ns

ns

2)3)4)5)

2)3)4)5)

2)3)4)5)

12

12

12

12

—

—

12

12

12

—

—

—

12

12

12

—

—

—

CL = 3.0

2)3)4)5)

CL = 2.5

2)3)4)5)

CL = 2.0

2)3)4)5)

CL = 1.5

2)3)4)5)

2)3)4)5)

DQ and DM input hold time

t

DH

DQ and DM input setup

time

Control and Addr. input

pulse width (each input)

DQ and DM input pulse

width (each input)

Data-out high-impedance

time from CK/CK

Data-out low-impedance

time from CK/CK

Write command to 1

st

DQS

latching transition

DQS-DQ skew (DQS and

associated DQ signals)

Data hold skew factor

DQ/DQS output hold time

t

DS

2)3)4)5)

t

IPW

2.5

—

2.2

—

2.2

—

ns

2)3)4)5)6)

t

DIPW

2.0

—

1.75

—

1.75

—

ns

2)3)4)5)6)

t

HZ

–0.8

+0.8

–0.75

+0.75

–0.75

+0.75

ns

2)3)4)5)7)

t

LZ

–0.8

+0.8

–0.75

+0.75

–0.75

+0.75

ns

2)3)4)5)7)

t

DQSS

0.75

1.25

0.75

1.25

0.75

1.25

t

CK

2)3)4)5)

t

DQSQ

—

+0.6

—

+0.5

—

+0.5

ns

2)3)4)5)

t

QHS

t

QH

—

t

HP

–

t

QHS

0.35

1.0

—

—

t

HP

–

t

QHS

0.35

0.75

—

—

t

HP

–

t

QHS

0.35

0.75

—

ns

ns

2)3)4)5)

2)3)4)5)

DQS input low (high) pulse

width (write cycle)

DQS falling edge to CK

setup time (write cycle)

DQS falling edge hold time

from CK (write cycle)

Mode register set command

cycle time

Write preamble setup time

Write postamble

Write preamble

t

DQSL,H

—

—

—

t

CK

2)3)4)5)

t

DSS

0.2

—

0.2

—

0.2

—

t

CK

2)3)4)5)

t

DSH

0.2

—

0.2

—

0.2

—

t

CK

2)3)4)5)

t

MRD

2

—

2

—

2

—

t

CK

2)3)4)5)

t

WPRES

t

WPST

t

WPRE

0

0.40

0.25

—

0.60

—

0

0.40

0.25

—

0.60

—

0

0.40

0.25

—

0.60

—

ns

t

CK

t

CK

2)3)4)5)8)

2)3)4)5)9)

2)3)4)5)

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| HYS64D16301GU-8-B | 184-Pin Unbuffered Dual-In-Line Memory Modules |

| HYS64D32000GU-8-B | 184-Pin Unbuffered Dual-In-Line Memory Modules |

| HYS72D32000GU-8-B | 184-Pin Unbuffered Dual-In-Line Memory Modules |

| HYS64D64020GU-8-B | 184-Pin Unbuffered Dual-In-Line Memory Modules |

| HYS72D64020GU-8-B | 184-Pin Unbuffered Dual-In-Line Memory Modules |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| HYS72D64020GU-8-A | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:?512MB (64Mx72) PC1600 2-bank? |

| HYS72D64020GU-8-B | 制造商:INFINEON 制造商全稱:Infineon Technologies AG 功能描述:184-Pin Unbuffered Dual-In-Line Memory Modules |

| HYS72D64300 | 制造商:QIMONDA 制造商全稱:QIMONDA 功能描述:184-Pin Registered Double Data Rate SDRAM Module |

| HYS72D64300GBR-5-B | 制造商:INFINEON 制造商全稱:Infineon Technologies AG 功能描述:184 - Pin Registered Double Data Rate SDRAM Modules |

| HYS72D64300GBR-5-C | 制造商:INFINEON 制造商全稱:Infineon Technologies AG 功能描述:184-Pin Registered Double Data Rate SDRAM Module |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。