- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄370809 > HYS72T256020GR-37-A (INFINEON TECHNOLOGIES AG) DDR2 Registered Memory Modules PDF資料下載

參數(shù)資料

| 型號: | HYS72T256020GR-37-A |

| 廠商: | INFINEON TECHNOLOGIES AG |

| 英文描述: | DDR2 Registered Memory Modules |

| 中文描述: | 注冊的DDR2內(nèi)存模塊 |

| 文件頁數(shù): | 12/33頁 |

| 文件大小: | 936K |

| 代理商: | HYS72T256020GR-37-A |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁當前第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁

HYS72T[256/128/64][0/2][0/2]0[G/H]R-[5/3.7]-A

Registered DDR2 SDRAM Modules

Data Sheet

Preliminary

12

Rev. 0.85, 2004-04

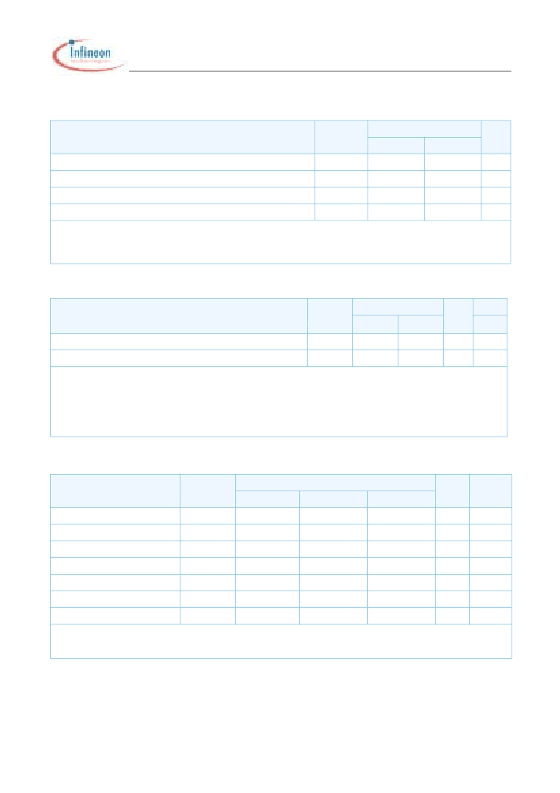

3.0 Absolute Maximum Ratings

3.1 Operating Temperature Range

3.2 Supply Voltage Levels and DC Operating Conditions

Parameter

Symbol

Limit Values

Unit

min.

max.

Voltage on any pins relative to V

SS

Voltage on V

DD

relative to V

SS

Voltage on V

DD Q

relative to V

SS

Storage temperature range

V

IN,

V

OUT

– 0.5

2.3

V

V

DD

– 1.0

2.3

V

V

DDQ

– 0.5

2.3

T

STG

-55

+100

o

C

Stresses greater than those listed under “Absolute Maximum Ratings” may cause permanent damage to the device. This is a

stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational

sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reli-

ability.

Parameter

Symbol

Limit Values

Unit

Notes

min.

max.

DIMM Module Operating Temperature Range (ambient)

TOPR

0

+55

o

C

DRAM Component Case Temperature Range

TCASE

0

+95

o

C

1 - 4

1. DRAM Component Case Temperature is the surface temperature in the center on the top side of any of the DRAMs. For

measurement conditions, please refer to the JEDEC document JESD51-2.

2. Within the DRAM Component Case Temperature range all DRAM specification will be supported.

3. Above 85

o

C DRAM case temperature the Auto-Refresh command interval has to be reduced to tREFI = 3.9 μs.

4. Self-Refresh period is hard-coded in the DRAMs and therefore it is imperative that the system ensures the DRAM is below

85

o

C case temperature before initiating self-refresh operation.

Parameter

Symbol

Limit Values

Unit

Notes

min.

nom.

max.

Device Supply Voltage

V

DD

1.7

1.8

1.9

V

-

Output Supply Voltage

V

DDQ

1.7

1.8

1.9

V

1)

Input Reference Voltage

V

REF

0.49 x

V

DDQ

1.7

0.5 x

V

DDQ

–

0.51 x

V

DDQ

3.6

V

2)

EEPROM Supply Voltage

V

DDSPD

V

DC Input Logic High

V

IH (DC)

V

REF

+ 0.125

– 0.30

–

V

DDQ

+ 0.3

V

REF

– 0.125

5

V

DC Input Logic Low

V

IL (DC)

–

V

In / Output Leakage Current

I

L

– 5

–

μ

A

3)

1

2

3

Under all conditions,

V

must be less than or equal to

V

DD

Peak to peak AC noise on

V

may not exceed ± 2%

V

REF (DC)

.

V

REF

is also expected to track noise variations in

V

DDQ

.

For any pin on the DIMM connector under test input of 0 V

V

IN

≤

V

DDQ

+ 0.3 V.

相關PDF資料 |

PDF描述 |

|---|---|

| HYS72T128000GR-37-A | DDR2 Registered Memory Modules |

| HYS72T256020GR-5-A | DDR2 Registered Memory Modules |

| HYS72T256220GR-5-A | DDR2 Registered Memory Modules |

| HYS72T128000GR-5-A | DDR2 Registered Memory Modules |

| HYB18T512400AC | CAP .0022UF 16V PPS FILM 0603 2% |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| HYS72T256020GR-5-A | 制造商:INFINEON 制造商全稱:Infineon Technologies AG 功能描述:DDR2 Registered Memory Modules |

| HYS72T256020HF | 制造商:QIMONDA 制造商全稱:QIMONDA 功能描述:240-Pin Fully-Buffered DDR2 SDRAM Modules |

| HYS72T256020HFA | 制造商:QIMONDA 制造商全稱:QIMONDA 功能描述:240-Pin Fully-Buffered DDR2 SDRAM Modules |

| HYS72T256020HFA-2.5-B | 制造商:QIMONDA 制造商全稱:QIMONDA 功能描述:240-Pin Fully-Buffered DDR2 SDRAM Modules |

| HYS72T256020HFA-3.7-B | 制造商:QIMONDA 制造商全稱:QIMONDA 功能描述:240-Pin Fully-Buffered DDR2 SDRAM Modules |

發(fā)布緊急采購,3分鐘左右您將得到回復。