- 您現在的位置:買賣IC網 > PDF目錄224008 > IDT5V996BBI (INTEGRATED DEVICE TECHNOLOGY INC) 5V SERIES, PLL BASED CLOCK DRIVER, 8 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PBGA144 PDF資料下載

參數資料

| 型號: | IDT5V996BBI |

| 廠商: | INTEGRATED DEVICE TECHNOLOGY INC |

| 元件分類: | 時鐘及定時 |

| 英文描述: | 5V SERIES, PLL BASED CLOCK DRIVER, 8 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PBGA144 |

| 封裝: | PLASTIC, BGA-144 |

| 文件頁數: | 1/9頁 |

| 文件大小: | 78K |

| 代理商: | IDT5V996BBI |

1

INDUSTRIALTEMPERATURERANGE

IDT5V996

3.3V PROGRAMMABLE SKEW PLL CLOCK DRIVER TURBOCLOCK II PLUS

NOVEMBER 2004

2004

Integrated Device Technology, Inc.

DSC 5855/6

c

INDUSTRIAL TEMPERATURE RANGE

The IDT logo is a registered trademark of Integrated Device Technology, Inc.

FEATURES:

3.3V operation

4 pairs of programmable skew outputs

Low skew: 150ps same pair, 350ps all outputs

Selectable positive or negative edge synchronization:

Excellent for DSP applications

Synchronous output enable

Input frequency: 25MHz to 225MHz

Output frequency: 25MHz to 225MHz

2x, 4x, 1/2, and 1/4 outputs (of VCO frequency)

3-level inputs for skew control

PLL bypass for DC testing

External feedback, internal loop filter

12mA balanced drive outputs

Low Jitter: <150ps peak-to-peak

Available in 144-pin BGA package

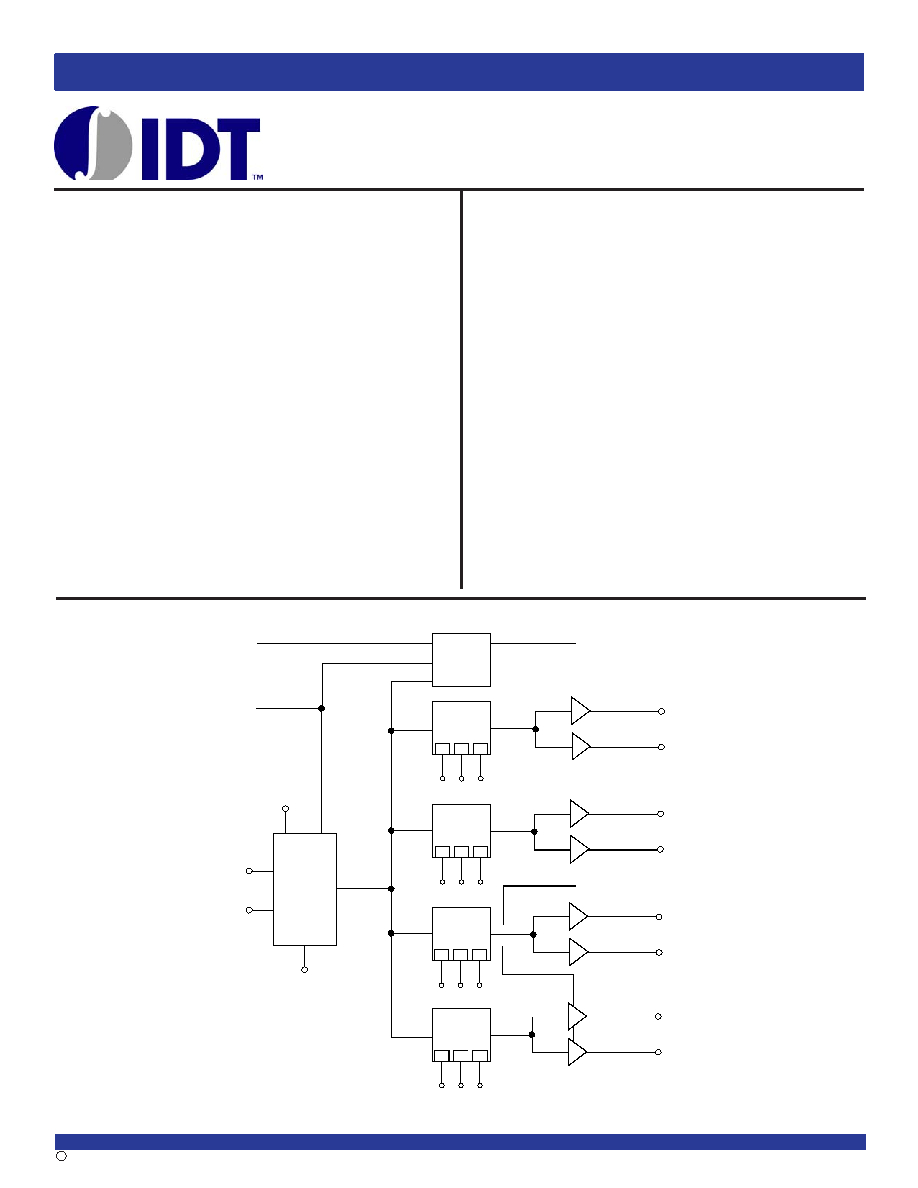

FUNCTIONAL BLOCK DIAGRAM

IDT5V996

3.3V PROGRAMMABLE

SKEW PLL CLOCK DRIVER

TURBOCLOCKTM II PLUS

PLL

Skew

Select

1F2:0

Skew

Select

4F2:0

Skew

Select

3F2:0

Skew

Select

2F2:0

LOC K

FB

REF

TEST

1Q0

1Q 1

2Q0

2Q1

3Q 0

3Q1

4Q0

4Q 1

3

SE

Enable

Logic

3

G

DESCRIPTION:

The IDT5V996 is a high fanout PLL based clock driver intended for high

performancecomputinganddata-communicationapplications.TheIDT5V996

has eight programmable skew outputs organized in four banks of two. Skew

is controlled by 3-level input signals that may be hard wired to appropriate

HIGH-MID-LOW levels. The IDT5V996 provides up to 18 programmable

levels of output skew, prescaling, and other features.

Other features of IDT5V996 are synchronous output enable (G), TEST,

and lock detect indicator (LOCK). When G is held low, all the outputs are

synchronously enabled, however, if G is held high, all outputs except 3Q0

and 3Q1 are in the state designated by SE (HIGH or LOW).

When TEST is held low, the chip operates in normal condition. When held

high, the PLL is shut off and the chip functions as a buffer. The lock detect

indicator asserts high when the phase lock loop has acquired lock. During

acquisition, the indicator is in the low state. Once the PLL has reached the

steady-state condition within a specified frequency range, LOCK is

asserted high.

The PLL is closed externally to provide more flexibility by allowing the

user to control the delay between the input clock and the outputs. The

IDT5V996 has LVTTL outputs with 12mA balanced drive outputs.

The IDT5V996 is characterized for operation from –40°C to +85°C.

相關PDF資料 |

PDF描述 |

|---|---|

| IDT5V996BBI8 | 5V SERIES, PLL BASED CLOCK DRIVER, 8 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PBGA144 |

| IDT71258L35TP | 64K X 4 STANDARD SRAM, 35 ns, PDIP24 |

| IDT71258L55TCB | 64K X 4 STANDARD SRAM, 55 ns, CDIP24 |

| IDT7133SA45L68 | 2K X 16 MULTI-PORT SRAM, 45 ns, CQCC68 |

| IDT7164L45XEB | 8K X 8 STANDARD SRAM, 45 ns, CDFP28 |

相關代理商/技術參數 |

參數描述 |

|---|---|

| IDT600 | 制造商:DRUCK 功能描述:MOISTURE TRAP |

| IDT60ALVCH16823PA | 制造商:IDT 制造商全稱:Integrated Device Technology 功能描述:3.3V CMOS 18-BIT BUS-INTERFACE FLIPFLOP WITH 3-STATE OUTPUTS AND BUS-HOLD |

| IDT60LVC162374APA | 制造商:IDT 制造商全稱:Integrated Device Technology 功能描述:3.3V CMOS 16-BIT EDGE TRIGGERED D-TYPE FLIP-FLOP WITH 3-STATE OUTPUTS, 5 VOLT TOLERANT I/O, BUS-HOLD |

| IDT60LVC162374APF | 制造商:IDT 制造商全稱:Integrated Device Technology 功能描述:3.3V CMOS 16-BIT EDGE TRIGGERED D-TYPE FLIP-FLOP WITH 3-STATE OUTPUTS, 5 VOLT TOLERANT I/O, BUS-HOLD |

| IDT60LVC162374APV | 制造商:IDT 制造商全稱:Integrated Device Technology 功能描述:3.3V CMOS 16-BIT EDGE TRIGGERED D-TYPE FLIP-FLOP WITH 3-STATE OUTPUTS, 5 VOLT TOLERANT I/O, BUS-HOLD |

發(fā)布緊急采購,3分鐘左右您將得到回復。