- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄377263 > IDT7016L35PFB (INTEGRATED DEVICE TECHNOLOGY INC) Quad Low-Power JFET-Input Operational Amplifier 14-PDIP 0 to 70 PDF資料下載

參數(shù)資料

| 型號(hào): | IDT7016L35PFB |

| 廠商: | INTEGRATED DEVICE TECHNOLOGY INC |

| 元件分類: | DRAM |

| 英文描述: | Quad Low-Power JFET-Input Operational Amplifier 14-PDIP 0 to 70 |

| 中文描述: | 16K X 9 DUAL-PORT SRAM, 35 ns, PQFP80 |

| 封裝: | TQFP-80 |

| 文件頁(yè)數(shù): | 10/20頁(yè) |

| 文件大小: | 262K |

| 代理商: | IDT7016L35PFB |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)當(dāng)前第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)

6.13

10

IDT7016S/L

HIGH-SPEED 16K x 9 DUAL-PORT STATIC RAM

MILITARY AND COMMERCIAL TEMPERATURE RANGES

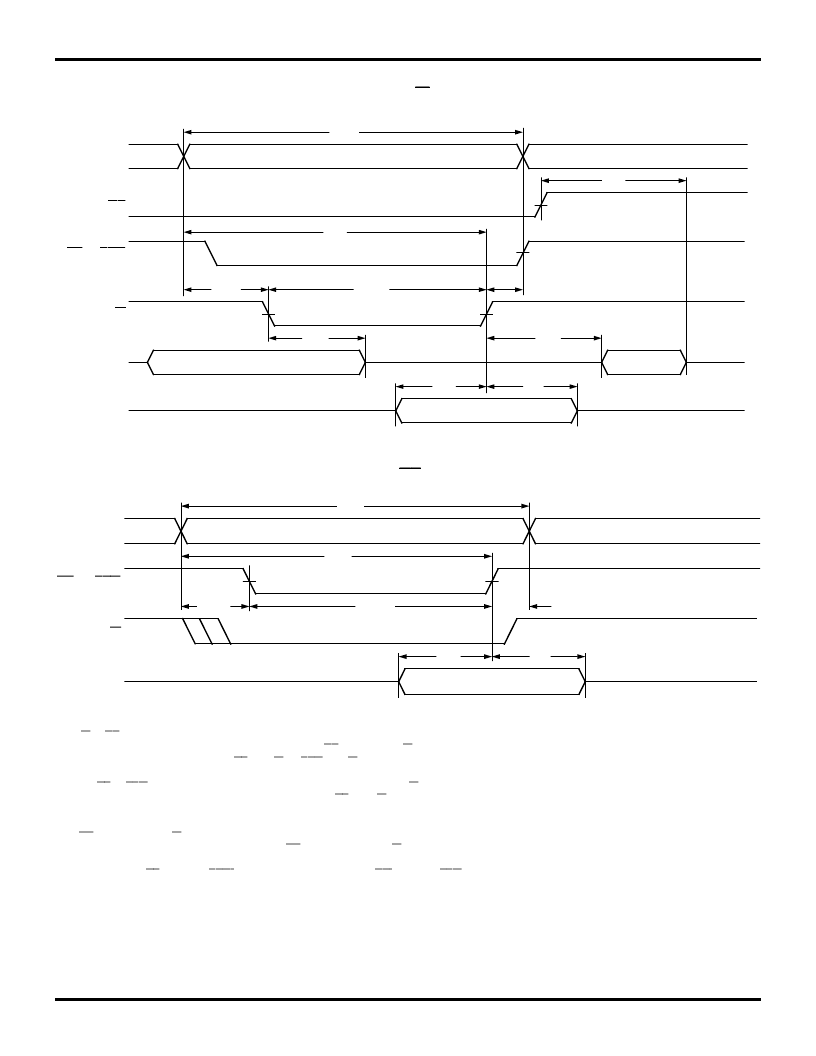

TIMING WAVEFORM OF WRITE CYCLE NO. 1, R/

W

CONTROLLED TIMING

(1,5,8)

R/

W

t

WC

t

HZ

t

AW

t

WR

t

AS

t

WP

DATA

OUT

(2)

t

WZ

t

DW

t

DH

t

OW

OE

ADDRESS

DATA

IN

CE

or

SEM

(6)

(4)

(4)

(3)

3190 drw 09

(7)

(9)

(7)

NOTES:

1. R/

W

or

CE

must be High during all address transitions.

2. A write occurs during the overlap (t

EW

or t

WP

) of a Low

CE

and a Low R/

W

for memory array writing cycle.

3. t

WR

is measured from the earlier of

CE

or R/

W

(or

SEM

or R/

W

) going High to the end of write cycle.

4. During this period, the I/O pins are in the output state and input signals must not be applied.

5. If the

CE

or

SEM

Low transition occurs simultaneously with or after the R/

W

Low transition, the outputs remain in the High-impedance state.

6. Timing depends on which enable signal is asserted last,

CE

or R/

W

.

7. This parameter is guaranteed by device characterization but is not production tested. Transition is measured +/-200mV from steady state with the Output

Test load (Figure 2).

8. If

OE

is Low during R/

W

controlled write cycle, the write pulse width must be the larger of t

WP

or (t

WZ

+ t

DW

) to allow the I/O drivers to turn off and data

to be placed on the bus for the required t

DW

. If

OE

is high during an R/

W

controlled write cycle, this requirement does not apply and the write pulse can

be as short as the specified t

WP

.

9. To access RAM,

CE

= V

IL and

SEM

= V

IH

. To access Semaphore,

CE

= V

IH

and

SEM

= V

IL.

t

EW

must be met for either condition.

3190 drw 10

t

WC

t

AS

t

WR

t

DW

t

DH

ADDRESS

DATA

IN

CE

or

SEM

R/

W

t

AW

t

EW

(3)

(2)

(6)

(9)

TIMING WAVEFORM OF WRITE CYCLE NO. 2,

CE

CONTROLLED TIMING

(1,5)

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| IDT7016S | Low-Power JFET-Input Quad Operational Amplifier 20-LCCC -55 to 125 |

| IDT7016S12G | Low-Power JFET-Input Quad Operational Amplifier 14-CDIP -55 to 125 |

| IDT7016S12GB | Low-Power JFET-Input Quad Operational Amplifier 14-CFP -55 to 125 |

| IDT7016S12J | Low-Power JFET-Input Quad Operational Amplifier 20-LCCC -55 to 125 |

| IDT7016S12JB | Low-Power JFET-Input Quad Operational Amplifier 20-LCCC -55 to 125 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| IDT7016L35PFG | 制造商:IDT 制造商全稱:Integrated Device Technology 功能描述:HIGH-SPEED 16K X 9 DUAL-PORT STATIC RAM |

| IDT7016L35PFGB | 制造商:IDT 制造商全稱:Integrated Device Technology 功能描述:HIGH-SPEED 16K X 9 DUAL-PORT STATIC RAM |

| IDT7016L35PFGI | 制造商:IDT 制造商全稱:Integrated Device Technology 功能描述:HIGH-SPEED 16K X 9 DUAL-PORT STATIC RAM |

| IDT7016S | 制造商:IDT 制造商全稱:Integrated Device Technology 功能描述:HIGH-SPEED 16K x 9 DUAL-PORT STATIC RAM |

| IDT7016S_06 | 制造商:IDT 制造商全稱:Integrated Device Technology 功能描述:HIGH-SPEED 16K X 9 DUAL-PORT STATIC RAM |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。