- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄377341 > IDT71V3556S100PFGI (INTEGRATED DEVICE TECHNOLOGY INC) 128K x 36, 256K x 18 3.3V Synchronous ZBT SRAMs 3.3V I/O, Burst Counter Pipelined Outputs PDF資料下載

參數(shù)資料

| 型號(hào): | IDT71V3556S100PFGI |

| 廠商: | INTEGRATED DEVICE TECHNOLOGY INC |

| 元件分類(lèi): | DRAM |

| 英文描述: | 128K x 36, 256K x 18 3.3V Synchronous ZBT SRAMs 3.3V I/O, Burst Counter Pipelined Outputs |

| 中文描述: | 128K X 36 ZBT SRAM, 5 ns, PQFP100 |

| 封裝: | 14 X 20 MM, 1.40 MM HEIGHT, PLASTIC, TQFP-100 |

| 文件頁(yè)數(shù): | 1/28頁(yè) |

| 文件大小: | 1010K |

| 代理商: | IDT71V3556S100PFGI |

當(dāng)前第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)

SEPTEMBER 2004

DSC-5281/08

1

2004 Integrated Device Technology, Inc.

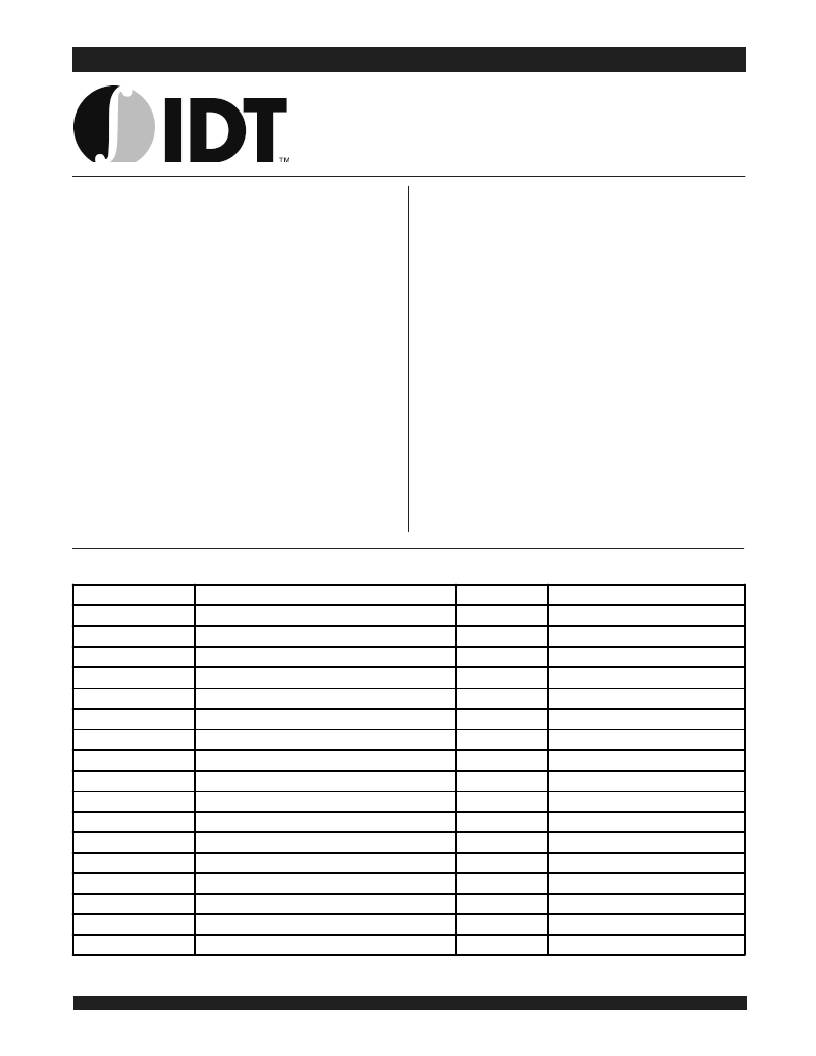

Pin Description Summary

Description

The IDT71V3556/58 are 3.3V high-speed 4,718,592-bit (4.5 Mega-

bit) synchronous SRAMS. They are designed to elimnate dead bus

cycles when turning the bus around between reads and writes, or

writes and reads. Thus, they have been given the name ZBT

TM

, or

Zero Bus Turnaround.

Address and control signals are applied to the SRAMduring one

clock cycle, and two cycles later the associated data cycle occurs, be it

read or write.

The IDT71V3556/58 contain data I/O, address and control signal

registers. Output enable is the only asynchronous signal and can be used

to disable the outputs at any given time.

A Clock Enable (

CEN

) pin allows operation of the IDT71V3556/58

to be suspended as long as necessary. All synchronous inputs are

ignored when (

CEN

) is high and the internal device registers will hold

their previous values.

There are three chip enable pins (

CE

1

, CE

2

,

CE

2

) that allow the user

to deselect the device when desired. If any one of these three are not

asserted when ADV/

LD

is low, no new memory operation can be

initiated. However, any pending data transfers (reads or writes) will be

completed. The data bus will tri-state two cycles after chip is deselected

or a write is initiated.

Features

N

128K x 36, 256K x 18 memory configurations

N

Supports high performance system speed - 200 MHz

(3.2 ns Clock-to-Data Access)

N

ZBT

TM

Feature - No dead cycles between write and read

cycles

N

Internally synchronized output buffer enable eliminates the

need to control

OE

N

Single R/

W

(READ/WRITE) control pin

N

Positive clock-edge triggered address, data, and control

signal registers for fully pipelined applications

N

4-word burst capability (interleaved or linear)

N

Individual byte write (

BW

1

-

BW

4

) control (May tie active)

N

Three chip enables for simple depth expansion

N

3.3V power supply (±5%), 3.3V I/O Supply (V

DDQ)

N

Optional- Boundary Scan JTAG Interface (IEEE 1149.1

compliant)

N

Packaged in a JEDEC standard 100-pin plastic thin quad

flatpack (TQFP), 119 ball grid array (BGA) and 165 fine pitch

ball grid array (fBGA)

A

0

-A

17

Address Inputs

Input

Synchronous

CE

1

, CE

2

,

CE

2

Chip Enables

Input

Synchronous

OE

Output Enable

Input

Asynchronous

R/

W

Read/Write Signal

Input

Synchronous

CEN

Clock Enable

Input

Synchronous

BW

1

,

BW

2

,

BW

3

,

BW

4

Individual Byte Write Selects

Input

Synchronous

CLK

Clock

Input

N/A

ADV/

LD

Advance burst address / Load newaddress

Input

Synchronous

LBO

Linear / Interleaved BurstOrder

Input

Static

TMS

Test Mode Select

Input

Synchronous

TDI

Test Data Input

Input

Synchronous

TCK

Test Clock

Input

N/A

TDO

Test Data Output

Output

Synchronous

TRST

JTAG Reset (Optional)

Input

Asynchronous

ZZ

Sleep Mode

Input

Synchronous

I/O

0

-I/O

31

, I/O

P1

-I/O

P4

Data Input / Output

I/O

Synchronous

V

DD

, V

DDQ

Core Power I/O Power

Supply

Static

V

SS

Ground

Supply

Static

5281 tbl 01

IDT71V3556S

IDT71V3558S

IDT71V3556SA

IDT71V3558SA

128K x 36, 256K x 18

3.3V Synchronous ZBT SRAMs

3.3V I/O, Burst Counter

Pipelined Outputs

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| IDT71V3556S133BGGI | 128K x 36, 256K x 18 3.3V Synchronous ZBT SRAMs 3.3V I/O, Burst Counter Pipelined Outputs |

| IDT71V3556S133BQG | 128K x 36, 256K x 18 3.3V Synchronous ZBT SRAMs 3.3V I/O, Burst Counter Pipelined Outputs |

| IDT71V3556S133BQGI | 128K x 36, 256K x 18 3.3V Synchronous ZBT SRAMs 3.3V I/O, Burst Counter Pipelined Outputs |

| IDT71V3556S133PFGI | 128K x 36, 256K x 18 3.3V Synchronous ZBT SRAMs 3.3V I/O, Burst Counter Pipelined Outputs |

| IDT71V3556S166BGGI | 128K x 36, 256K x 18 3.3V Synchronous ZBT SRAMs 3.3V I/O, Burst Counter Pipelined Outputs |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| IDT71V3556S100PFGI8 | 功能描述:IC SRAM 4MBIT 100MHZ 100TQFP RoHS:是 類(lèi)別:集成電路 (IC) >> 存儲(chǔ)器 系列:- 標(biāo)準(zhǔn)包裝:72 系列:- 格式 - 存儲(chǔ)器:RAM 存儲(chǔ)器類(lèi)型:SRAM - 同步 存儲(chǔ)容量:4.5M(256K x 18) 速度:133MHz 接口:并聯(lián) 電源電壓:3.135 V ~ 3.465 V 工作溫度:0°C ~ 70°C 封裝/外殼:100-LQFP 供應(yīng)商設(shè)備封裝:100-TQFP(14x20) 包裝:托盤(pán) |

| IDT71V3556S100PFI | 功能描述:IC SRAM 4MBIT 100MHZ 100TQFP RoHS:否 類(lèi)別:集成電路 (IC) >> 存儲(chǔ)器 系列:- 產(chǎn)品變化通告:Product Discontinuation 05/Nov/2008 標(biāo)準(zhǔn)包裝:84 系列:- 格式 - 存儲(chǔ)器:RAM 存儲(chǔ)器類(lèi)型:SRAM - 同步 ZBT 存儲(chǔ)容量:4.5M(128K x 36) 速度:75ns 接口:并聯(lián) 電源電壓:3.135 V ~ 3.465 V 工作溫度:-40°C ~ 85°C 封裝/外殼:119-BGA 供應(yīng)商設(shè)備封裝:119-PBGA(14x22) 包裝:托盤(pán) 其它名稱:71V3557SA75BGI |

| IDT71V3556S100PFI8 | 功能描述:IC SRAM 4MBIT 100MHZ 100TQFP RoHS:否 類(lèi)別:集成電路 (IC) >> 存儲(chǔ)器 系列:- 產(chǎn)品變化通告:Product Discontinuation 05/Nov/2008 標(biāo)準(zhǔn)包裝:84 系列:- 格式 - 存儲(chǔ)器:RAM 存儲(chǔ)器類(lèi)型:SRAM - 同步 ZBT 存儲(chǔ)容量:4.5M(128K x 36) 速度:75ns 接口:并聯(lián) 電源電壓:3.135 V ~ 3.465 V 工作溫度:-40°C ~ 85°C 封裝/外殼:119-BGA 供應(yīng)商設(shè)備封裝:119-PBGA(14x22) 包裝:托盤(pán) 其它名稱:71V3557SA75BGI |

| IDT71V3556S133BG | 功能描述:IC SRAM 4MBIT 133MHZ 119BGA RoHS:否 類(lèi)別:集成電路 (IC) >> 存儲(chǔ)器 系列:- 產(chǎn)品變化通告:Product Discontinuation 05/Nov/2008 標(biāo)準(zhǔn)包裝:84 系列:- 格式 - 存儲(chǔ)器:RAM 存儲(chǔ)器類(lèi)型:SRAM - 同步 ZBT 存儲(chǔ)容量:4.5M(128K x 36) 速度:75ns 接口:并聯(lián) 電源電壓:3.135 V ~ 3.465 V 工作溫度:-40°C ~ 85°C 封裝/外殼:119-BGA 供應(yīng)商設(shè)備封裝:119-PBGA(14x22) 包裝:托盤(pán) 其它名稱:71V3557SA75BGI |

| IDT71V3556S133BG8 | 功能描述:IC SRAM 4MBIT 133MHZ 119BGA RoHS:否 類(lèi)別:集成電路 (IC) >> 存儲(chǔ)器 系列:- 產(chǎn)品變化通告:Product Discontinuation 05/Nov/2008 標(biāo)準(zhǔn)包裝:84 系列:- 格式 - 存儲(chǔ)器:RAM 存儲(chǔ)器類(lèi)型:SRAM - 同步 ZBT 存儲(chǔ)容量:4.5M(128K x 36) 速度:75ns 接口:并聯(lián) 電源電壓:3.135 V ~ 3.465 V 工作溫度:-40°C ~ 85°C 封裝/外殼:119-BGA 供應(yīng)商設(shè)備封裝:119-PBGA(14x22) 包裝:托盤(pán) 其它名稱:71V3557SA75BGI |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。