- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄10118 > IDT72201L10PFG8 (IDT, Integrated Device Technology Inc)IC FIFO 256X9 SYNC 10NS 32-TQFP PDF資料下載

參數(shù)資料

| 型號: | IDT72201L10PFG8 |

| 廠商: | IDT, Integrated Device Technology Inc |

| 文件頁數(shù): | 10/14頁 |

| 文件大小: | 0K |

| 描述: | IC FIFO 256X9 SYNC 10NS 32-TQFP |

| 標準包裝: | 2,000 |

| 系列: | 7200 |

| 功能: | 同步 |

| 存儲容量: | 2.3K(256 x 9) |

| 數(shù)據(jù)速率: | 100MHz |

| 訪問時間: | 11.5ns |

| 電源電壓: | 4.5 V ~ 5.5 V |

| 工作溫度: | 0°C ~ 70°C |

| 安裝類型: | 表面貼裝 |

| 封裝/外殼: | 32-LQFP |

| 供應商設備封裝: | 32-TQFP(7x7) |

| 包裝: | 帶卷 (TR) |

| 其它名稱: | 72201L10PFG8 |

5

COMMERCIALANDINDUSTRIAL

TEMPERATURERANGES

IDT72421/72201/72211/72221/72231/72241/72251 CMOS SyncFIFO

64 x 9, 256 x 9, 512 x 9, 1,024 x 9, 2,048 x 9, 4,096 x 9 and 8,192 x 9

OUTPUT ENABLE (OE)

When Output Enable (OE) is enabled (LOW), the parallel output buffers

receive data from the output register. When Output Enable (OE) is disabled

(HIGH), the Q output data bus is in a high-impedance state.

WRITE ENABLE 2/LOAD (WEN2/LD)

This is a dual-purpose pin. The FIFO is configured at Reset to have

programmableflagsortohavetwowriteenables,whichallowsdepthexpansion.

IfWriteEnable2/Load(WEN2/LD)issetHIGHatReset(RS =LOW),thispin

operates as a second write enable pin.

If the FIFO is configured to have two write enables, when Write Enable

(WEN1) is LOW and Write Enable 2/Load (WEN2/LD) is HIGH, data can be

loaded into the input register and RAM array on the LOW-to-HIGH transition

ofeveryWriteClock(WCLK). DataisstoredintheRAMarraysequentiallyand

independently of any ongoing read operation.

In this configuration, when Write Enable (WEN1) is HIGH and/or Write

Enable2/Load(WEN2/LD)isLOW,theinputregisterholdsthepreviousdata

and no new data is allowed to be loaded into the register.

Topreventdataoverflow,theFullFlag(FF)willgoLOW,inhibitingfurther

writeoperations. Uponthecompletionofavalidreadcycle,theFullFlag(FF)

willgoHIGHaftertWFF,allowingavalidwritetobegin. WriteEnable1(WEN1)

and Write Enable 2/Load (WEN2/LD) are ignored when the FIFO is full.

TheFIFOisconfiguredtohaveprogrammableflagswhentheWriteEnable

2/Load (WEN2/LD) is set LOW at Reset (RS=LOW). The IDT72421/72201/

72211/72221/72231/72241/72251devicescontainfour8-bitoffsetregisters

whichcanbeloadedwithdataontheinputs,orreadontheoutputs. SeeFigure

3 for details of the size of the registers and the default values.

IftheFIFOisconfiguredtohaveprogrammableflagswhentheWriteEnable

1(WEN1)andWriteEnable2/Load(WEN2/LD)aresetLOW,dataontheinputs

DiswrittenintotheEmpty(LeastSignificantBit)OffsetregisteronthefirstLOW-

to-HIGHtransitionoftheWriteClock(WCLK). DataiswrittenintotheEmpty(Most

SignificantBit)OffsetregisteronthesecondLOW-to-HIGHtransitionoftheWrite

Clock (WCLK), into the Full (Least Significant Bit) Offset register on the third

transition, and into the Full (Most Significant Bit) Offset register on the fourth

transition. ThefifthtransitionoftheWriteClock(WCLK)againwritestotheEmpty

(LeastSignificantBit)Offsetregister.

However,writingalloffsetregistersdoesnothavetooccuratonetime. One

ortwooffsetregisterscanbewrittenandthenbybringingtheWriteEnable2/

Load (WEN2/LD) pin HIGH, the FIFO is returned to normal read/write

operation. WhentheWriteEnable2/Load(WEN2/LD)pinissetLOW,theWrite

Enable 1 (WEN1) is LOW, the next offset register in sequence is written.

SIGNAL DESCRIPTIONS

INPUTS:

DATA IN (D0 - D8)

Data inputs for 9-bit wide data.

CONTROLS:

RESET (RS)

Reset is accomplished whenever the Reset (RS) input is taken to a LOW

state. During reset, both internal read and write pointers are set to the first

location. A reset is required after power-up before a write operation can take

place. TheFullFlag(FF)andProgrammableAlmost-Fullflag(PAF)willbereset

to HIGH after tRSF. The Empty Flag (EF) and Programmable Almost-Empty

flag(PAE)willberesettoLOWaftertRSF. Duringreset,theoutputregisteris

initializedtoallzerosandtheoffsetregistersareinitializedtotheirdefaultvalues.

WRITE CLOCK (WCLK)

AwritecycleisinitiatedontheLOW-to-HIGHtransitionoftheWriteClock

(WCLK). DatasetupandholdtimesmustbemetinrespecttotheLOW-to-HIGH

transition of WCLK. The Full Flag (FF) and Programmable Almost-Full flag

(PAF)aresynchronizedwithrespecttotheLOW-to-HIGHtransitionofWCLK.

The Write and Read Clocks can be asynchronous or coincident.

WRITE ENABLE 1 (WEN1)

If the FIFO is configured for programmable flags, Write Enable 1 (WEN1)

istheonlyenablecontrolpin. Inthisconfiguration,whenWriteEnable1(WEN1)

isLOW,datacanbeloadedintotheinputregisterandRAMarrayontheLOW-

to-HIGHtransitionofeveryWriteClock(WCLK). DataisstoredintheRAMarray

sequentially and independently of any ongoing read operation.

Inthisconfiguration,whenWriteEnable1(WEN1)isHIGH,theinputregister

holdsthepreviousdataandnonewdataisallowedtobeloadedintotheregister.

IftheFIFOisconfiguredtohavetwowriteenables,whichallowsfordepth

expansion,therearetwoenablecontrolpins. SeeWriteEnable2paragraph

belowforoperationinthisconfiguration.

Topreventdataoverflow,theFullFlag(FF)willgoLOW,inhibitingfurther

writeoperations. Uponthecompletionofavalidreadcycle,theFullFlag(FF)

willgoHIGHaftertWFF,allowingavalidwritetobegin. WriteEnable1(WEN1)

is ignored when the FIFO is full.

READ CLOCK (RCLK)

DatacanbereadontheoutputsontheLOW-to-HIGHtransitionoftheRead

Clock (RCLK). The Empty Flag (EF) and Programmable Almost-Empty flag

(PAE)aresynchronizedwithrespecttotheLOW-to-HIGHtransitionofRCLK.

The Write and Read Clocks can be asynchronous or coincident.

READ ENABLES (REN1, REN2)

When both Read Enables (REN1, REN2) are LOW, data is read from the

RAM array to the output register on the LOW-to-HIGH transition of the Read

Clock (RCLK).

WheneitherReadEnable(REN1,REN2)isHIGH,theoutputregisterholds

the previous data and no new data is allowed to be loaded into the register.

When all the data has been read from the FIFO, the Empty Flag (EF) will

go LOW, inhibiting further read operations. Once a valid write operation has

been accomplished, the Empty Flag (EF) will go HIGH after tREF and a valid

readcanbegin. TheReadEnables(REN1,REN2)areignoredwhentheFIFO

isempty.

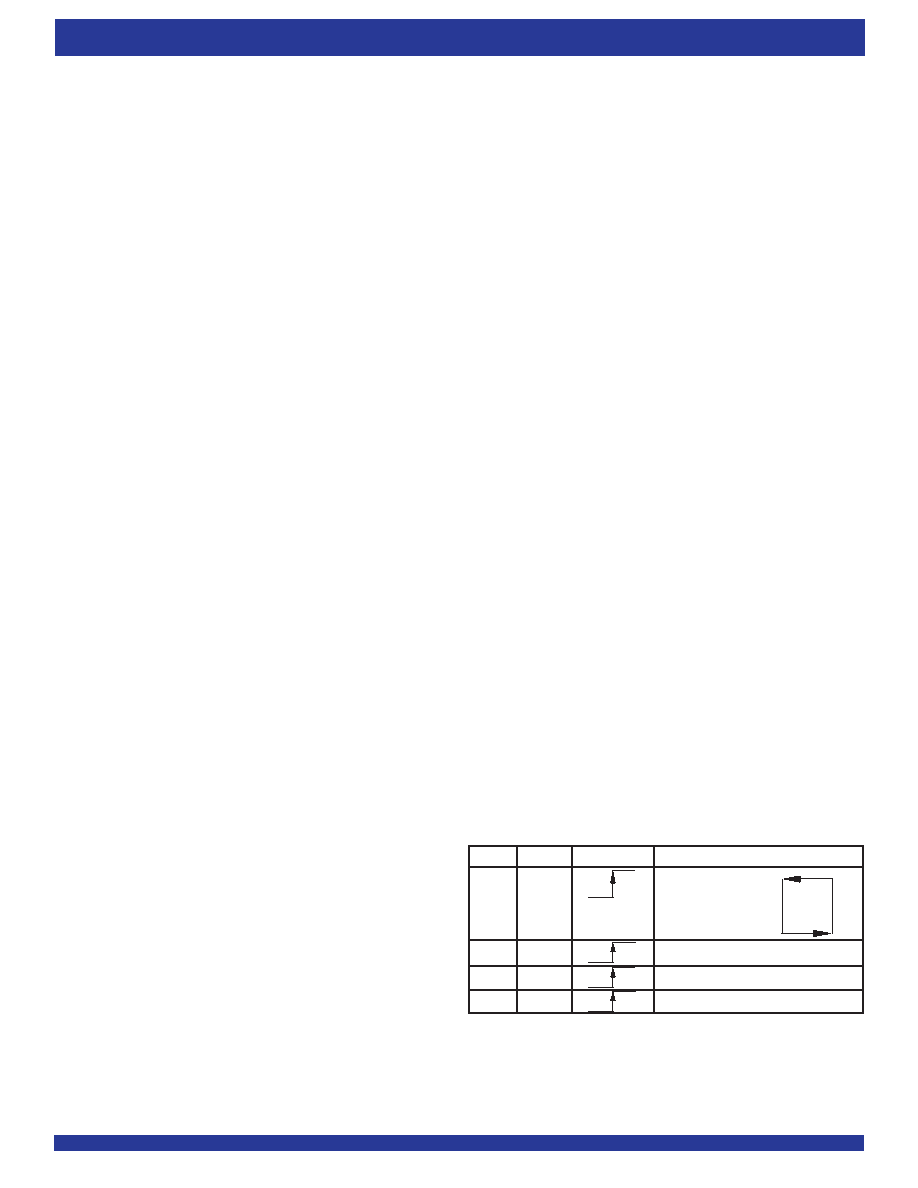

LD

WEN1

WCLK

Selection

0

EmptyOffset(LSB)

Empty Offset (MSB)

Full Offset (LSB)

Full Offset (MSB)

0

1

No Operation

1

0

Write Into FIFO

1

No Operation

NOTE:

1. For the purposes of this table, WEN2 = VIH.

2. The same selection sequence applies to reading from the registers. REN1 and REN2

are enabled and read is performed on the LOW-to-HIGH transition of RCLK.

Figure 2. Write Offset Register

相關PDF資料 |

PDF描述 |

|---|---|

| LTC2863CS8-2#TRPBF | IC TRANSCEIVER RS485 8-SOIC |

| VI-B3Z-IV-B1 | CONVERTER MOD DC/DC 2V 60W |

| VI-B3Z-IU-F4 | CONVERTER MOD DC/DC 2V 80W |

| MS3106A18-65P | CONN PLUG 6POS STRAIGHT W/PINS |

| LTC2141CUP-14#TRPBF | IC ADC DUAL 14BIT 40 MSPS 64-QFN |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| IDT72201L15J | 功能描述:IC FIFO 256X9 SYNC 15NS 32-PLCC RoHS:否 類別:集成電路 (IC) >> 邏輯 - FIFO 系列:7200 標準包裝:80 系列:7200 功能:同步 存儲容量:18.4K(1K x 18) 數(shù)據(jù)速率:- 訪問時間:10ns 電源電壓:4.5 V ~ 5.5 V 工作溫度:0°C ~ 70°C 安裝類型:表面貼裝 封裝/外殼:64-LQFP 供應商設備封裝:64-TQFP(10x10) 包裝:托盤 其它名稱:72225LB10TF |

| IDT72201L15J8 | 功能描述:IC FIFO 256X9 SYNC 15NS 32-PLCC RoHS:否 類別:集成電路 (IC) >> 邏輯 - FIFO 系列:7200 標準包裝:80 系列:7200 功能:同步 存儲容量:18.4K(1K x 18) 數(shù)據(jù)速率:- 訪問時間:10ns 電源電壓:4.5 V ~ 5.5 V 工作溫度:0°C ~ 70°C 安裝類型:表面貼裝 封裝/外殼:64-LQFP 供應商設備封裝:64-TQFP(10x10) 包裝:托盤 其它名稱:72225LB10TF |

| IDT72201L15JI | 功能描述:IC FIFO 256X9 SYNC 15NS 32-PLCC RoHS:否 類別:集成電路 (IC) >> 邏輯 - FIFO 系列:7200 標準包裝:80 系列:7200 功能:同步 存儲容量:18.4K(1K x 18) 數(shù)據(jù)速率:- 訪問時間:10ns 電源電壓:4.5 V ~ 5.5 V 工作溫度:0°C ~ 70°C 安裝類型:表面貼裝 封裝/外殼:64-LQFP 供應商設備封裝:64-TQFP(10x10) 包裝:托盤 其它名稱:72225LB10TF |

| IDT72201L15JI8 | 功能描述:IC FIFO 256X9 SYNC 15NS 32-PLCC RoHS:否 類別:集成電路 (IC) >> 邏輯 - FIFO 系列:7200 標準包裝:80 系列:7200 功能:同步 存儲容量:18.4K(1K x 18) 數(shù)據(jù)速率:- 訪問時間:10ns 電源電壓:4.5 V ~ 5.5 V 工作溫度:0°C ~ 70°C 安裝類型:表面貼裝 封裝/外殼:64-LQFP 供應商設備封裝:64-TQFP(10x10) 包裝:托盤 其它名稱:72225LB10TF |

| IDT72201L15PF | 功能描述:IC FIFO 256X9 SYNC 15NS 32-TQFP RoHS:否 類別:集成電路 (IC) >> 邏輯 - FIFO 系列:7200 標準包裝:80 系列:7200 功能:同步 存儲容量:18.4K(1K x 18) 數(shù)據(jù)速率:- 訪問時間:10ns 電源電壓:4.5 V ~ 5.5 V 工作溫度:0°C ~ 70°C 安裝類型:表面貼裝 封裝/外殼:64-LQFP 供應商設備封裝:64-TQFP(10x10) 包裝:托盤 其它名稱:72225LB10TF |

發(fā)布緊急采購,3分鐘左右您將得到回復。