- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄377403 > IDT72201L15PFI (INTEGRATED DEVICE TECHNOLOGY INC) SerDes Low Voltage 24-Bit Bi-Directional Serializer/Deserializer; Package: MLP; No of Pins: 40; Container: Tape & Reel PDF資料下載

參數(shù)資料

| 型號(hào): | IDT72201L15PFI |

| 廠商: | INTEGRATED DEVICE TECHNOLOGY INC |

| 元件分類(lèi): | DRAM |

| 英文描述: | SerDes Low Voltage 24-Bit Bi-Directional Serializer/Deserializer; Package: MLP; No of Pins: 40; Container: Tape & Reel |

| 中文描述: | 256 X 9 OTHER FIFO, 10 ns, PQFP32 |

| 封裝: | TQFP-32 |

| 文件頁(yè)數(shù): | 8/14頁(yè) |

| 文件大?。?/td> | 155K |

| 代理商: | IDT72201L15PFI |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)當(dāng)前第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)

COMMERCIAL AND INDUSTRIAL

TEMPERATURE RANGES

IDT72421/72201/72211/72221/72231/72241/72251 CMOS SyncFIFO

64 x 9, 256 x 9, 512 x 9, 1,024 x 9, 2,048 x 9, 4,096 x 9 and 8,192 x 9

8

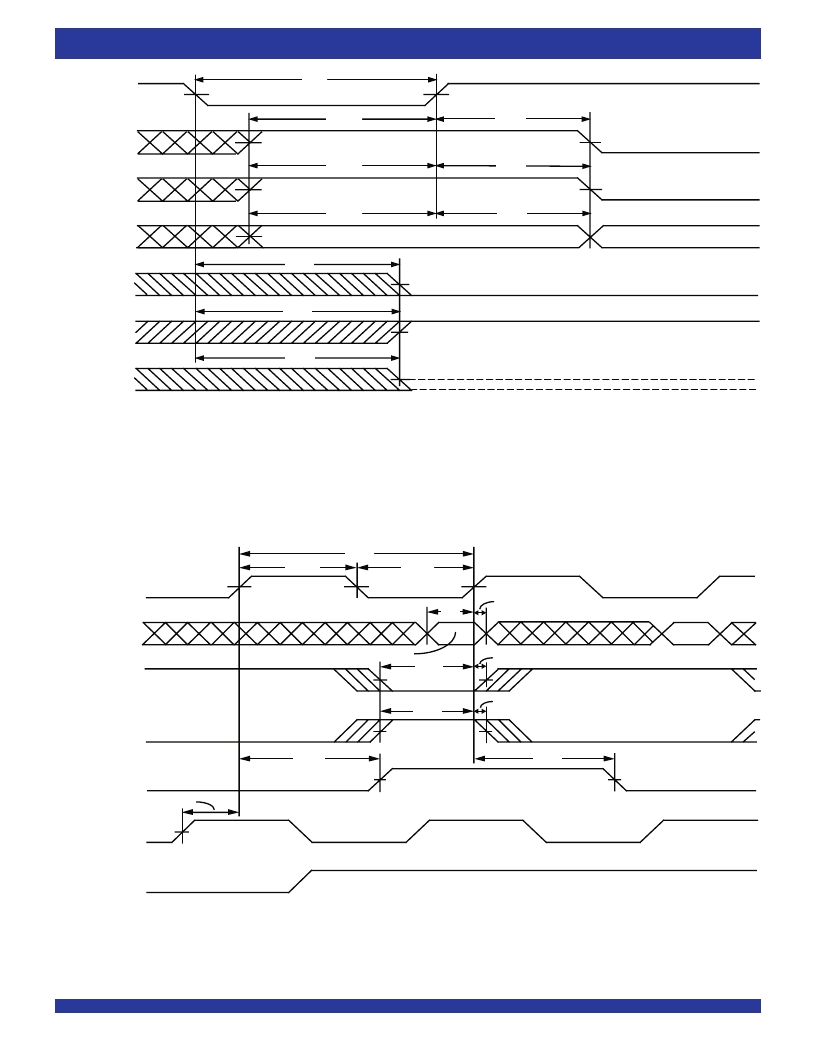

NOTE:

1. t

SKEW1

is the mnimumtime between a rising RCLK edge and a rising WCLK edge for

FF

to change during the current clock cycle. If the time between the rising edge of RCLK

and the rising edge of WCLK is less than t

SKEW

1, then

FF

may not change state until the next WCLK edge.

Figure 5. Write Cycle Timing

NOTES:

1. Holding WEN2/

LD

HIGH during reset will make the pin act as a second write enable pin. Holding WEN2/

LD

LOW during reset will make the pin act as a load enable for the programmable

flag offset registers.

2. After reset, the outputs will be LOW if

OE

= 0 and tri-state if

OE

= 1.

3.

The clocks (RCLK, WCLK) can be free-running during reset.

Figure 4. Reset Timing

t

RS

t

RSR

RS

REN1

,

REN2

t

RSF

t

RSF

= 1

OE

= 0

(2)

EF

,

PAE

FF

,

PAF

Q

0

- Q

8

2655 drw 06

WEN1

(1)

WEN2/

LD

t

RSS

t

RSF

t

RSR

t

RSS

t

RSR

t

RSS

t

DH

t

ENH

t

SKEW1(1)

t

CLK

t

CLKH

t

CLKL

t

DS

t

ENS

t

WFF

t

WFF

WCLK

D

0

- D

8

WEN1

WEN2/

(If Applicable)

FF

RCLK

REN1

,

REN2

NO OPERATION

NO OPERATION

2655 drw 07

DATA IN VALID

t

ENH

t

ENS

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| IDT72201L25J | 24-Bit Ultra-Low Power Serializer Deserializer Supporting Single and Dual Displays (*Recommended for new designs); Package: BGA; No of Pins: 42; Container: Tape & Reel |

| IDT72201L25JI | 24-Bit Ultra-Low Power Serializer Deserializer Supporting Single and Dual Displays (*Recommended for new designs); Package: MLP; No of Pins: 40; Container: Tape & Reel |

| IDT72201L25PF | Low Voltage 28-Bit Flat Panel Display Link Serializers |

| IDT72201L25PFI | Low Voltage 28-Bit Flat Panel Display Link Serializers; Package: TSSOP; No of Pins: 56; Container: Tape & Reel |

| IDT72251L10J | CMOS SyncFIFOO 64 X 9, 256 x 9, 512 x 9, 1024 X 9, 2048 X 9 and 4096 x 9 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| IDT72201L15PFI8 | 功能描述:IC FIFO 256X9 SYNC 15NS 32-TQFP RoHS:否 類(lèi)別:集成電路 (IC) >> 邏輯 - FIFO 系列:7200 標(biāo)準(zhǔn)包裝:80 系列:7200 功能:同步 存儲(chǔ)容量:18.4K(1K x 18) 數(shù)據(jù)速率:- 訪(fǎng)問(wèn)時(shí)間:10ns 電源電壓:4.5 V ~ 5.5 V 工作溫度:0°C ~ 70°C 安裝類(lèi)型:表面貼裝 封裝/外殼:64-LQFP 供應(yīng)商設(shè)備封裝:64-TQFP(10x10) 包裝:托盤(pán) 其它名稱(chēng):72225LB10TF |

| IDT72201L20J | 制造商:Integrated Device Technology Inc 功能描述:FIFO, 256 x 9, Synchronous, 32 Pin, Plastic, PLCC |

| IDT72201L25J | 功能描述:IC FIFO 256X9 SYNC 25NS 32-PLCC RoHS:否 類(lèi)別:集成電路 (IC) >> 邏輯 - FIFO 系列:7200 標(biāo)準(zhǔn)包裝:90 系列:74ABT 功能:同步,雙端口 存儲(chǔ)容量:4.6K(64 x 36 x2) 數(shù)據(jù)速率:67MHz 訪(fǎng)問(wèn)時(shí)間:- 電源電壓:4.5 V ~ 5.5 V 工作溫度:0°C ~ 70°C 安裝類(lèi)型:表面貼裝 封裝/外殼:120-LQFP 裸露焊盤(pán) 供應(yīng)商設(shè)備封裝:120-HLQFP(14x14) 包裝:托盤(pán) 產(chǎn)品目錄頁(yè)面:1005 (CN2011-ZH PDF) 其它名稱(chēng):296-3984 |

| IDT72201L25J8 | 功能描述:IC FIFO 256X9 SYNC 25NS 32-PLCC RoHS:否 類(lèi)別:集成電路 (IC) >> 邏輯 - FIFO 系列:7200 標(biāo)準(zhǔn)包裝:80 系列:7200 功能:同步 存儲(chǔ)容量:18.4K(1K x 18) 數(shù)據(jù)速率:- 訪(fǎng)問(wèn)時(shí)間:10ns 電源電壓:4.5 V ~ 5.5 V 工作溫度:0°C ~ 70°C 安裝類(lèi)型:表面貼裝 封裝/外殼:64-LQFP 供應(yīng)商設(shè)備封裝:64-TQFP(10x10) 包裝:托盤(pán) 其它名稱(chēng):72225LB10TF |

| IDT72201L25JI | 功能描述:IC FIFO 256X9 SYNC 25NS 32-PLCC RoHS:否 類(lèi)別:集成電路 (IC) >> 邏輯 - FIFO 系列:7200 標(biāo)準(zhǔn)包裝:80 系列:7200 功能:同步 存儲(chǔ)容量:18.4K(1K x 18) 數(shù)據(jù)速率:- 訪(fǎng)問(wèn)時(shí)間:10ns 電源電壓:4.5 V ~ 5.5 V 工作溫度:0°C ~ 70°C 安裝類(lèi)型:表面貼裝 封裝/外殼:64-LQFP 供應(yīng)商設(shè)備封裝:64-TQFP(10x10) 包裝:托盤(pán) 其它名稱(chēng):72225LB10TF |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。