- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄377404 > IDT72225LB25G (INTEGRATED DEVICE TECHNOLOGY INC) CMOS SyncFIFOO 256 x 18, 512 x 18, 1024 x 18, 2048 x 18 and 4096 x 18 PDF資料下載

參數(shù)資料

| 型號: | IDT72225LB25G |

| 廠商: | INTEGRATED DEVICE TECHNOLOGY INC |

| 元件分類: | DRAM |

| 英文描述: | CMOS SyncFIFOO 256 x 18, 512 x 18, 1024 x 18, 2048 x 18 and 4096 x 18 |

| 中文描述: | 1K X 18 OTHER FIFO, CPGA68 |

| 封裝: | CAVITY-UP, PGA-68 |

| 文件頁數(shù): | 10/16頁 |

| 文件大小: | 181K |

| 代理商: | IDT72225LB25G |

10

IDT72205LB/72215LB/72225LB/72235LB/72245LB CMOS SyncFIFO

256 x 18, 512 x 18, 1,024 x 18, 2,048 x 18 and 4,096 x 18

Commercial And Industrial Temperature Ranges

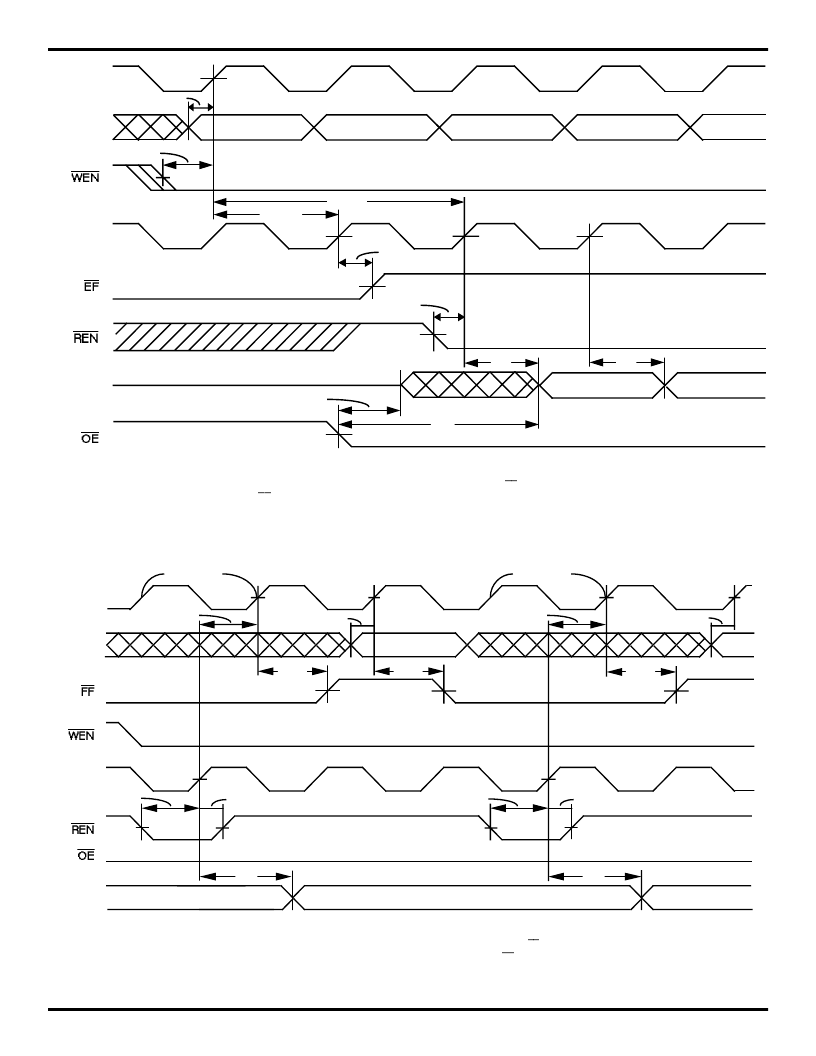

Figure 7. First Data Word Latency after Reset with Simultaneous Read and Write

Figure 8. Full Flag Timing

WCLK

D

0

- D

17

RCLK

Q

0

- Q

17

t

DS

t

SKEW2

t

ENS

t

REF

t

A

0

1

2

3

D

D

D

D

0

1

D

D

(first valid write)

t

OE

t

OLZ

t

A

t

FRL(1)

D

4

t

ENS

2766 drw 09

NOTE:

1. t

SKEW1

is the minimum time between a rising RCLK edge and a rising WCLK edge to guarantee that

FF

will go HIGH during the current clock cycle. If the

time between the rising edge of RCLK and the rising edge of WCLK is less than t

SKEW1

, then

FF

may not change state until the next WCLK edge.

DATA READ

WCLK

D

0

- D

17

RCLK

Q

0

- Q

17

t

A

t

WFF

DATA WRITE

t

WFF

t

ENH

t

ENS

t

DS

t

WFF

t

DS

DATA

WRITE

NEXT DATA READ

t

A

NO WRITE

NO WRITE

DATA IN OUTPUT REGISTER

LOW

t

SKEW1(1)

t

SKEW11)

t

ENH

t

ENS

2766 drw 10

NOTES:

1. When t

SKEW2

minimum specification, t

FRL

(maximum) = t

CLK

+ t

SKEW2

. When t

SKEW2

< minimum specification, t

FRL

(maximum) = either

2*t

CLK

+ t

SKEW2 or

t

CLK

+ t

SKEW2

. The Latency Timing applies only at the Empty Boundary (

EF

= LOW).

2. The first word is available the cycle after

EF

goes HIGH, always.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| IDT72225LB25J | CMOS SyncFIFOO 256 x 18, 512 x 18, 1024 x 18, 2048 x 18 and 4096 x 18 |

| IDT72225LB25TF | CMOS SyncFIFOO 256 x 18, 512 x 18, 1024 x 18, 2048 x 18 and 4096 x 18 |

| IDT72225LB25TFB | CMOS SyncFIFOO 256 x 18, 512 x 18, 1024 x 18, 2048 x 18 and 4096 x 18 |

| IDT72225LB25TFI | CMOS SyncFIFOO 256 x 18, 512 x 18, 1024 x 18, 2048 x 18 and 4096 x 18 |

| IDT72225LB35G | CMOS SyncFIFOO 256 x 18, 512 x 18, 1024 x 18, 2048 x 18 and 4096 x 18 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| IDT72225LB25J | 功能描述:IC FIFO 1024X18 SYNC 25NS 68PLCC RoHS:否 類別:集成電路 (IC) >> 邏輯 - FIFO 系列:7200 標(biāo)準(zhǔn)包裝:80 系列:7200 功能:同步 存儲容量:18.4K(1K x 18) 數(shù)據(jù)速率:- 訪問時間:10ns 電源電壓:4.5 V ~ 5.5 V 工作溫度:0°C ~ 70°C 安裝類型:表面貼裝 封裝/外殼:64-LQFP 供應(yīng)商設(shè)備封裝:64-TQFP(10x10) 包裝:托盤 其它名稱:72225LB10TF |

| IDT72225LB25J8 | 功能描述:IC FIFO 1024X18 SYNC 25NS 68PLCC RoHS:否 類別:集成電路 (IC) >> 邏輯 - FIFO 系列:7200 標(biāo)準(zhǔn)包裝:80 系列:7200 功能:同步 存儲容量:18.4K(1K x 18) 數(shù)據(jù)速率:- 訪問時間:10ns 電源電壓:4.5 V ~ 5.5 V 工作溫度:0°C ~ 70°C 安裝類型:表面貼裝 封裝/外殼:64-LQFP 供應(yīng)商設(shè)備封裝:64-TQFP(10x10) 包裝:托盤 其它名稱:72225LB10TF |

| IDT72225LB25JI | 功能描述:IC FIFO 1024X18 SYNC 25NS 68PLCC RoHS:否 類別:集成電路 (IC) >> 邏輯 - FIFO 系列:7200 標(biāo)準(zhǔn)包裝:80 系列:7200 功能:同步 存儲容量:18.4K(1K x 18) 數(shù)據(jù)速率:- 訪問時間:10ns 電源電壓:4.5 V ~ 5.5 V 工作溫度:0°C ~ 70°C 安裝類型:表面貼裝 封裝/外殼:64-LQFP 供應(yīng)商設(shè)備封裝:64-TQFP(10x10) 包裝:托盤 其它名稱:72225LB10TF |

| IDT72225LB25JI8 | 功能描述:IC FIFO 1024X18 SYNC 25NS 68PLCC RoHS:否 類別:集成電路 (IC) >> 邏輯 - FIFO 系列:7200 標(biāo)準(zhǔn)包裝:80 系列:7200 功能:同步 存儲容量:18.4K(1K x 18) 數(shù)據(jù)速率:- 訪問時間:10ns 電源電壓:4.5 V ~ 5.5 V 工作溫度:0°C ~ 70°C 安裝類型:表面貼裝 封裝/外殼:64-LQFP 供應(yīng)商設(shè)備封裝:64-TQFP(10x10) 包裝:托盤 其它名稱:72225LB10TF |

| IDT72225LB25PF | 功能描述:IC FIFO 1024X18 SYNC 25NS 64TQFP RoHS:否 類別:集成電路 (IC) >> 邏輯 - FIFO 系列:7200 標(biāo)準(zhǔn)包裝:80 系列:7200 功能:同步 存儲容量:18.4K(1K x 18) 數(shù)據(jù)速率:- 訪問時間:10ns 電源電壓:4.5 V ~ 5.5 V 工作溫度:0°C ~ 70°C 安裝類型:表面貼裝 封裝/外殼:64-LQFP 供應(yīng)商設(shè)備封裝:64-TQFP(10x10) 包裝:托盤 其它名稱:72225LB10TF |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。