- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄377404 > IDT72225LB25G (INTEGRATED DEVICE TECHNOLOGY INC) CMOS SyncFIFOO 256 x 18, 512 x 18, 1024 x 18, 2048 x 18 and 4096 x 18 PDF資料下載

參數(shù)資料

| 型號(hào): | IDT72225LB25G |

| 廠商: | INTEGRATED DEVICE TECHNOLOGY INC |

| 元件分類: | DRAM |

| 英文描述: | CMOS SyncFIFOO 256 x 18, 512 x 18, 1024 x 18, 2048 x 18 and 4096 x 18 |

| 中文描述: | 1K X 18 OTHER FIFO, CPGA68 |

| 封裝: | CAVITY-UP, PGA-68 |

| 文件頁(yè)數(shù): | 7/16頁(yè) |

| 文件大?。?/td> | 181K |

| 代理商: | IDT72225LB25G |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)當(dāng)前第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)

7

IDT72205LB/72215LB/72225LB/72235LB/72245LB CMOS SyncFIFO

256 x 18-BIT, 512 x 18, 1,024 x 18, 2,048 x 18 and 4,096 x 18

Commercial And Industrial Temperature Ranges

When the

LD

pin is LOW and

WEN

is HIGH, the WCLK input

is disabled; then a signal at this input can neither increment the

write offset register pointer, nor execute a write.

The contents of the offset registers can be read on the

output lines when the

LD

pin is set LOW and

REN

is set LOW;

then, data can be read on the LOW-to-HIGH transition of the

read clock (RCLK). The act of reading the control registers

employs a dedicated read offset register pointer. (The read

and write pointers operate independently).

A read and a write should not be performed simultaneously

to the offset registers.

FIRST LOAD (

FL

is grounded to indicate operation in the Single Device or

Width Expansion mode. In the Depth Expansion configuration,

FL

is grounded to indicate it is the first device loaded and is set

to HIGH for all other devices in the Daisy Chain. (See Operating

Configurations for further details.)

FL

)

WRITE EXPANSION INPUT (

This is a dual purpose pin.

WXI

is grounded to indicate

operation in the Single Device or Width Expansion mode.

WXI

is connected to Write Expansion Out (

WXO

) of the previous

device in the Daisy Chain Depth Expansion mode.

WXI

)

READ EXPANSION INPUT (

This is a dual purpose pin.

RXI

is grounded to indicate

operation in the Single Device or Width Expansion mode.

RXI

is connected to Read Expansion Out (

RXO

) of the previous

device in the Daisy Chain Depth Expansion mode.

RXI

)

OUTPUTS:

FULL FLAG (

When the FIFO is full,

FF

will go LOW, inhibiting further

write operations. When

FF

is HIGH, the FIFO is not full. If no

reads are performed after a reset,

FF

will go LOW after D

writes to the FIFO.

D = 256 writes for the IDT72205LB, 512 for

the IDT72215LB, 1,024 for the IDT72225LB, 2,048 for the

IDT72235LB and 4,096 for the IDT72245LB.

The

FF

is updated on the LOW-to-HIGH transition of the

write clock (WCLK).

FF

)

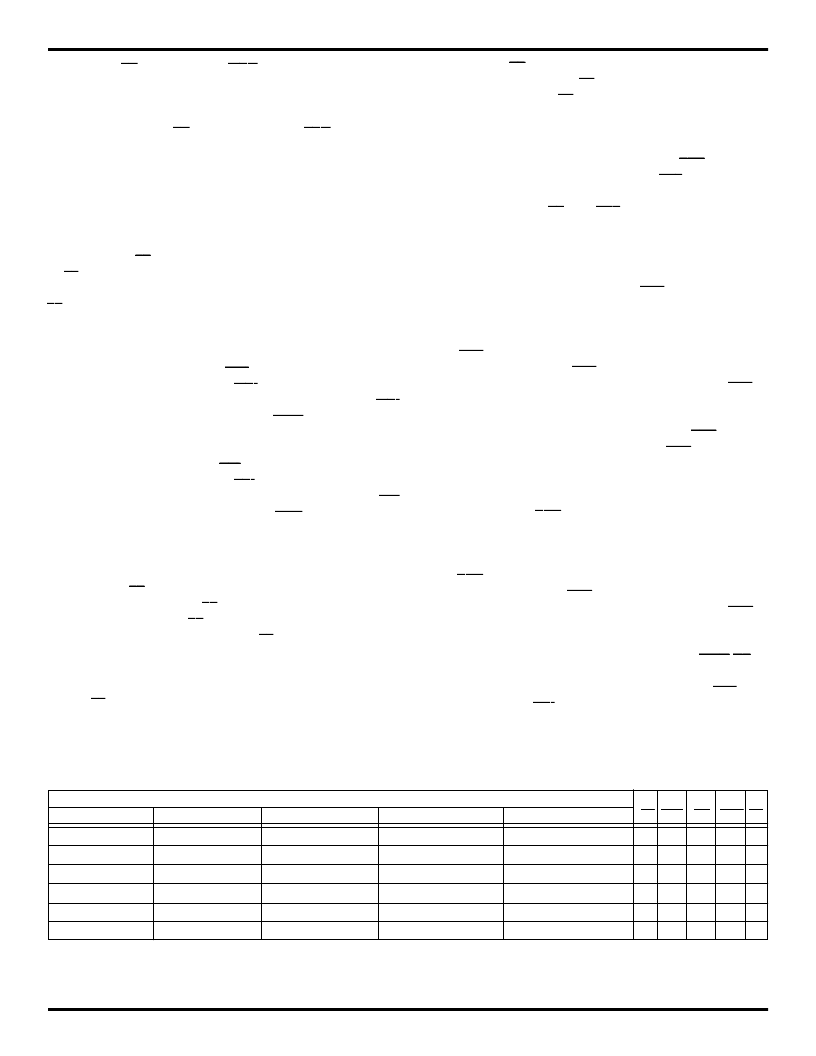

Number of Words in FIFO Memory

72225

72205

72215

72235

72245

FF PAF

HF

PAE

EF

0

0

0

0

0

H

H

H

H

H

L

H

H

H

H

L

L

H

H

H

L

L

L

L

L

H

H

H

H

L

H

H

H

H

H

1 to n

(1)

(n + 1) to 128

129 to (256-(m+1))

(256-m)

(2)

to 255

256

NOTES:

1. n = Empty Offset (Default Values : IDT72205 n=31, IDT72215 n = 63, IDT72225/72235/72245 n = 127)

2. m = Full Offset (Default Values : IDT72205 n=31, IDT72215 n = 63, IDT72225/72235/72245 n = 127)

1 to n

(1)

(n + 1) to 256

257 to (512-(m+1)) 513 to (1,024-(m+1)) 1,025 to (2,048-(m+1)) 2,049 to (4,096-(m+1))

(512-m)

(2)

to 511

(1,024-m)

(2)

to 1,023

(2,048-m)

(2)

to 2,047

512

1,024

1 to n

(1)

(n + 1) to 512

1 to n

(1)

1 to n

(1)

(n + 1) to 1,024

(n + 1) to 2,048

(4,096-m)

(2)

to 4,095

4,096

2,048

2766 tbl 09

TABLE I — STATUS FLAGS

EMPTY FLAG (

When the FIFO is

empty,

EF

will go LOW, inhibiting further

read operations. When

EF

is HIGH, the FIFO is not empty.

The EF is updated on the LOW-to-HIGH transition of the

read clock (RCLK).

EF

)

PROGRAMMABLE ALMOST-FULL FLAG (

The Programmable Almost-Full Flag (

PAF

) will go LOW

when FIFO reaches the Almost-Full condition. If no reads are

performed after Reset (

RS

), the

PAF

will go LOW after (256-m)

writes for the IDT72205LB, (512-m) writes for the IDT72215LB,

(1,024-m) writes for the IDT72225LB, (2,048–m) writes for the

IDT72235LB and (4,096–m) writes for the IDT72245LB. The

offset “m” is defined in the FULL offset register.

If there is no Full offset specified, the

PAF

will be LOW when

the device is 31 away from completely full for IDT72205LB, 63

away from completely full for IDT72215LB, and 127 away from

completely full for IDT72225LB/72235LB/72245LB.

The

PAF

is asserted LOW on the LOW-to-HIGH transition

of the write clock (WCLK).

PAF

is reset to HIGH on the LOW-

to-HIGH transition of the read clock (RCLK). Thus

PAF

is

asynchronous.

PAF

)

PROGRAMMABLE ALMOST-EMPTY FLAG (

The Programmable Almost-Empty Flag (

PAE

) will go LOW

when the read pointer is “n+1” locations less than the write

pointer. The offset “n” is defined in the EMPTY offset register.

If there is no Empty offset specified, the Programmable

Almost-Empty Flag (

PAE

) will be LOW when the device is 31

away from completely empty for IDT72205LB, 63 away from

completely empty for IDT72215LB, and 127 away from com-

pletely empty for IDT72225LB/72235LB/72245LB.

The

PAE

is asserted LOW on the LOW-to-HIGH transition

of the read clock (RCLK).

PAE

is reset to HIGH on the LOW-

to-HIGH transition of the write clock (WCLK). Thus

PAE

is

asynchronous.

PAE

)

WRITE EXPANSION OUT/HALF-FULL FLAG (

This is a dual-purpose output. In the Single Device and

Width Expansion mode, when Write Expansion In (

WXI

) and

Read Expansion In (

RXI

) are grounded, this output acts as an

indication of a half-full memory.

WXO

/

HF

)

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| IDT72225LB25J | CMOS SyncFIFOO 256 x 18, 512 x 18, 1024 x 18, 2048 x 18 and 4096 x 18 |

| IDT72225LB25TF | CMOS SyncFIFOO 256 x 18, 512 x 18, 1024 x 18, 2048 x 18 and 4096 x 18 |

| IDT72225LB25TFB | CMOS SyncFIFOO 256 x 18, 512 x 18, 1024 x 18, 2048 x 18 and 4096 x 18 |

| IDT72225LB25TFI | CMOS SyncFIFOO 256 x 18, 512 x 18, 1024 x 18, 2048 x 18 and 4096 x 18 |

| IDT72225LB35G | CMOS SyncFIFOO 256 x 18, 512 x 18, 1024 x 18, 2048 x 18 and 4096 x 18 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| IDT72225LB25J | 功能描述:IC FIFO 1024X18 SYNC 25NS 68PLCC RoHS:否 類別:集成電路 (IC) >> 邏輯 - FIFO 系列:7200 標(biāo)準(zhǔn)包裝:80 系列:7200 功能:同步 存儲(chǔ)容量:18.4K(1K x 18) 數(shù)據(jù)速率:- 訪問(wèn)時(shí)間:10ns 電源電壓:4.5 V ~ 5.5 V 工作溫度:0°C ~ 70°C 安裝類型:表面貼裝 封裝/外殼:64-LQFP 供應(yīng)商設(shè)備封裝:64-TQFP(10x10) 包裝:托盤 其它名稱:72225LB10TF |

| IDT72225LB25J8 | 功能描述:IC FIFO 1024X18 SYNC 25NS 68PLCC RoHS:否 類別:集成電路 (IC) >> 邏輯 - FIFO 系列:7200 標(biāo)準(zhǔn)包裝:80 系列:7200 功能:同步 存儲(chǔ)容量:18.4K(1K x 18) 數(shù)據(jù)速率:- 訪問(wèn)時(shí)間:10ns 電源電壓:4.5 V ~ 5.5 V 工作溫度:0°C ~ 70°C 安裝類型:表面貼裝 封裝/外殼:64-LQFP 供應(yīng)商設(shè)備封裝:64-TQFP(10x10) 包裝:托盤 其它名稱:72225LB10TF |

| IDT72225LB25JI | 功能描述:IC FIFO 1024X18 SYNC 25NS 68PLCC RoHS:否 類別:集成電路 (IC) >> 邏輯 - FIFO 系列:7200 標(biāo)準(zhǔn)包裝:80 系列:7200 功能:同步 存儲(chǔ)容量:18.4K(1K x 18) 數(shù)據(jù)速率:- 訪問(wèn)時(shí)間:10ns 電源電壓:4.5 V ~ 5.5 V 工作溫度:0°C ~ 70°C 安裝類型:表面貼裝 封裝/外殼:64-LQFP 供應(yīng)商設(shè)備封裝:64-TQFP(10x10) 包裝:托盤 其它名稱:72225LB10TF |

| IDT72225LB25JI8 | 功能描述:IC FIFO 1024X18 SYNC 25NS 68PLCC RoHS:否 類別:集成電路 (IC) >> 邏輯 - FIFO 系列:7200 標(biāo)準(zhǔn)包裝:80 系列:7200 功能:同步 存儲(chǔ)容量:18.4K(1K x 18) 數(shù)據(jù)速率:- 訪問(wèn)時(shí)間:10ns 電源電壓:4.5 V ~ 5.5 V 工作溫度:0°C ~ 70°C 安裝類型:表面貼裝 封裝/外殼:64-LQFP 供應(yīng)商設(shè)備封裝:64-TQFP(10x10) 包裝:托盤 其它名稱:72225LB10TF |

| IDT72225LB25PF | 功能描述:IC FIFO 1024X18 SYNC 25NS 64TQFP RoHS:否 類別:集成電路 (IC) >> 邏輯 - FIFO 系列:7200 標(biāo)準(zhǔn)包裝:80 系列:7200 功能:同步 存儲(chǔ)容量:18.4K(1K x 18) 數(shù)據(jù)速率:- 訪問(wèn)時(shí)間:10ns 電源電壓:4.5 V ~ 5.5 V 工作溫度:0°C ~ 70°C 安裝類型:表面貼裝 封裝/外殼:64-LQFP 供應(yīng)商設(shè)備封裝:64-TQFP(10x10) 包裝:托盤 其它名稱:72225LB10TF |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。