- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄10006 > IDT72261LA15PF8 (IDT, Integrated Device Technology Inc)IC FIFO 8192X18 LP 15NS 64QFP PDF資料下載

參數(shù)資料

| 型號: | IDT72261LA15PF8 |

| 廠商: | IDT, Integrated Device Technology Inc |

| 文件頁數(shù): | 26/27頁 |

| 文件大?。?/td> | 0K |

| 描述: | IC FIFO 8192X18 LP 15NS 64QFP |

| 標(biāo)準(zhǔn)包裝: | 750 |

| 系列: | 7200 |

| 功能: | 同步 |

| 存儲(chǔ)容量: | 144K(8K x 18) |

| 數(shù)據(jù)速率: | 67MHz |

| 訪問時(shí)間: | 15ns |

| 電源電壓: | 4.5 V ~ 5.5 V |

| 工作溫度: | 0°C ~ 70°C |

| 安裝類型: | 表面貼裝 |

| 封裝/外殼: | 64-LQFP |

| 供應(yīng)商設(shè)備封裝: | 64-TQFP(14x14) |

| 包裝: | 帶卷 (TR) |

| 其它名稱: | 72261LA15PF8 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁當(dāng)前第26頁第27頁

8

COMMERCIALANDINDUSTRIAL

TEMPERATURERANGES

IDT72261LA/72271LA SuperSync FIFO

16,384 x 9 and 32,768 x 9

NOTES:

1. n = Empty Offset, Default Values: n = 127 when parallel offset loading is selected or n = 1,023 when serial offset loading is selected.

2. m = Full Offset, Default Values: m = 127 when parallel offset loading is selected or m = 1,023 when serial offset loading is selected.

PROGRAMMING FLAG OFFSETS

Full and Empty Flag offset values are user programmable. The

IDT72261LA/72271LA has internal registers for these offsets. Default

settings are stated in the footnotes of Table 1 and Table 2. Offset values

can be programmed into the FIFO in one of two ways; serial or parallel

loading method. The selection of the loading method is done using the LD

(Load) pin. During Master Reset, the state of the LD input determines

whether serial or parallel flag offset programming is enabled. A HIGH on

LD during Master Reset selects serial loading of offset values and in

addition, sets a default PAE offset value of 3FFH (a threshold 1,023 words

from the empty boundary), and a default PAF offset value of 3FFH (a

threshold 1,023 words from the full boundary). A LOW on LD during Master

Reset selects parallel loading of offset values, and in addition, sets a

default PAE offset value of 07FH (a threshold 127 words from the empty

boundary), and a default PAF offset value of 07FH (a threshold 127 words

from the full boundary). See Figure 3, Offset Register Location and Default

Values.

In addition to loading offset values into the FIFO, it also possible to read

the current offset values. It is only possible to read offset values via parallel

read.

Figure 4, Programmable Flag Offset Programming Sequence, summa-

rizes the control pins and sequence for both serial and parallel program-

ming modes. For a more detailed description, see discussion that follows.

The offset registers may be programmed (and reprogrammed) any time

after Master Reset, regardless of whether serial or parallel programming

has been selected.

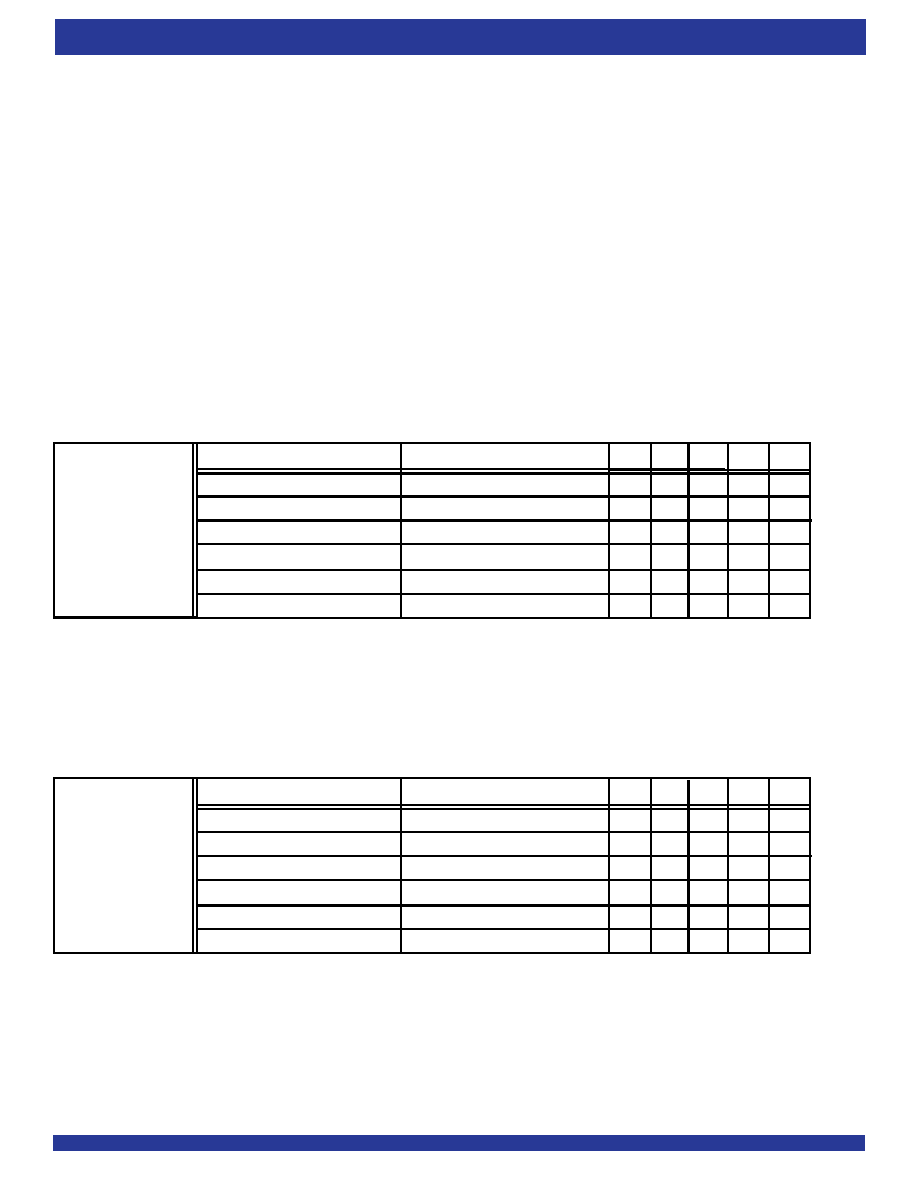

Number of

Words in

FIFO

0

1 to n (1)

0

1 to n (1)

(n+1) to 8,192

8,193 to (16,384-(m+1))

(16,384-m) (2) to 16,383

16,384

IDT72261LA

IDT72271LA

FF

PAF HF

PAE EF

HH

HL

L

HH

HL

H

HH

H

HH

L

H

HL

L

H

LL

LH

H

4671 drw 05

0

1 to n+1(1)

0

1 to n+1(1)

(n+2) to 16,385

16,386 to (32,769-(m+1))

(32,769-m)

(2)

to 32,768

32,769

IR

PAF HF

PAE OR

LH

H

L

H

LH

H

L

H

HHL

LH

L

H

L

LLL

H

L

HL

L

H

L

IDT72261LA

IDT72271LA

Number of

Words in

FIFO (1)

(n+1) to 16,384

16,385 to (32,768-(m+1))

(32,768-m) (2) to 32,767

32,768

(n+2) to 8,193

8,194 to (16,385-(m+1))

(16,385-m)

(2)

to 16,384

16,385

NOTES:

1. n = Empty Offset, Default Values: n = 127 when parallel offset loading is selected or n = 1,023 when serial offset loading is selected.

2. m = Full Offset, Default Values: m = 127 when parallel offset loading is selected or m = 1,023 when serial offset loading is selected.

TABLE 1 — STATUS FLAGS FOR IDT STANDARD MODE

TABLE 2 — STATUS FLAGS FOR IDT STANDARD MODE

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| LTC2847CUHF#TRPBF | IC TXRX MULTIPROTOCOL 38-QFN |

| IDT72255LA20PFI8 | IC FIFO 8KX18 LP 20NS 64QFP |

| VI-24Z-IV-B1 | CONVERTER MOD DC/DC 2V 60W |

| LTC2847CUHF#TR | IC TXRX MULTIPROTOCOL 38-QFN |

| VI-BNM-MX-B1 | CONVERTER MOD DC/DC 10V 75W |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| IDT72261LA15PFI | 功能描述:IC FIFO 8192X18 LP 15NS 64QFP RoHS:否 類別:集成電路 (IC) >> 邏輯 - FIFO 系列:7200 標(biāo)準(zhǔn)包裝:90 系列:7200 功能:同步 存儲(chǔ)容量:288K(16K x 18) 數(shù)據(jù)速率:100MHz 訪問時(shí)間:10ns 電源電壓:4.5 V ~ 5.5 V 工作溫度:0°C ~ 70°C 安裝類型:表面貼裝 封裝/外殼:64-LQFP 供應(yīng)商設(shè)備封裝:64-TQFP(14x14) 包裝:托盤 其它名稱:72271LA10PF |

| IDT72261LA15PFI8 | 功能描述:IC FIFO 8192X18 LP 15NS 64QFP RoHS:否 類別:集成電路 (IC) >> 邏輯 - FIFO 系列:7200 標(biāo)準(zhǔn)包裝:90 系列:7200 功能:同步 存儲(chǔ)容量:288K(16K x 18) 數(shù)據(jù)速率:100MHz 訪問時(shí)間:10ns 電源電壓:4.5 V ~ 5.5 V 工作溫度:0°C ~ 70°C 安裝類型:表面貼裝 封裝/外殼:64-LQFP 供應(yīng)商設(shè)備封裝:64-TQFP(14x14) 包裝:托盤 其它名稱:72271LA10PF |

| IDT72261LA15TF | 功能描述:IC FIFO 8192X18 LP 15NS 64QFP RoHS:否 類別:集成電路 (IC) >> 邏輯 - FIFO 系列:7200 標(biāo)準(zhǔn)包裝:90 系列:7200 功能:同步 存儲(chǔ)容量:288K(16K x 18) 數(shù)據(jù)速率:100MHz 訪問時(shí)間:10ns 電源電壓:4.5 V ~ 5.5 V 工作溫度:0°C ~ 70°C 安裝類型:表面貼裝 封裝/外殼:64-LQFP 供應(yīng)商設(shè)備封裝:64-TQFP(14x14) 包裝:托盤 其它名稱:72271LA10PF |

| IDT72261LA15TF8 | 功能描述:IC FIFO 8192X18 LP 15NS 64QFP RoHS:否 類別:集成電路 (IC) >> 邏輯 - FIFO 系列:7200 標(biāo)準(zhǔn)包裝:90 系列:7200 功能:同步 存儲(chǔ)容量:288K(16K x 18) 數(shù)據(jù)速率:100MHz 訪問時(shí)間:10ns 電源電壓:4.5 V ~ 5.5 V 工作溫度:0°C ~ 70°C 安裝類型:表面貼裝 封裝/外殼:64-LQFP 供應(yīng)商設(shè)備封裝:64-TQFP(14x14) 包裝:托盤 其它名稱:72271LA10PF |

| IDT72261LA15TFGI | 功能描述:IC FIFO 8192X18 LP 15NS 64QFP RoHS:是 類別:集成電路 (IC) >> 邏輯 - FIFO 系列:7200 標(biāo)準(zhǔn)包裝:90 系列:7200 功能:同步 存儲(chǔ)容量:288K(16K x 18) 數(shù)據(jù)速率:100MHz 訪問時(shí)間:10ns 電源電壓:4.5 V ~ 5.5 V 工作溫度:0°C ~ 70°C 安裝類型:表面貼裝 封裝/外殼:64-LQFP 供應(yīng)商設(shè)備封裝:64-TQFP(14x14) 包裝:托盤 其它名稱:72271LA10PF |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。