- 您現(xiàn)在的位置:買(mǎi)賣IC網(wǎng) > PDF目錄9999 > IDT72V255LA15PFI8 (IDT, Integrated Device Technology Inc)IC FIFO SS 8192X18 15NS 64-TQFP PDF資料下載

參數(shù)資料

| 型號(hào): | IDT72V255LA15PFI8 |

| 廠商: | IDT, Integrated Device Technology Inc |

| 文件頁(yè)數(shù): | 12/27頁(yè) |

| 文件大小: | 0K |

| 描述: | IC FIFO SS 8192X18 15NS 64-TQFP |

| 標(biāo)準(zhǔn)包裝: | 750 |

| 系列: | 72V |

| 功能: | 同步 |

| 存儲(chǔ)容量: | 144K(8K x 18) |

| 訪問(wèn)時(shí)間: | 15ns |

| 電源電壓: | 3 V ~ 3.6 V |

| 工作溫度: | -40°C ~ 85°C |

| 安裝類型: | 表面貼裝 |

| 封裝/外殼: | 64-LQFP |

| 供應(yīng)商設(shè)備封裝: | 64-TQFP(14x14) |

| 包裝: | 帶卷 (TR) |

| 其它名稱: | 72V255LA15PFI8 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)當(dāng)前第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)

2

IDT72V255LA/72V265LA 3.3 VOLT CMOS SuperSync FIFO

8,192 x 18, 16,384 x 18

COMMERCIAL AND INDUSTRIAL

TEMPERATURE RANGES

OCTOBER 22, 2008

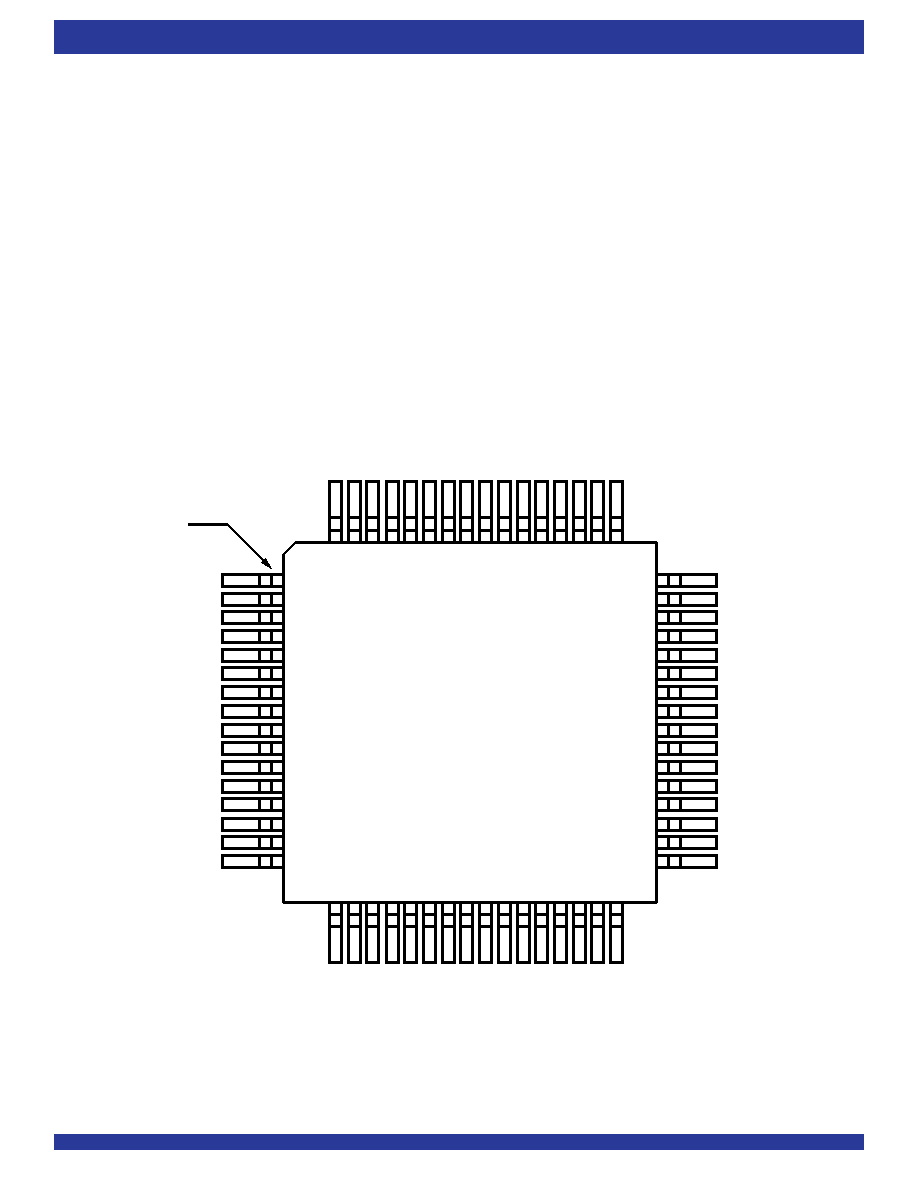

PIN CONFIGURATIONS

TQFP (PN64-1, ORDER CODE: PF)

STQFP (PP64-1, ORDER CODE: TF)

TOP VIEW

DESCRIPTION (CONTINUED)

PIN 1

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

WEN

SEN

DC(1)

VCC

GND

D17

D16

D15

D14

D13

D12

D11

D10

D9

D8

D7

64 63 62 61 60 59 58 57 56 55 54 53 52 51 50 49

17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32

Q17

Q16

GND

Q15

Q14

VCC

Q13

Q12

Q11

GND

Q10

Q9

Q8

Q7

Q6

GND

WCLK

PRS

MRS

LD

FWFT/SI

GND

FF

/IR

PAF

HF

V

CC

PAE

EF

/OR

RCLK

REN

RT

OE

Q5

Q4

V

CC

Q3

Q2

GND

Q1

Q0

GND

D0

D1

D2

D3

D4

D5

D6

4672 drw 02

The period required by the retransmit operation is now fixed and short.

The first word data latency period, from the time the first word is written to

anemptyFIFOtothetimeitcanberead,isnowfixedandshort. (Thevariable

clock cycle counting delay associated with the latency period found on

previous SuperSync devices has been eliminated on this SuperSync

family.)

SuperSync FIFOs are particularly appropriate for networking, video,

telecommunications,datacommunicationsandotherapplicationsthatneedto

buffer large amounts of data.

TheinputportiscontrolledbyaWriteClock(WCLK)inputandaWriteEnable

(

WEN)input. DataiswrittenintotheFIFOoneveryrisingedgeofWCLKwhen

WEN is asserted. The output port is controlled by a Read Clock (RCLK) input

and Read Enable (

REN) input. Data is read from the FIFO on every rising

edgeofRCLKwhen

RENisasserted. AnOutputEnable(OE)inputisprovided

for three-state control of the outputs.

The frequencies of both the RCLK and the WCLK signals may vary from 0

to fMAX with complete independence. There are no restrictions on the

frequency of one clock input with respect to the other.

NOTE:

1. DC = Don’t Care. Must be tied to GND or VCC, cannot be left open.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| IDT72V255LA10PFG8 | IC FIFO SS 8192X18 10NS 64-TQFP |

| ISL26313FBZ-T | IC ADC 12BIT SPI/SRL 125K 8SOIC |

| VI-B4Y-IU-F2 | CONVERTER MOD DC/DC 3.3V 132W |

| XRT73LC00AIV | IC LIU STS1/DS3/E3 SGL 44TQFP |

| VI-B4Y-IU-F1 | CONVERTER MOD DC/DC 3.3V 132W |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| IDT72V255LA15TF | 功能描述:IC FIFO SS 8192X18 15NS 64-STQFP RoHS:否 類別:集成電路 (IC) >> 邏輯 - FIFO 系列:72V 標(biāo)準(zhǔn)包裝:90 系列:7200 功能:同步 存儲(chǔ)容量:288K(16K x 18) 數(shù)據(jù)速率:100MHz 訪問(wèn)時(shí)間:10ns 電源電壓:4.5 V ~ 5.5 V 工作溫度:0°C ~ 70°C 安裝類型:表面貼裝 封裝/外殼:64-LQFP 供應(yīng)商設(shè)備封裝:64-TQFP(14x14) 包裝:托盤(pán) 其它名稱:72271LA10PF |

| IDT72V255LA15TF8 | 功能描述:IC FIFO SS 8192X18 15NS 64-STQFP RoHS:否 類別:集成電路 (IC) >> 邏輯 - FIFO 系列:72V 標(biāo)準(zhǔn)包裝:90 系列:7200 功能:同步 存儲(chǔ)容量:288K(16K x 18) 數(shù)據(jù)速率:100MHz 訪問(wèn)時(shí)間:10ns 電源電壓:4.5 V ~ 5.5 V 工作溫度:0°C ~ 70°C 安裝類型:表面貼裝 封裝/外殼:64-LQFP 供應(yīng)商設(shè)備封裝:64-TQFP(14x14) 包裝:托盤(pán) 其它名稱:72271LA10PF |

| IDT72V255LA15TFGI | 制造商:Integrated Device Technology Inc 功能描述:IC FIFO SS 8192X18 15NS 64-STQFP |

| IDT72V255LA15TFGI8 | 制造商:Integrated Device Technology Inc 功能描述:IC FIFO SS 8192X18 15NS 64-STQFP |

| IDT72V255LA15TFI | 功能描述:IC FIFO SS 8192X18 15NS 64-STQFP RoHS:否 類別:集成電路 (IC) >> 邏輯 - FIFO 系列:72V 標(biāo)準(zhǔn)包裝:90 系列:7200 功能:同步 存儲(chǔ)容量:288K(16K x 18) 數(shù)據(jù)速率:100MHz 訪問(wèn)時(shí)間:10ns 電源電壓:4.5 V ~ 5.5 V 工作溫度:0°C ~ 70°C 安裝類型:表面貼裝 封裝/外殼:64-LQFP 供應(yīng)商設(shè)備封裝:64-TQFP(14x14) 包裝:托盤(pán) 其它名稱:72271LA10PF |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。