- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄10011 > IDT72V3650L15PF8 (IDT, Integrated Device Technology Inc)IC FIFO SS 2048X36 15NS 128-TQFP PDF資料下載

參數(shù)資料

| 型號: | IDT72V3650L15PF8 |

| 廠商: | IDT, Integrated Device Technology Inc |

| 文件頁數(shù): | 43/46頁 |

| 文件大小: | 0K |

| 描述: | IC FIFO SS 2048X36 15NS 128-TQFP |

| 標(biāo)準(zhǔn)包裝: | 1,000 |

| 系列: | 72V |

| 功能: | 異步,同步 |

| 存儲容量: | 72K(2K x 36) |

| 數(shù)據(jù)速率: | 67MHz |

| 訪問時間: | 15ns |

| 電源電壓: | 3.15 V ~ 3.45 V |

| 工作溫度: | 0°C ~ 70°C |

| 安裝類型: | 表面貼裝 |

| 封裝/外殼: | 128-LQFP |

| 供應(yīng)商設(shè)備封裝: | 128-TQFP(14x20) |

| 包裝: | 帶卷 (TR) |

| 其它名稱: | 72V3650L15PF8 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁當(dāng)前第43頁第44頁第45頁第46頁

6

COMMERCIAL AND INDUSTRIAL

TEMPERATURE RANGES

IDT72V3640/50/60/70/80/90 3.3V HIGH DENSITY SUPERSYNC IITM 36-BIT FIFO

1,024 x 36, 2,048 x 36, 4,096 x 36, 8,192 x 36, 16,384 x 36 and 32,768 x 36

OCTOBER 22, 2008

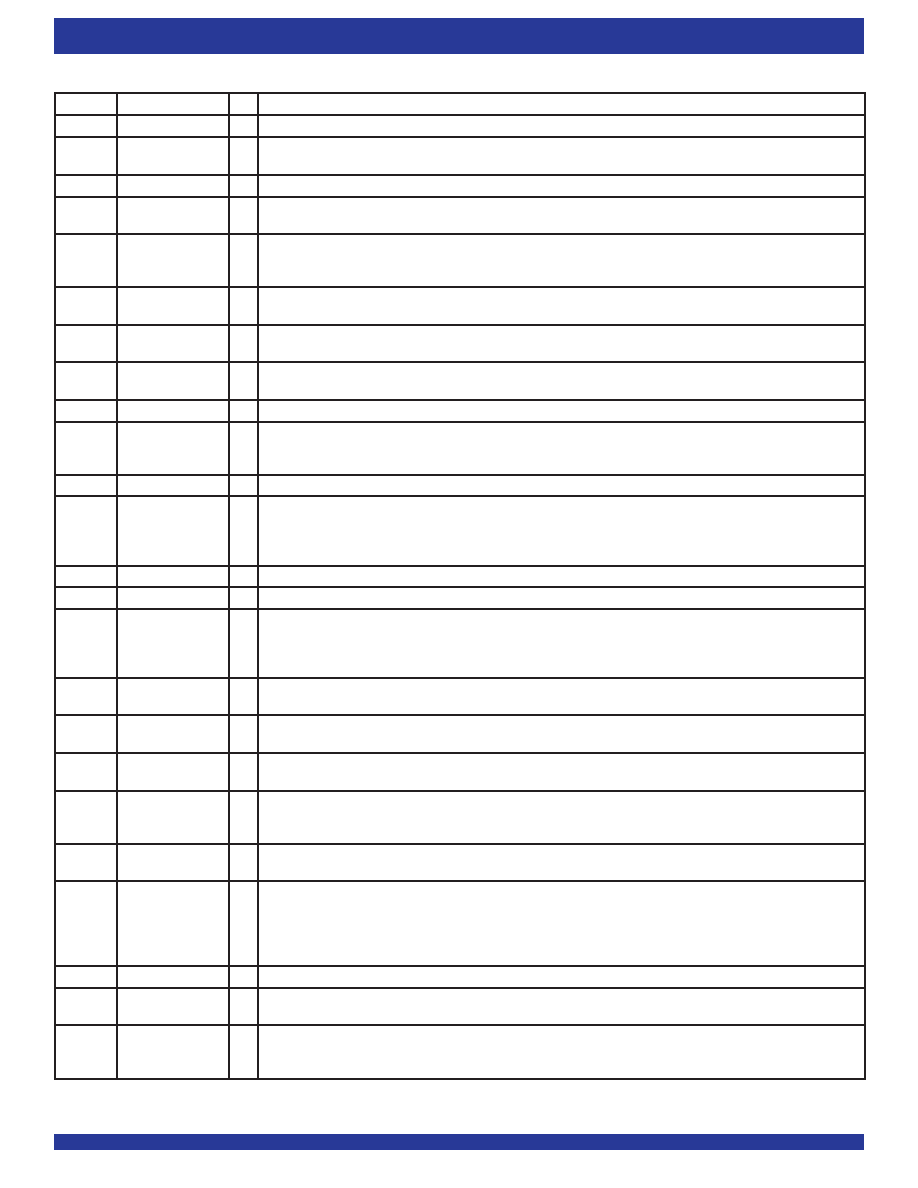

PIN DESCRIPTION (TQFP AND PBGA PACKAGES)

Symbol

Name

I/O

Description

BM(1)

Bus-Matching

I

BM works with IW and OW to select the bus sizes for both write and read ports. See Table 1 for bus size configuration.

BE(1)

Big-Endian/

I

During Master Reset, a LOW on

BE will select Big-Endian operation. A HIGH on BE during Master Reset will

Little-Endian

selectLittle-Endianformat.

D0–D35

DataInputs

I

Data inputs for a 36-, 18- or 9-bit bus. When in 18- or 9-bit mode, the unused input pins are in a don’t care state.

EF/OR

Empty Flag/

O

In the IDT Standard mode, the

EF function is selected. EF indicates whether or not the FIFO memory is empty.

Output Ready

In FWFT mode, the

OR functionisselected.OR indicateswhetherornotthereisvaliddataavailableattheoutputs.

FF/IR

Full Flag/

O

In the IDT Standard mode, the

FF function is selected. FF indicates whether or not the FIFO memory is full. In the

Input Ready

FWFT mode, the

IR function is selected. IR indicates whether or not there is space available for writing to the FIFO

memory.

FSEL0(1)

Flag Select Bit 0

I

DuringMasterReset,thisinputalongwithFSEL1andthe

LDpin,willselectthedefaultoffsetvaluesfortheprogrammable

flags

PAE and PAF. There are up to eight possible settings available.

FSEL1(1)

Flag Select Bit 1

I

DuringMasterReset,thisinputalongwithFSEL0andthe

LDpinwillselectthedefaultoffsetvaluesfortheprogrammable

flags

PAE and PAF. There are up to eight possible settings available.

FWFT/SI

First Word Fall

I

During Master Reset, selects First Word Fall Through or IDT Standard mode. After Master Reset, this pin functions

Through/Serial In

as a serial input for loading offset registers.

HF

Half-Full Flag

O

HF indicates whether the FIFO memory is more or less than half-full.

IP(1)

Interspersed Parity

I

During Master Reset, a LOW on IP will select Non-Interspersed Parity mode. A HIGH will select Interspersed Parity

mode. Interspersed Parity control only has an effect during parallel programming of the offset registers. It does not

effect the data written to and read from the FIFO.

IW(1)

InputWidth

I

This pin, along with OW and MB, selects the bus width of the write port. See Table 1 for bus size configuration.

LD

Load

I

This is a dual purpose pin. During Master Reset, the state of the

LD inputalongwithFSEL0andFSEL1,determines

oneofeightdefaultoffsetvaluesforthe

PAEandPAFflags,alongwiththemethodbywhichtheseoffsetregisterscan

be programmed, parallel or serial (see Table 2). After Master Reset, this pin enables writing to and reading from the

offsetregisters.

OE

OutputEnable

I

OE controls the output impedance of Qn.

OW(1)

OutputWidth

I

This pin, along with IW and BM, selects the bus width of the read port. See Table 1 for bus size configuration.

MRS

Master Reset

I

MRS initializes the read and write pointers to zero and sets the output register to all zeroes. During Master Reset,

theFIFOisconfiguredforeitherFWFTorIDTStandardmode,Bus-Matchingconfigurations,oneofeightprogammable

flagdefaultsettings,serialorparallelprogrammingoftheoffsetsettings,Big-Endian/Little-Endianformat,zerolatency

timing mode, interspersed parity, and synchronous versus asynchronous programmable flag timing modes.

PAE

Programmable

O

PAE goes LOW if the number of words in the FIFO memory is less than offset n, which is stored in the Empty Offset

Almost-EmptyFlag

register.

PAE goes HIGH if the number of words in the FIFO memory is greater than or equal to offset n.

PAF

Programmable

O

PAF goes HIGH if the number of free locations in the FIFO memory is more than offset m, which is stored in the

Almost-FullFlag

Full Offset register.

PAF goes LOW if the number of free locations in the FIFO memory is less than or equal to m.

PFM(1)

Programmable

I

During Master Reset, a LOW on PFM will select Asynchronous Programmable flag timing mode. A HIGH on PFM

Flag Mode

will select Synchronous Programmable flag timing mode.

PRS

PartialReset

I

PRS initializes the read and write pointers to zero and sets the output register to all zeroes. During Partial Reset,

the existing mode (IDT or FWFT), programming method (serial or parallel), and programmable flag settings are all

retained.

Q0–Q35

DataOutputs

O

Data outputs for an 36-, 18- or 9-bit bus. When in 18- or 9-bit mode, the unused output pins are in a don’t care

state. Outputs are not 5V tolerant regardless of the state of

OE.

RCLK/

Read Clock/

I

If Synchronous operation of the read port has been selected, when enabled by

REN, the rising edge of RCLK

RD

Read Strobe

reads data from the FIFO memory and offsets from the programmable registers. If

LD is LOW, the values loaded

into the offset registers is output on a rising edge of RCLK.If Asynchronous operation of the read port has been

selected, a rising edge on RD reads data from the FIFO in an Asynchronous manner.

REN should be tied LOW.

Asynchronous operation of the RCLK/RD input is only available in the PBGA package.

REN

Read Enable

I

REN enables RCLK for reading data from the FIFO memory and offset registers.

RM(1)

RetransmitTiming

I

During Master Reset, a LOW on RM will select zero latency Retransmit timing Mode. A HIGH on RM will select

Mode

normal latency mode.

RT

Retransmit

I

RT asserted on the rising edge of RCLK initializes the READ pointer to zero, sets the EF flag to LOW (OR to HIGH

in FWFT mode) and does not disturb the write pointer, programming method, existing timing mode or programmable

flag settings.

RT is useful to reread data from the first physical location of the FIFO.

NOTE:

1. Inputs should not change state after Master Reset.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MS27467E17B35SB | CONN PLUG 55POS STRAIGHT W/SCKT |

| LTC1350IG#PBF | IC TXRX 3.3V EIA/TIA-562 28-SSOP |

| VI-B3B-MX-B1 | CONVERTER MOD DC/DC 95V 75W |

| VE-B6P-IV-F1 | CONVERTER MOD DC/DC 13.8V 150W |

| IDT72V3631L15PF8 | IC SYNCFIFO 512X36 15NS 120-TQFP |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| IDT72V3650L15PFI | 功能描述:IC FIFO SS 2048X36 15NS 128-TQFP RoHS:否 類別:集成電路 (IC) >> 邏輯 - FIFO 系列:72V 標(biāo)準(zhǔn)包裝:90 系列:7200 功能:同步 存儲容量:288K(16K x 18) 數(shù)據(jù)速率:100MHz 訪問時間:10ns 電源電壓:4.5 V ~ 5.5 V 工作溫度:0°C ~ 70°C 安裝類型:表面貼裝 封裝/外殼:64-LQFP 供應(yīng)商設(shè)備封裝:64-TQFP(14x14) 包裝:托盤 其它名稱:72271LA10PF |

| IDT72V3650L15PFI8 | 功能描述:IC FIFO SS 2048X36 15NS 128-TQFP RoHS:否 類別:集成電路 (IC) >> 邏輯 - FIFO 系列:72V 標(biāo)準(zhǔn)包裝:90 系列:7200 功能:同步 存儲容量:288K(16K x 18) 數(shù)據(jù)速率:100MHz 訪問時間:10ns 電源電壓:4.5 V ~ 5.5 V 工作溫度:0°C ~ 70°C 安裝類型:表面貼裝 封裝/外殼:64-LQFP 供應(yīng)商設(shè)備封裝:64-TQFP(14x14) 包裝:托盤 其它名稱:72271LA10PF |

| IDT72V3650L6BB | 功能描述:IC FIFO SS 2048X36 6NS 144-BGA RoHS:否 類別:集成電路 (IC) >> 邏輯 - FIFO 系列:72V 標(biāo)準(zhǔn)包裝:90 系列:7200 功能:同步 存儲容量:288K(16K x 18) 數(shù)據(jù)速率:100MHz 訪問時間:10ns 電源電壓:4.5 V ~ 5.5 V 工作溫度:0°C ~ 70°C 安裝類型:表面貼裝 封裝/外殼:64-LQFP 供應(yīng)商設(shè)備封裝:64-TQFP(14x14) 包裝:托盤 其它名稱:72271LA10PF |

| IDT72V3650L6BB8 | 功能描述:IC FIFO SS 2048X36 6NS 144-BGA RoHS:否 類別:集成電路 (IC) >> 邏輯 - FIFO 系列:72V 標(biāo)準(zhǔn)包裝:90 系列:7200 功能:同步 存儲容量:288K(16K x 18) 數(shù)據(jù)速率:100MHz 訪問時間:10ns 電源電壓:4.5 V ~ 5.5 V 工作溫度:0°C ~ 70°C 安裝類型:表面貼裝 封裝/外殼:64-LQFP 供應(yīng)商設(shè)備封裝:64-TQFP(14x14) 包裝:托盤 其它名稱:72271LA10PF |

| IDT72V3650L6PF | 功能描述:IC FIFO SS 2048X36 6NS 128-TQFP RoHS:否 類別:集成電路 (IC) >> 邏輯 - FIFO 系列:72V 標(biāo)準(zhǔn)包裝:90 系列:7200 功能:同步 存儲容量:288K(16K x 18) 數(shù)據(jù)速率:100MHz 訪問時間:10ns 電源電壓:4.5 V ~ 5.5 V 工作溫度:0°C ~ 70°C 安裝類型:表面貼裝 封裝/外殼:64-LQFP 供應(yīng)商設(shè)備封裝:64-TQFP(14x14) 包裝:托盤 其它名稱:72271LA10PF |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。