- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄360859 > IMST414B-J20S Peripheral IC PDF資料下載

參數(shù)資料

| 型號(hào): | IMST414B-J20S |

| 英文描述: | Peripheral IC |

| 中文描述: | 外圍芯片 |

| 文件頁數(shù): | 6/74頁 |

| 文件大小: | 563K |

| 代理商: | IMST414B-J20S |

第1頁第2頁第3頁第4頁第5頁當(dāng)前第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁

IMS T400

/ 74

6

3

System services

System services include allthe necessarylogic to initialiseand sustain operationof the device.They also

include error handling and analysis facilities.

3.1

Power

Powerissupplied tothedeviceviathe

VDD

and

GND

pins.Severalofeachareprovidedtominimiseinduc-

tance within the package. All supply pins must be connected. The supply must be decoupled close to the

chip by at least one 100 nF low inductance (e.g. ceramic) capacitor between

VDD

and

GND

. Four layer

boards are recommended; if two layer boards are used, extra care should be taken in decoupling.

Input voltages must not exceed specification with respect to

VDD

and

GND

, even during power-up and

power-down ramping, otherwise latchupcan occur.CMOS devices can be permanently damagedby ex-

cessive periods of latchup.

3.2

CapPlus, CapMinus

The internally derived power supply for internal clocks requires an external low leakage, low inductance

1 F capacitor to be connected between

CapPlus

and

CapMinus

. A ceramic capacitor is preferred, with

an impedance less than 3 Ohmsbetween 100KHz and10 MHz. If a polarisedcapacitor is usedthe nega-

tive terminal should be connected to

CapMinus

. TotalPCB track length should be less than 50 mm. The

connections must not touch power supplies or other noise sources.

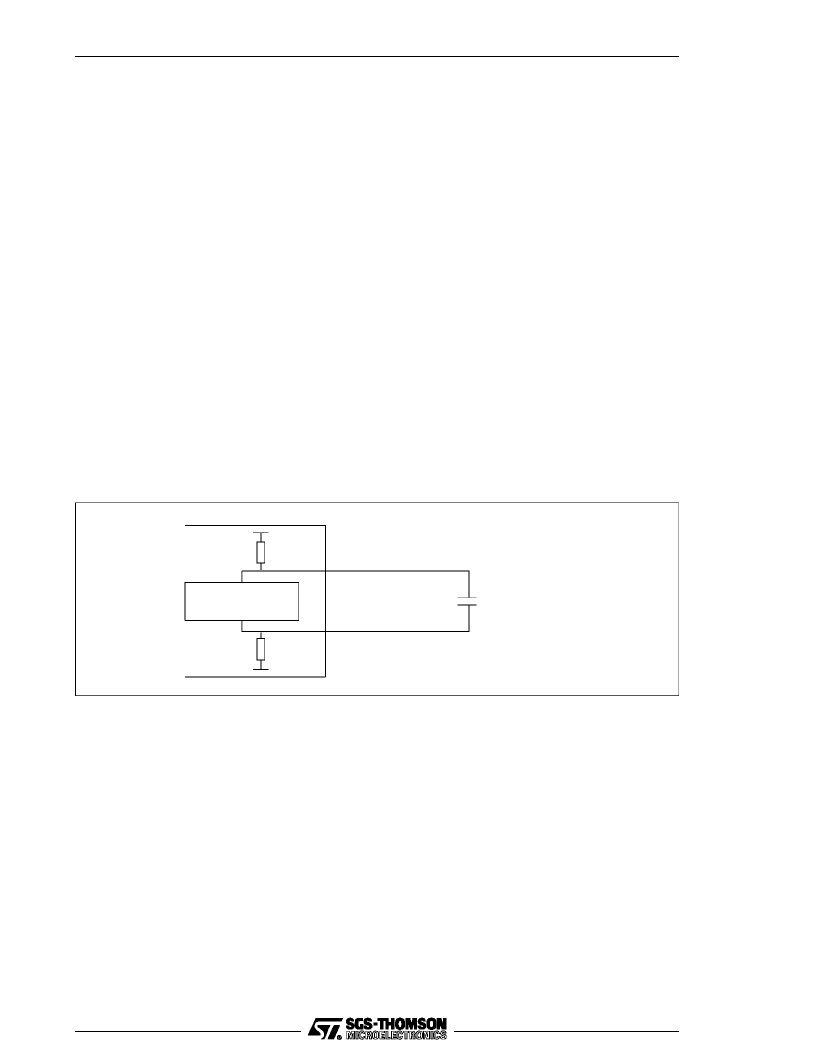

Phase–locked

loops

VDD

GND

CapPlus

CapMinus

P.C.B track

P.C.B track

Decoupling

capacitor 1 F

Figure 3.1

Recommended PLL decoupling

3.3

ClockIn

Transputerfamily componentsusea standard clockfrequency,supplied bythe useronthe

ClockIn

input.

The nominal frequency of this clock for all transputer family components is 5 MHz, regardless of device

type, transputer word length or processor cycle time. High frequency internal clocks are derived from

ClockIn

, simplifying system design and avoiding problems of distributing high speed clocks externally.

A number of transputer devicesmay beconnected toa commonclock,or mayhave individual clocks pro-

vidingeach onemeetsthespecifiedstabilitycriteria.In a multi-clocksystem therelativephasing of

Clock-

In

clocks is not important, due to the asynchronous nature of the links. Mark/space ratio is unimportant

provided the specified limits of

ClockIn

pulse widths are met.

Oscillator stability is important.

ClockIn

must be derived from a crystal oscillator; RC oscillators are not

sufficiently stable.

ClockIn

must not be distributed through a long chain of buffers.Clock edgesmust be

monotonic and remain within the specified voltage and time limits.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| IMST425-G17M | 32-Bit Microprocessor |

| IMST425G17S | Peripheral IC |

| IMST425-G17S | 32-Bit Microprocessor |

| IMST425-G20M | 32-Bit Microprocessor |

| IMST425G20S | Peripheral IC |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| IMST425-G17M | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:32-Bit Microprocessor |

| IMST425G17S | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Peripheral IC |

| IMST425-G17S | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:32-Bit Microprocessor |

| IMST425-G20M | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:32-Bit Microprocessor |

| IMST425G20S | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Peripheral IC |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。