- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄360859 > IMST425G25S Peripheral IC PDF資料下載

參數(shù)資料

| 型號: | IMST425G25S |

| 英文描述: | Peripheral IC |

| 中文描述: | 外圍芯片 |

| 文件頁數(shù): | 26/74頁 |

| 文件大小: | 563K |

| 代理商: | IMST425G25S |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁當(dāng)前第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁

IMS T400

/ 74

26

5.5

Memory refresh

The

RefreshPending

pin is asserted high when the external memory interface is about to perform a re-

fresh cycle. It remains high until the refresh cycle is started by the transputer. The mimimum time for the

RefreshPending

pin to be high is for one cycle of

ProcClockOut

(two periods

Tm

), when the EMI was

notabouttoperforma memoryreadorwrite.IftheEMIwasheldinthetristatecondition with

MemGranted

asserted, then

RefreshPending

will beassertedwhentherefresh controllerintheEMI isreadytoperform

a refresh.

MemReq

maybe re-asserted any timeafter the commencementof the refresh cycle.

Refresh-

Pending

changesstatenear therising edgeof

ProcClockOut

andcantherefore besampledby thefalling

edge of

ProcClockOut

.

If no DMA is active then refresh will be performed following the end of the current internal or external

memory cycle. If DMA is active the transputer will wait for DMA to terminate before commencing the re-

fresh cycle. Unlike

MemnotRfD1

,

RefreshPending

is nevertristated and can thusbeinterrogated by the

DMA device; theDMA cycle can then be suspended, at the discretionof the DMAdevice, to allow refresh

to take place.

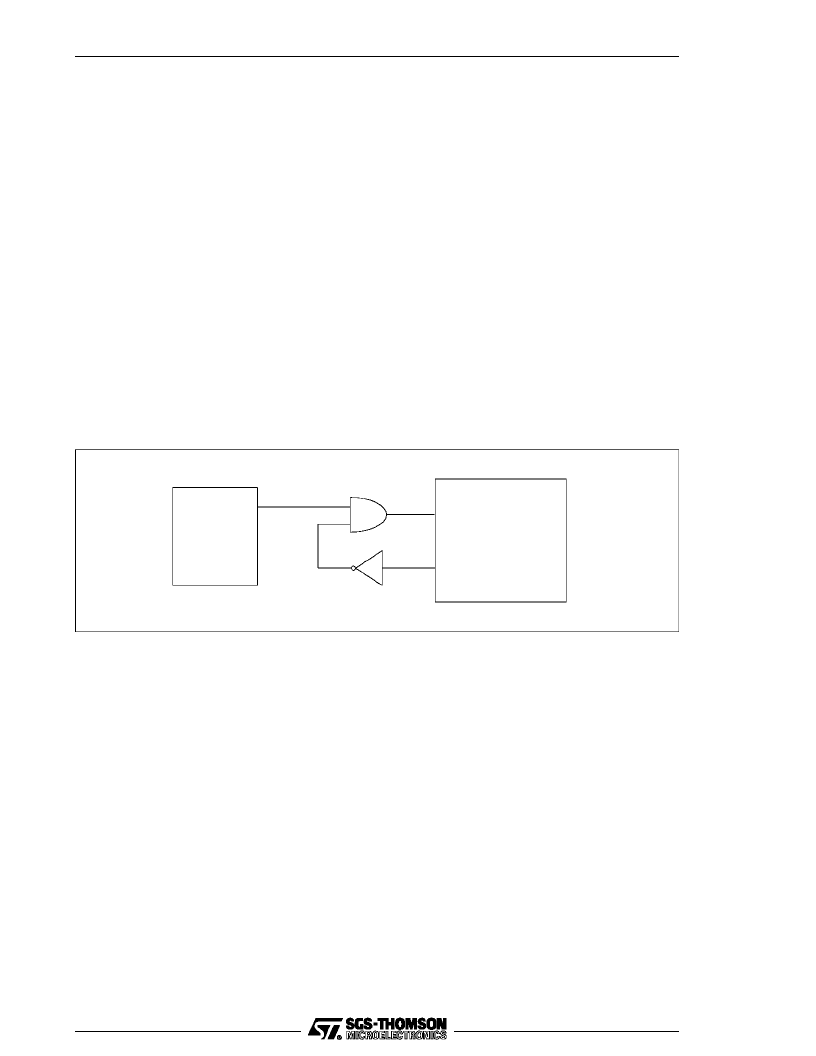

The simple circuitof Figure 5.10 will suspend DMArequests from theexternal logic when

RefreshPend-

ing

is asserted, so that a memory refresh cycle can be performed. DMA is restored on completion of the

refresh cycle. The transputer will not perform an external memory cycle other than a refresh cycle, using

this method, until the requesting device removes its DMA request.

IMS T400

Logic

DMA Request

RefreshPending

MemReq

Figure 5.10

IMS T400 refresh with DMA

When refresh is disabled no refresh cycles occur. During the post-

Reset

period eight dummy refresh

cycles will occur with the appropriate timing but with no bus or strobe activity.

A refresh cycle uses the same basic external memory timing as a normal external memory cycle, except

that it starts two periods

Tm

before the start of

T1

. If a refresh cycle is due during an external memory

access, it will be delayed until the end of that external cycle. Twoextra periods

Tm

(periods

R

in the dia-

gram) will then be inserted between the end of

T6

of the external memory cycle and thestart of

T1

of the

refresh cycle itself. The refresh address and various external strobes become active approximately one

period

Tm

before

T1

. Bus signals are activeuntil the end of

T2

, whilst

notMemRf

remains activeuntil the

end of

T6

.

For a refresh cycle,

MemnotRfD1

goes lowwhen

notMemRf

goes lowand

MemnotWrD0

goeshigh with

the sametiming as

MemnotRfD1

.All the addresslinesshare the sametiming, butonly

MemAD2-11

give

the refresh address.

MemAD12-30

stay high during the address period, whilst

MemAD31

remains low.

Refresh cycles generatestrobes

notMemS0-4

with timingas for anormal externalcycle, but

notMemRd

and

notMemWrB0-3

remain high.

MemWait

operates normally during refresh cycles.

Refresh cycles donot interruptinternal memory accesses,although the internal addresses cannot be re-

flected on the external bus during refresh.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| IMST425-G25S | 32-Bit Microprocessor |

| IMST425G30S | Peripheral IC |

| IMST425J17S | Peripheral IC |

| IMST425-J17S | 32-Bit Microprocessor |

| IMST425J20S | Peripheral IC |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| IMST425-G25S | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:32-Bit Microprocessor |

| IMST425G30S | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Peripheral IC |

| IMST425J17S | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Peripheral IC |

| IMST425-J17S | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:32-Bit Microprocessor |

| IMST425J20S | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Peripheral IC |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。