- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄360859 > IMST425G25S Peripheral IC PDF資料下載

參數(shù)資料

| 型號: | IMST425G25S |

| 英文描述: | Peripheral IC |

| 中文描述: | 外圍芯片 |

| 文件頁數(shù): | 71/74頁 |

| 文件大小: | 563K |

| 代理商: | IMST425G25S |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁當(dāng)前第71頁第72頁第73頁第74頁

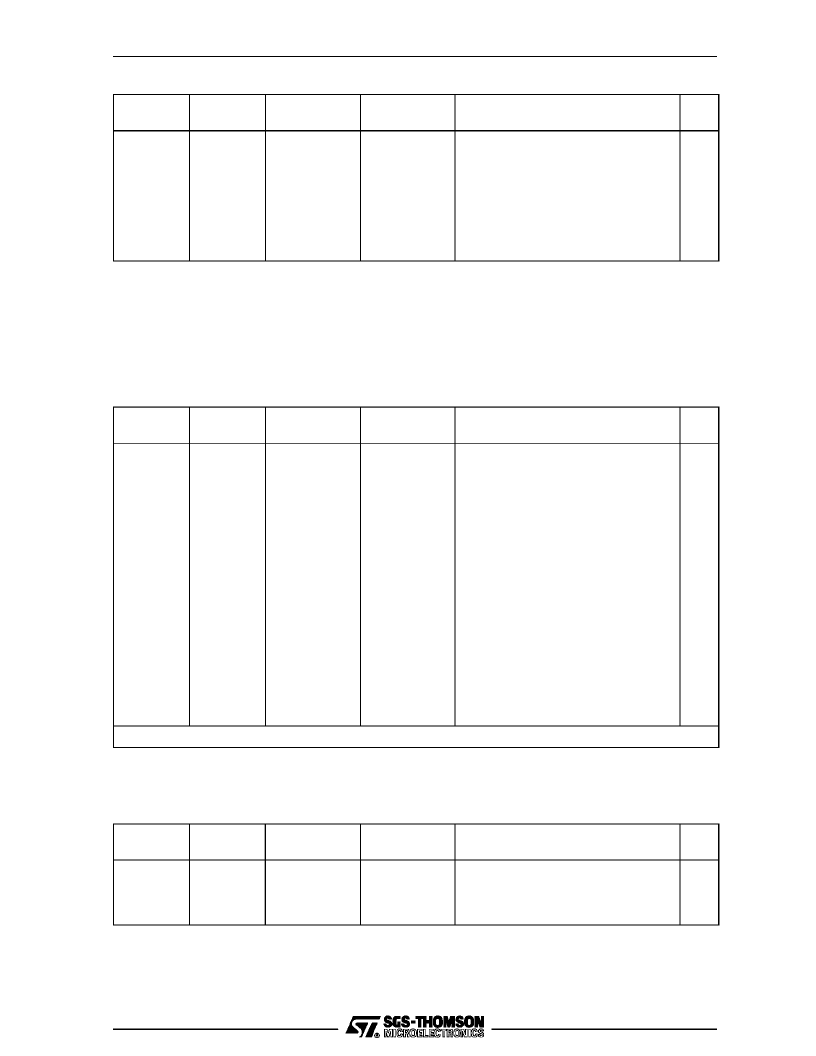

11 Transputer instruction set summary

/ 74

71

Operation

Code

74

75

Memory

Code

27F4

27F5

Mnemonic

Processor

Cycles

35

11

Name

DEF

crcword

crcbyte

calculate crc on word

calculate crc on byte

76

77

78

27F6

27F7

27F8

bitcnt

bitrevword

bitrevnbits

b

+2

36

n

+4

count bits set in word

reverse bits in word

reverse bottom n bits in word

Table 11.22

CRC and bit operation codes

11.8

Floating point instructions

11.9

Floating point instructions for IMS T805 only

Operation

Code

8E

8A

86

82

9F

A0

AA

A6

AC

A8

88

84

9E

Memory

Code

28FE

28FA

28F6

28F2

29FF

2AF0

2AFA

2AF6

2AFC

2AF8

28F8

28F4

29FE

Mnemonic

Processor

Cycles

2

3

4

6

2

2

8/11

9/12

13/20

21/30

2

3

4

Name

DEF

fpldnlsn

fpldnldb

fpldnlsni

fpldnldbi

fpldzerosn

fpldzerodb

fpldnladdsn

fpldnladddb

fpldnlmulsn

fpldnlmuldb

fpstnlsn

fpstnldb

fpstnli32

fp load non-local single

fp load non-local double

fp load non-local indexed single

fp load non-local indexed double

load zero single

load zero double

fp load non local & add single

fp load non local & add double

fp load non local & multiply single

fp load non local & multiply double

fp store non-local single

fp store non-local double

store non-local int32

F

F

F

F

Processor cycles are shown as

Typical/Maximum

cycles.

Table 11.23

Floating point load/store operation codes

Operation

Code

AB

A4

A3

Memory

Code

2AFB

2AF4

2AF3

Mnemonic

Processor

Cycles

1

1

1

Name

DEF

fpentry

fprev

fpdup

floating point unit entry

fp reverse

fp duplicate

Table 11.24

Floating point general operation codes

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| IMST425-G25S | 32-Bit Microprocessor |

| IMST425G30S | Peripheral IC |

| IMST425J17S | Peripheral IC |

| IMST425-J17S | 32-Bit Microprocessor |

| IMST425J20S | Peripheral IC |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| IMST425-G25S | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:32-Bit Microprocessor |

| IMST425G30S | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Peripheral IC |

| IMST425J17S | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Peripheral IC |

| IMST425-J17S | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:32-Bit Microprocessor |

| IMST425J20S | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Peripheral IC |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。