- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄360859 > IMST425J17S Peripheral IC PDF資料下載

參數(shù)資料

| 型號: | IMST425J17S |

| 英文描述: | Peripheral IC |

| 中文描述: | 外圍芯片 |

| 文件頁數(shù): | 24/74頁 |

| 文件大小: | 563K |

| 代理商: | IMST425J17S |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁當前第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁

IMS T400

/ 74

24

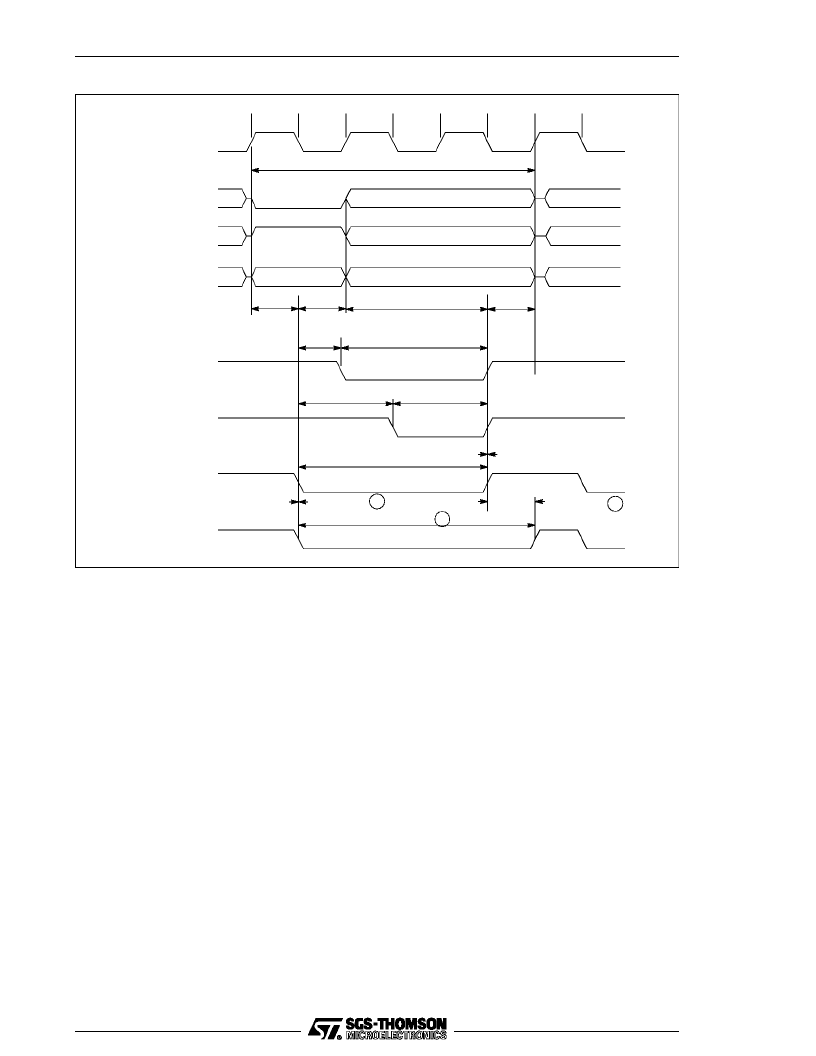

ProcClockOut

MemnotWrD0

MemnotRfD1

MemAD2–31

notMemWrB0–3

(Early write)

notMemS0

(CE)

notMemS1

(ALE)

T1

T2

T3

Tmx

T5

T6

T1

Tstate

TaVS0LTS0LaX

TWrHDX

TdVWrH

Data

Address

TS0LWrL

TWrLWrH

TS0HWrH

TS0LS0H

TS0LS1L

TS0LS1H

TS0HS1H

T4

Data

Data

notMemWrB0–3

(Late write)

TS0LWrL

TWrLWrH

9

5

1

Figure 5.8

IMS T400 external write cycle

5.4

Wait

Taking

MemWait

high with the timing shown (figure 5.9) will extend the duration of

T4

.

MemWait

is

sampled close to the falling edge of

ProcClockOut

during a

T3

or

T4

period, prior to, but not at the end

of

T4

. By convention,

notMemS4

is used to synchronize wait state insertion. If this or another strobe is

used, its delay should be such as to take the strobe low an even number of periods

Tm

after the start of

T1

, to coincide with a rising edge of

ProcClockOut

.

MemWait

may be kepthigh indefinitely, although ifdynamic memory refresh is used itshould notbe kept

high longenough to interfere with refresh timing.

MemWait

operates normallyduring all cycles,including

refresh and configuration cycles. It does not affect internal memory access in any way.

If thestartof

T5

wouldcoincidewitha fallingedgeof

ProcClockOut

an extrawait period

Tm

(

EW

)isgener-

atedbytheEMItoforcecoincidencewitharisingedge.Risingedgecoincidenceisonlyforcedifwaitstates

are added, otherwise coincidence with a falling edge is permitted.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| IMST425-J17S | 32-Bit Microprocessor |

| IMST425J20S | Peripheral IC |

| IMST425-J20S | 32-Bit Microprocessor |

| IMST425-J25S | 32-Bit Microprocessor |

| IMST425-X25S | 32-Bit Microprocessor |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| IMST425-J17S | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:32-Bit Microprocessor |

| IMST425J20S | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Peripheral IC |

| IMST425-J20S | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:32-Bit Microprocessor |

| IMST425-J25S | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:32-Bit Microprocessor |

| IMST425-X25S | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:32-Bit Microprocessor |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。