- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄378626 > IN74AC109 (INTEGRAL JOINT STOCK COMPANY) Dual J-K Flip-Flop with Set and Reset High-Speed Silicon-Gate CMOS PDF資料下載

參數(shù)資料

| 型號(hào): | IN74AC109 |

| 廠(chǎng)商: | INTEGRAL JOINT STOCK COMPANY |

| 英文描述: | Dual J-K Flip-Flop with Set and Reset High-Speed Silicon-Gate CMOS |

| 中文描述: | 雙JK觸發(fā)器的設(shè)置和復(fù)位高速硅柵CMOS |

| 文件頁(yè)數(shù): | 4/5頁(yè) |

| 文件大?。?/td> | 170K |

| 代理商: | IN74AC109 |

IN74AC109

120

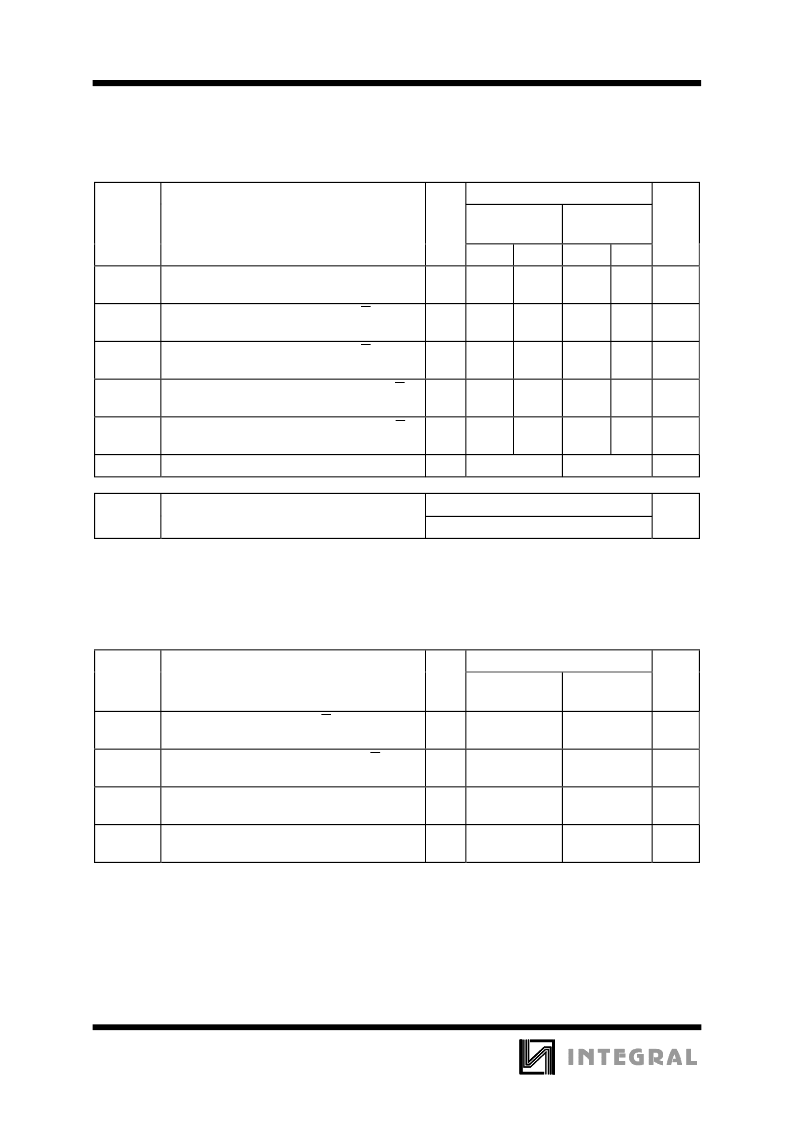

AC ELECTRICAL CHARACTERISTICS

(C

L

=50pF,Input t

r

=t

f

=3.0 ns)

V

CC

V

*

Guaranteed Limits

25

°

C

Symbol

Parameter

-40

°

C to

85

°

C

Min

Unit

Min

Max

Max

f

max

Maximum Clock Frequency (Figure 1)

3.3

5.0

125

150

100

125

MHz

t

PLH

Propagation Delay , Clock to Q or Q

(Figure 1)

3.3

5.0

4.0

2.5

13.5

10.0

3.5

2.0

16.0

10.5

ns

t

PHL

Propagation Delay , Clock to Q or Q

(Figure 1)

3.3

5.0

3.0

2.0

14.0

10.0

3.0

1.5

14.5

10.5

ns

t

PLH

Propagation Delay , Set or Reset to Q or Q

(Figure 2)

3.3

5.0

3.0

2.5

12.0

9.0

2.5

2.0

13.0

10.0

ns

t

PHL

Propagation Delay , Set or Reset to Q or Q

(Figure 2)

3.3

5.0

3.0

2.0

12.0

9.5

3.0

2.0

13.5

10.5

ns

C

IN

Maximum Input Capacitance

5.0

4.5

4.5

pF

Typical @25

°

C,V

CC

=5.0 V

35

C

PD

Power Dissipation Capacitance

pF

*

Voltage Range 3.3 V is 3.3 V

±

0.3 V

Voltage Range 5.0 V is 5.0 V

±

0.5 V

TIMING REQUIREMENTS

(C

L

=50pF,Input t

r

=t

f

=3.0 ns)

V

CC

V

*

Guaranteed Limits

25

°

C

Symbol

Parameter

-40

°

C to

85

°

C

7.5

5.0

Unit

t

su

Minimum Setup Time, J or K to Clock (Figure

3)

3.3

5.0

6.5

4.5

ns

t

h

Minimum Hold Time, Clock to J or K (Figure

3)

3.3

5.0

0

0.5

0

0.5

ns

t

w

Minimum Pulse Width, Set, Reset, Clock

(Figures 1,2)

3.3

5.0

4.0

3.5

4.5

3.5

ns

t

rec

Minimum Recovery Time, Set or Reset to

Clock (Figure 2)

3.3

5.0

0

0

0

0

ns

*

Voltage Range 3.3 V is 3.3 V

±

0.3 V

Voltage Range 5.0 V is 5.0 V

±

0.5 V

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| IN74AC109D | Dual J-K Flip-Flop with Set and Reset High-Speed Silicon-Gate CMOS |

| IN74AC109N | 30-AWG WHITE 50 FT ROLL |

| IN74AC125 | Quad 3-State Noninverting Buffers High-Speed Silicon-Gate CMOS |

| IN74AC132 | Quad 2-Input NAND Gate with Schmitt-Trigger Inputs High-Performance Silicon-Gate CMOS |

| IN74AC132D | Quad 2-Input NAND Gate with Schmitt-Trigger Inputs High-Performance Silicon-Gate CMOS |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| IN74AC109D | 制造商:INTEGRAL 制造商全稱(chēng):INTEGRAL 功能描述:Dual J-K Flip-Flop with Set and Reset High-Speed Silicon-Gate CMOS |

| IN74AC109N | 制造商:INTEGRAL 制造商全稱(chēng):INTEGRAL 功能描述:Dual J-K Flip-Flop with Set and Reset High-Speed Silicon-Gate CMOS |

| IN74AC112 | 制造商:IKSEMICON 制造商全稱(chēng):IK Semicon Co., Ltd 功能描述:Dual J-K Flip-Flop with Set and Reset High-Speed Silicon-Gate CMOS |

| IN74AC112D | 制造商:INTEGRAL 制造商全稱(chēng):INTEGRAL 功能描述:Dual J-K Flip-Flop with Set and Reset High-Speed Silicon-Gate CMOS |

| IN74AC112N | 制造商:IKSEMICON 制造商全稱(chēng):IK Semicon Co., Ltd 功能描述:Dual J-K Flip-Flop with Set and Reset High-Speed Silicon-Gate CMOS |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。