- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄360867 > INTEL387DX Intel387 DX - MATH COPROCESSOR PDF資料下載

參數(shù)資料

| 型號: | INTEL387DX |

| 英文描述: | Intel387 DX - MATH COPROCESSOR |

| 中文描述: | Intel387霉素-數(shù)學(xué)協(xié)處理器 |

| 文件頁數(shù): | 21/41頁 |

| 文件大小: | 435K |

| 代理商: | INTEL387DX |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁當(dāng)前第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁

Intel387

TM

DX MATH COPROCESSOR

3.1.4 SYSTEM RESET (RESETIN)

A LOW to HIGH transition on this pin causes the

MCP to terminate its present activity and to enter a

dormant state. RESETIN must remain HIGH for at

least 40 NUMCLK2 periods. The HIGH to LOW tran-

sitions of RESETIN must be synchronous with

CPUCLK2, so that the phase of the internal clock of

the bus control logic (which is the CPUCLK2 divided

by 2) is the same as the phase of the internal clock

of the Intel386 DX CPU. After RESETIN goes LOW,

at least 50 NUMCLK2 periods must pass before the

first MCP instruction is written into the Intel387 DX

MCP. This pin should be connected to the Intel386

DX CPU RESET pin. Table 3.3 shows the status of

other pins after a reset.

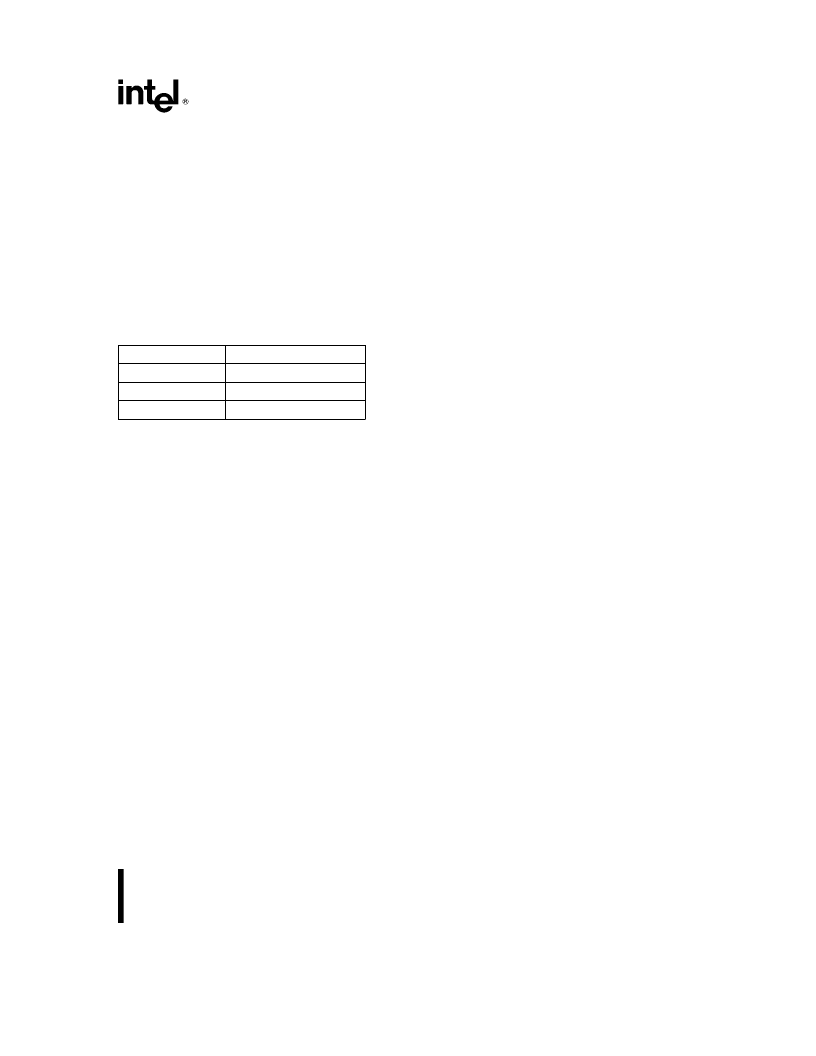

Table 3.3. Output Pin Status During Reset

Pin Value

Pin Name

HIGH

READYO

Y

, BUSY

Y

LOW

PEREQ, ERROR

Y

Tri-State OFF

D31–D0

3.1.5 PROCESSOR EXTENSION REQUEST

(PEREQ)

When active, this pin signals to the Intel386 DX CPU

that the MCP is ready for data transfer to/from its

data FIFO. When all data is written to or read from

the data FIFO, PEREQ is deactivated. This signal

always goes inactive before BUSY

Y

goes inactive.

This signal is referenced to CPUCLK2. It should be

connected to the Intel386 DX CPU PEREQ input.

3.1.6 BUSY STATUS (BUSY

Y

)

When active, this pin signals to the Intel386 DX CPU

that the MCP is currently executing an instruction.

This signal is referenced to CPUCLK2. It should be

connected to the Intel386 DX CPU BUSY

Y

pin.

3.1.7 ERROR STATUS (ERROR

Y

)

This pin reflects the ES bits of the status register.

When active, it indicates that an unmasked excep-

tion has occurred (except that, immediately after a

reset, it indicates to the Intel386 DX Microprocessor

that a Intel387 DX MCP is present in the system).

This signal can be changed to inactive state only by

the following instructions (without a preceding

WAIT): FNINIT, FNCLEX, FNSTENV, and FNSAVE.

This signal is referenced to NUMCLK2. It should be

connected to the Intel386 DX CPU ERROR

Y

pin.

3.1.8 DATA PINS (D31–D0)

These bidirectional pins are used to transfer data

and opcodes between the Intel386 DX CPU and In-

tel387 DX MCP. They are normally connected direct-

ly to the corresponding Intel386 DX CPU data pins.

HIGH state indicates a value of one. D0 is the least

significant data bit. Timings are referenced to

CPUCLK2.

3.1.9 WRITE/READ BUS CYCLE (W/R

Y

)

This signal indicates to the MCP whether the In-

tel386 DX CPU bus cycle in progress is a read or a

write cycle. This pin should be connected directly to

the Intel386 DX CPU W/R

Y

pin. HIGH indicates a

write cycle; LOW, a read cycle. This input is ignored

if any of the signals STEN, NPS1

Y

, or NPS2 is inac-

tive. Setup and hold times are referenced to

CPUCLK2.

3.1.10 ADDRESS STROBE (ADS

Y

)

This input, in conjunction with the READY

Y

input

indicates when the MCP bus-control logic may sam-

ple W/R

Y

and the chip-select signals. Setup and

hold times are referenced to CPUCLK2. This pin

should be connected to the Intel386 DX CPU ADS

Y

pin.

21

21

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| INTEL740 | 64-Bit Graphics (GUI) Accelerator |

| INTRO_TO_TRANSISTOR | |

| INTRUMENT | For EM60000 series |

| IO100VXI | |

| IO110VXI | |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| INTEL387SX | 制造商:INTEL 制造商全稱:Intel Corporation 功能描述:Intel387 SX - MATH COPROCESSOR |

| INTEL387TMDX | 制造商:INTEL 制造商全稱:Intel Corporation 功能描述:Intel387TM DX MATH COPROCESSOR |

| INTEL740 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:64-Bit Graphics (GUI) Accelerator |

| INTEL82801 | 制造商:INTEL 制造商全稱:Intel Corporation 功能描述:82801AB (ICH0) I/O Controller Hub |

| INTEL82802AB | 制造商:INTEL 制造商全稱:Intel Corporation 功能描述:Firmware Hub (FWH) |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。