- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄377551 > IS42S32200B-7T (INTEGRATED SILICON SOLUTION INC) 512K Bits x 32 Bits x 4 Banks (64-MBIT) SYNCHRONOUS DYNAMIC RAM PDF資料下載

參數(shù)資料

| 型號(hào): | IS42S32200B-7T |

| 廠商: | INTEGRATED SILICON SOLUTION INC |

| 元件分類: | DRAM |

| 英文描述: | 512K Bits x 32 Bits x 4 Banks (64-MBIT) SYNCHRONOUS DYNAMIC RAM |

| 中文描述: | 2M X 32 SYNCHRONOUS DRAM, 6.5 ns, PDSO86 |

| 封裝: | 0.400 INCH, PLASTIC, TSOP2-86 |

| 文件頁(yè)數(shù): | 13/56頁(yè) |

| 文件大小: | 537K |

| 代理商: | IS42S32200B-7T |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)當(dāng)前第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)

IS42S32200B

ISSI

Integrated Silicon Solution, Inc. — www.issi.com —

1-800-379-4774

Rev. 00C

09/29/03

13

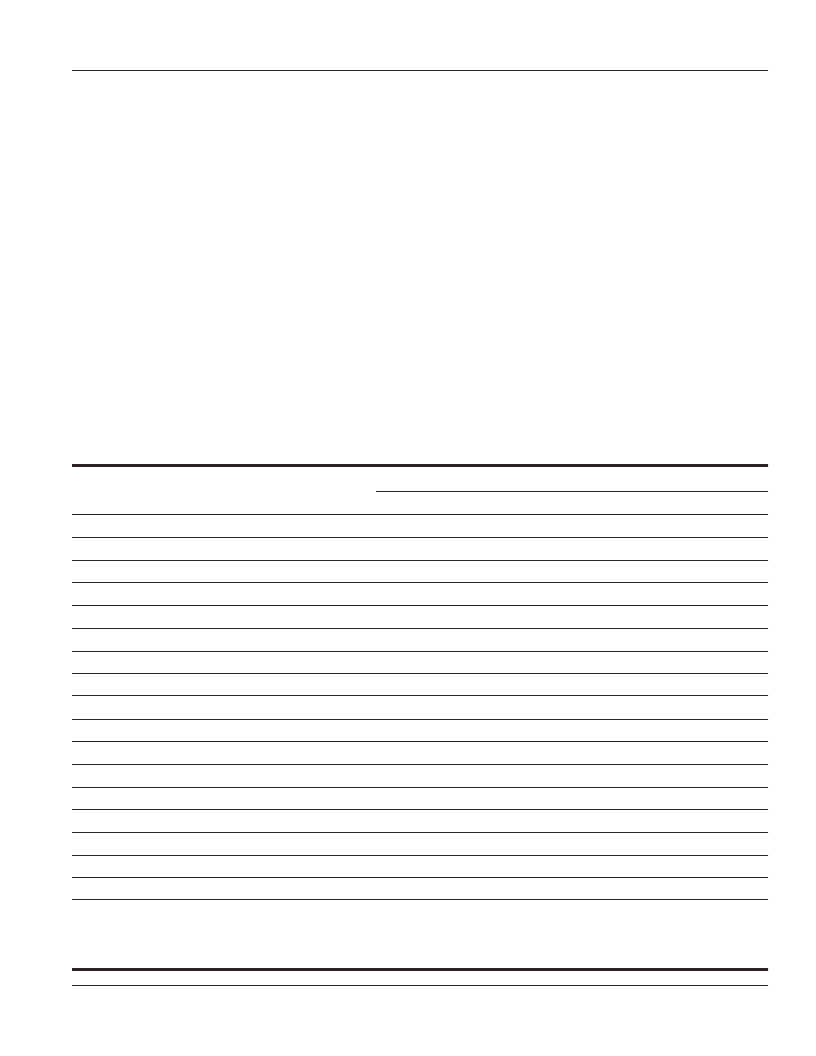

BURST DEFINITION

Burst

Starting Column

Order of Accesses Within a Burst

Length

Address

Type = Sequential

Type = Interleaved

A0

2

0

0-1

0-1

1

1-0

1-0

A1

A0

0

0

0-1-2-3

0-1-2-3

4

0

1

1-2-3-0

1-0-3-2

1

0

2-3-0-1

2-3-0-1

1

1

3-0-1-2

3-2-1-0

A2

A1

A0

0

0

0

0-1-2-3-4-5-6-7

0-1-2-3-4-5-6-7

0

0

1

1-2-3-4-5-6-7-0

1-0-3-2-5-4-7-6

0

1

0

2-3-4-5-6-7-0-1

2-3-0-1-6-7-4-5

8

0

1

1

3-4-5-6-7-0-1-2

3-2-1-0-7-6-5-4

1

0

0

4-5-6-7-0-1-2-3

4-5-6-7-0-1-2-3

1

0

1

5-6-7-0-1-2-3-4

5-4-7-6-1-0-3-2

1

1

0

6-7-0-1-2-3-4-5

6-7-4-5-2-3-0-1

1

1

1

7-0-1-2-3-4-5-6

7-6-5-4-3-2-1-0

Full

Page

(y)

n = A0-A7

Cn, Cn + 1, Cn + 2

Cn + 3, Cn + 4...

…Cn - 1,

Cn…

Not Supported

(location 0-y)

Burst Length

Read and write accesses to the SDRAM are burst ori-

ented, with the burst length being programmable, as

shown in MODE REGISTER DEFINITION. The burst

length determines the maximum number of column loca-

tions that can be accessed for a given READ or WRITE

command. Burst lengths of 1, 2, 4 or 8 locations are

available for both the sequential and the interleaved burst

types, and a full-page burst is available for the sequential

type. The full-page burst is used in conjunction with the

BURST TERMINATE command to generate arbitrary

burst lengths.

Reserved states should not be used, as unknown opera-

tion or incompatibility with future versions may result.

When a READ or WRITE command is issued, a block of

columns equal to the burst length is effectively selected.

All accesses for that burst take place within this block,

meaning that the burst will wrap within the block if a

boundary is reached. The block is uniquely selected by

A1-A7 (x32) when the burst length is set to two; by A2-A7

(x32) when the burst length is set to four; and by A3-A7

(x32) when the burst length is set to eight. The remaining

(least significant) address bit(s) is (are) used to select the

starting location within the block. Full-page bursts wrap

within the page if the boundary is reached.

Burst Type

Accesses within a given burst may be programmed to be

either sequential or interleaved; this is referred to as the

burst type and is selected via bit M3.

The ordering of accesses within a burst is determined by

the burst length, the burst type and the starting column

address, as shown in BURST DEFINITION table.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| IS42S32200B-7TI | 512K Bits x 32 Bits x 4 Banks (64-MBIT) SYNCHRONOUS DYNAMIC RAM |

| IS42S32200B-7TL | 512K Bits x 32 Bits x 4 Banks (64-MBIT) SYNCHRONOUS DYNAMIC RAM |

| IS42S32200B-7TLI | 512K Bits x 32 Bits x 4 Banks (64-MBIT) SYNCHRONOUS DYNAMIC RAM |

| IS42S32200C1 | 512K Bits x 32 Bits x 4 Banks (64-MBIT) SYNCHRONOUS DYNAMIC RAM |

| IS42S32200C1-55T | 512K Bits x 32 Bits x 4 Banks (64-MBIT) SYNCHRONOUS DYNAMIC RAM |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| IS42S32200B-7TI | 制造商:Integrated Silicon Solution Inc 功能描述:DRAM Chip SDRAM 64M-Bit 2Mx32 3.3V 86-Pin TSOP-II |

| IS42S32200B-7TI-TR | 制造商:Integrated Silicon Solution Inc 功能描述:DRAM Chip SDRAM 64M-Bit 2Mx32 3.3V 86-Pin TSOP-II T/R |

| IS42S32200B-7TL | 制造商:ISSI 制造商全稱:Integrated Silicon Solution, Inc 功能描述:512K Bits x 32 Bits x 4 Banks (64-MBIT) SYNCHRONOUS DYNAMIC RAM |

| IS42S32200B-7TLI | 制造商:ISSI 制造商全稱:Integrated Silicon Solution, Inc 功能描述:512K Bits x 32 Bits x 4 Banks (64-MBIT) SYNCHRONOUS DYNAMIC RAM |

| IS42S32200B-7T-TR | 制造商:Integrated Silicon Solution Inc 功能描述:DRAM Chip SDRAM 64M-Bit 2Mx32 3.3V 86-Pin TSOP-II T/R |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。