- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄377554 > IS61C1024 (Integrated Silicon Solution, Inc.) 128K x 8 HIGH-SPEED CMOS STATIC RAM PDF資料下載

參數(shù)資料

| 型號: | IS61C1024 |

| 廠商: | Integrated Silicon Solution, Inc. |

| 英文描述: | 128K x 8 HIGH-SPEED CMOS STATIC RAM |

| 中文描述: | 128K的× 8高速CMOS靜態(tài)RAM |

| 文件頁數(shù): | 1/11頁 |

| 文件大小: | 80K |

| 代理商: | IS61C1024 |

IS61C1024

IS61C1024L

128K x 8 HIGH-SPEED

CMOS STATIC RAM

ISSI reserves the right to make changes to its products at any time without notice in order to improve design and supply the best possible product. We assume no responsibility for any errors which

may appear in this publication. Copyright 1999, Integrated Silicon Solution, Inc.

DESCRIPTION

The

ISSI

IS61C1024 and IS61C1024L are very high-speed,

low power, 131,072-word by 8-bit CMOS static RAMs. They

are fabricated using ISSIs high-performance CMOS

technology. This highly reliable process coupled with innovative

circuit design techniques, yields higher performance and low

power consumption devices.

When

CE1

is HIGH or CE2 is LOW (deselected), the device

assumes a standby mode at which the power dissipation can

be reduced by using CMOS input levels.

Easy memory expansion is provided by using two Chip Enable

inputs,

CE1

and CE2. The active LOW Write Enable (

WE

)

controls both writing and reading of the memory.

The IS61C1024 and IS61C1024L are available in 32-pin

300-mil SOJ, and TSOP (Type I, 8x20), and sTSOP (Type I,

8 x 13.4) packages.

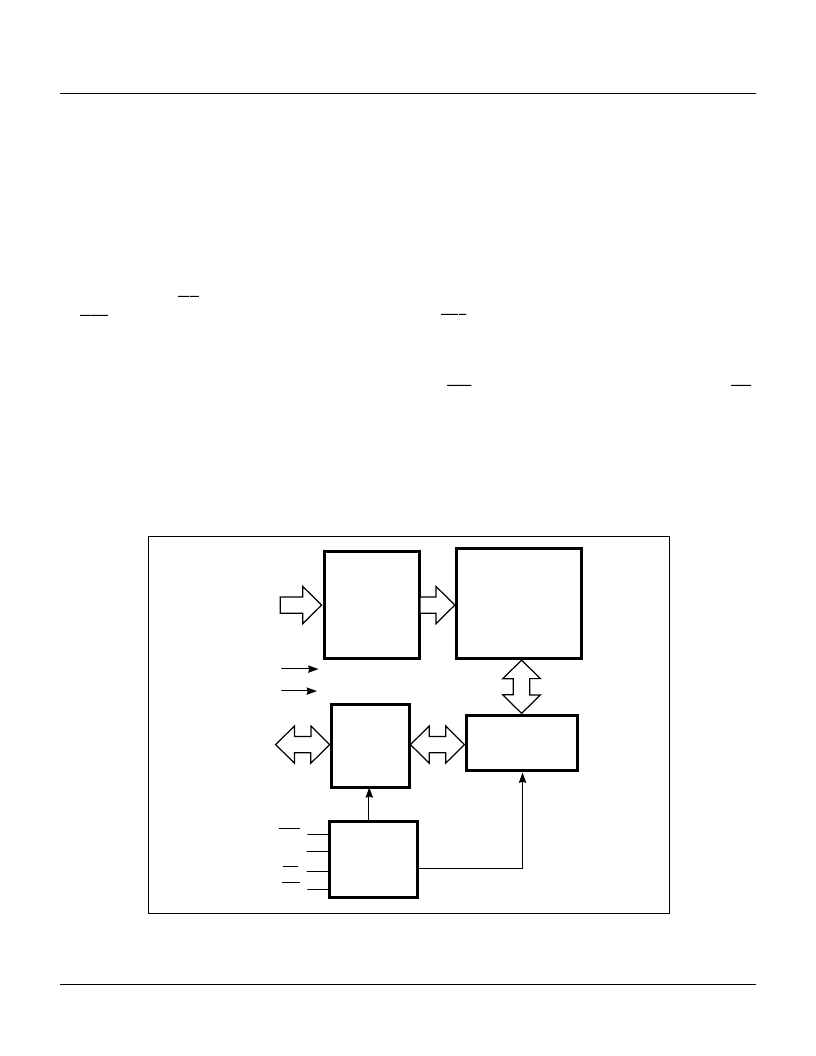

FUNCTIONAL BLOCK DIAGRAM

A0-A16

CE1

CE2

OE

WE

512 x 2048

MEMORY ARRAY

DECODER

COLUMN I/O

CONTROL

CIRCUIT

GND

VCC

I/O

DATA

CIRCUIT

I/O0-I/O7

FEATURES

High-speed access time: 12, 15, 20, 25 ns

Low active power: 600 mW (typical)

Low standby power: 500

μ

W (typical) CMOS

standby

Output Enable (

OE

) and two Chip Enable

(

CE1

and CE2) inputs for ease in applications

Fully static operation: no clock or refresh

required

TTL compatible inputs and outputs

Single 5V (

±

10%) power supply

Low power version available: IS61C1024L

Commercial and industrial temperature ranges

available

MAY 1999

ISSI

Integrated Silicon Solution, Inc. — 1-800-379-4774

SR028-1K

05/12/99

1

相關PDF資料 |

PDF描述 |

|---|---|

| IS61C1024-12H | 128K x 8 HIGH-SPEED CMOS STATIC RAM |

| IS61C1024-12HI | RES POWER .020 OHM 2W 5% SMT |

| IS61C1024-12J | 128K x 8 HIGH-SPEED CMOS STATIC RAM |

| IS61C1024-12JI | 128K x 8 HIGH-SPEED CMOS STATIC RAM |

| IS61C1024-12K | 128K x 8 HIGH-SPEED CMOS STATIC RAM |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| IS61C1024_99 | 制造商:ISSI 制造商全稱:Integrated Silicon Solution, Inc 功能描述:128K x 8 HIGH-SPEED CMOS STATIC RAM |

| IS61C10240L-15H | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:x8 SRAM |

| IS61C10240L-15HI | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:x8 SRAM |

| IS61C10240L-20H | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:x8 SRAM |

| IS61C10240L-20HI | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:x8 SRAM |

發(fā)布緊急采購,3分鐘左右您將得到回復。