- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄383143 > ISL6225CA-T (INTERSIL CORP) Dual Mobile-Friendly PWM Controller with DDR Memory Option PDF資料下載

參數(shù)資料

| 型號: | ISL6225CA-T |

| 廠商: | INTERSIL CORP |

| 元件分類: | 穩(wěn)壓器 |

| 英文描述: | Dual Mobile-Friendly PWM Controller with DDR Memory Option |

| 中文描述: | DUAL SWITCHING CONTROLLER, 345 kHz SWITCHING FREQ-MAX, PDSO28 |

| 封裝: | PLASTIC, SSOP-28 |

| 文件頁數(shù): | 8/19頁 |

| 文件大?。?/td> | 522K |

| 代理商: | ISL6225CA-T |

8

FN9049.7

December 28, 2004

Description

Operation

The ISL6225 is a dual channel PWM controller intended for

use in power supplies for graphic chipset, SDRAM, DDR

DRAM or other low voltage power applications in modern

notebook and sub-notebook PCs. The IC integrates two

control circuits for two synchronous buck converters. The

output voltage of each controller can be set in the range of

0.9V to 5.5V by an external resistive divider. Out-of-phase

operation with 180 degree phase shift reduces input current

ripple.

The synchronous buck converters can operate from either

an unregulated DC source such as a notebook battery with a

voltage ranging from 5.0V to 24V, or from a regulated system

rail of 3.3V or 5V. In either mode of operation the controller is

biased from the +5V source.

The controllers operate in the current mode with input

voltage feed-forward for simplified feedback loop

compensation and reduced effect of the input voltage

variation. An integrated feedback loop compensation

dramatically reduces the number of external components.

Depending on the load level, converters can operate either

in a fixed-frequency mode or in a hysteretic mode. Switch-

over to the hysteretic mode operation at light loads improves

the converters' efficiency and prolongs battery run time. The

hysteretic mode of operation can be inhibited independently

for each channel if a variable frequency operation is not

desired.

The ISL6225 has a special means to rearrange its internal

architecture into a complete DDR solution. When DDR input

is set high, the second channel can provide the capability to

track the output voltage of the first channel. The buffered

reference voltage required by DDR memory chips is also

provided.

Initialization

The Power-On Reset (POR) function continually monitors

the bias supply voltage on the V

CC

pin and initiates soft-start

operation after the input supply voltage exceeds 4.5V.

Should this voltage drop lower than 4.0V, the POR disables

the chip.

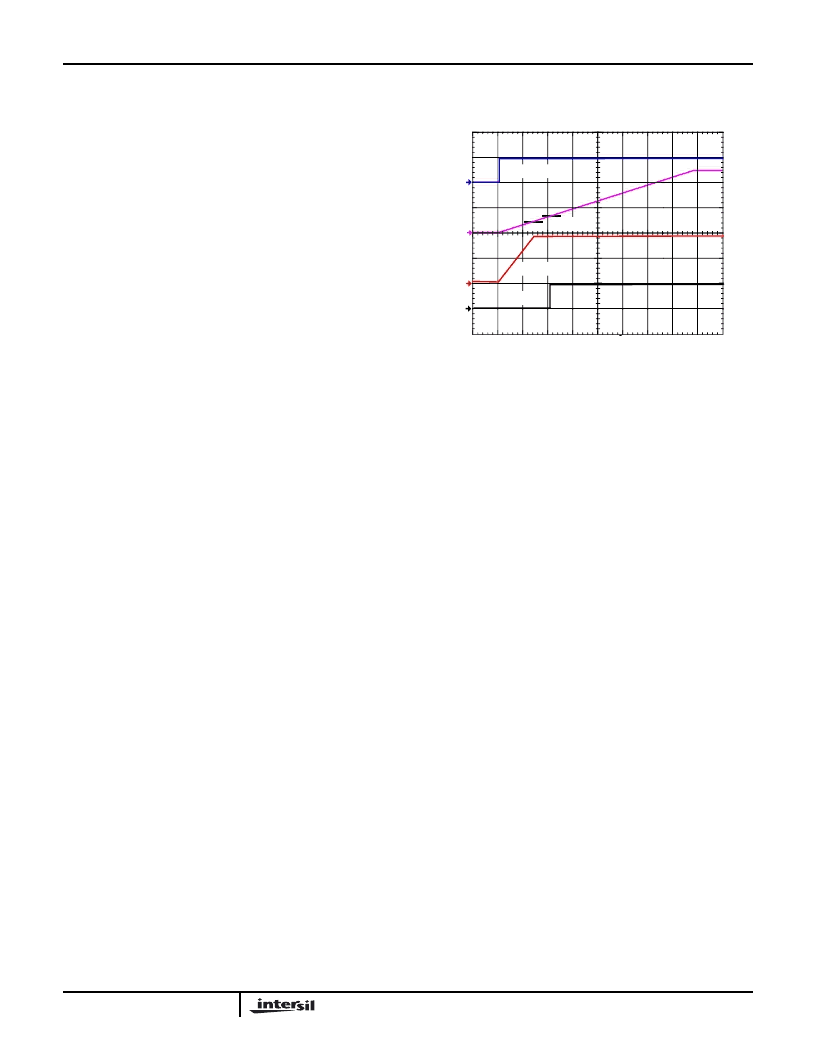

Soft-Start

When soft-start is initiated, the voltage on the SOFT pin

starts to ramp gradually due to the 5

μ

A current sourced into

the external soft-start capacitor. The output voltage starts to

follow the soft-start voltage.

When the SOFT pin voltage reaches a level of 0.9V, the

output voltage comes into regulation while the soft-start pin

voltage continues to rise. When the SOFT voltage reaches

1.5V, the power good (PGOOD), the mode control, and the

fault functions are enabled, as depicted in Figure 3.

This completes the soft-start sequence. Further rise of pin

voltage does not affect the output voltage. During the soft-

start, the converter always operates in continuous

conduction mode independently of the load level or FCCM

pin potential.

The soft-start time (the time from the moment when EN

becomes high to the moment when PGOOD is reported) is

determined by the following equation.

The time it takes the output voltage to come into regulation

can be obtained from the following equation.

Having such a spread between the time when the output

voltage reaches the regulation point and the moment when

PGOOD is reported allows for a fault-safe test mode by

means of an external circuit that clamps the SOFT pin

voltage on the level 0.9V < V

SOFT

< 1.5V.

Output Voltage Program

The output voltage of either channel is set by a resistive divider

from the output to ground. The center point of the divider is

connected to VSEN pin as shown in Figure 4. The output

voltage value is determined by the following equation.

Where 0.9V is the value of the internal reference. The VSEN

pin voltage is also used by the controller for the power good

function and to detect Undervoltage and Overvoltage

conditions.

FIGURE 3. START UP

Ch3 1.0V

Ch2 2.0V

Ch4 5.0V

M1.00ms

Ch1 5.0V

3

2

4

1

EN

0.9V1.5V

SOFT

VOUT

PGOOD

TSOFT

----------------------------------

=

TRISE

0.6

TSOFT

×

=

VO

-----------------------------+

)

=

相關PDF資料 |

PDF描述 |

|---|---|

| ISL6225CAZA | Dual Mobile-Friendly PWM Controller with DDR Memory Option |

| ISL6226 | Advanced PWM and Linear Power Controller for Portable Applications |

| ISL6226EVAL1 | Advanced PWM and Linear Power Controller for Portable Applications |

| ISL6226CA | Octal D-Type Transparent Latches With 3-State Outputs 20-SOIC -40 to 85 |

| ISL6232 | Octal D-Type Transparent Latches With 3-State Outputs 20-SOIC -40 to 85 |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| ISL6225CAZ | 功能描述:電流型 PWM 控制器 DL SWITCHER W/DRR OPTION 30V CS80 FSC RoHS:否 制造商:Texas Instruments 開關頻率:27 KHz 上升時間: 下降時間: 工作電源電壓:6 V to 15 V 工作電源電流:1.5 mA 輸出端數(shù)量:1 最大工作溫度:+ 105 C 安裝風格:SMD/SMT 封裝 / 箱體:TSSOP-14 |

| ISL6225CAZA | 功能描述:電流型 PWM 控制器 W/ANNEAL DL SWITCHER W/DRR OPTION 30V RoHS:否 制造商:Texas Instruments 開關頻率:27 KHz 上升時間: 下降時間: 工作電源電壓:6 V to 15 V 工作電源電流:1.5 mA 輸出端數(shù)量:1 最大工作溫度:+ 105 C 安裝風格:SMD/SMT 封裝 / 箱體:TSSOP-14 |

| ISL6225CAZA-T | 功能描述:電流型 PWM 控制器 W/ANNEAL DL SWITCHER W/DRR OPTION 30V RoHS:否 制造商:Texas Instruments 開關頻率:27 KHz 上升時間: 下降時間: 工作電源電壓:6 V to 15 V 工作電源電流:1.5 mA 輸出端數(shù)量:1 最大工作溫度:+ 105 C 安裝風格:SMD/SMT 封裝 / 箱體:TSSOP-14 |

| ISL6225CAZ-T | 功能描述:IC CTRLR DDR DRAM, SDRAM 28QSOP RoHS:是 類別:集成電路 (IC) >> PMIC - 穩(wěn)壓器 - 專用型 系列:- 標準包裝:43 系列:- 應用:控制器,Intel VR11 輸入電壓:5 V ~ 12 V 輸出數(shù):1 輸出電壓:0.5 V ~ 1.6 V 工作溫度:-40°C ~ 85°C 安裝類型:表面貼裝 封裝/外殼:48-VFQFN 裸露焊盤 供應商設備封裝:48-QFN(7x7) 包裝:管件 |

| ISL6226 | 制造商:INTERSIL 制造商全稱:Intersil Corporation 功能描述:Advanced PWM and Linear Power Controller for Portable Applications |

發(fā)布緊急采購,3分鐘左右您將得到回復。