- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄360999 > ISP1761ET (NXP SEMICONDUCTORS) Hi-Speed Universal Serial Bus On-The-Go controller PDF資料下載

參數(shù)資料

| 型號: | ISP1761ET |

| 廠商: | NXP SEMICONDUCTORS |

| 元件分類: | 總線控制器 |

| 英文描述: | Hi-Speed Universal Serial Bus On-The-Go controller |

| 中文描述: | UNIVERSAL SERIAL BUS CONTROLLER, PBGA128 |

| 封裝: | 9 X 9 MM, 0.80 MM HEIGHT, PLASTIC, MO-195, SOT857-1, TFBGA-128 |

| 文件頁數(shù): | 36/158頁 |

| 文件大?。?/td> | 724K |

| 代理商: | ISP1761ET |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁當(dāng)前第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁第122頁第123頁第124頁第125頁第126頁第127頁第128頁第129頁第130頁第131頁第132頁第133頁第134頁第135頁第136頁第137頁第138頁第139頁第140頁第141頁第142頁第143頁第144頁第145頁第146頁第147頁第148頁第149頁第150頁第151頁第152頁第153頁第154頁第155頁第156頁第157頁第158頁

9397 750 13258

Koninklijke Philips Electronics N.V. 2005. All rights reserved.

Product data sheet

Rev. 01 — 12 January 2005

36 of 158

Philips Semiconductors

ISP1761

Hi-Speed USB OTG controller

[1]

The reserved bits should always be written with the reset value.

[1]

For details on register bit description, refer to Enhanced Host Controller Interface Specification for Universal

Serial Bus Rev. 1.0

8.2.3

USBINTR register (R/W: 0028h)

All the bits in this register are reserved.

8.2.4

FRINDEX register (R/W: 002Ch)

The Frame Index (FRINDEX) register is used by the Host Controller to index into the

periodic frame list. The register updates every 125

μ

s (once each microframe). Bits n to 3

are used to select a particular entry in the Periodic Frame List during periodic schedule

execution. The number of bits used for the index depends on the size of the frame list as

set by the system software in the FLS (Frame List Size) field of the USBCMD register.

This register must be written as a Double Word. A Word-only write (16-bit mode) produces

undefined results. This register cannot be written unless the Host Controller is in the

halted state as indicated by the HCH (HCHalted) bit. A write to this register while the RS

(Run/Stop) bit is set produces undefined results. Writes to this register also affect the SOF

value. The bit allocation is given in

Table 19

.

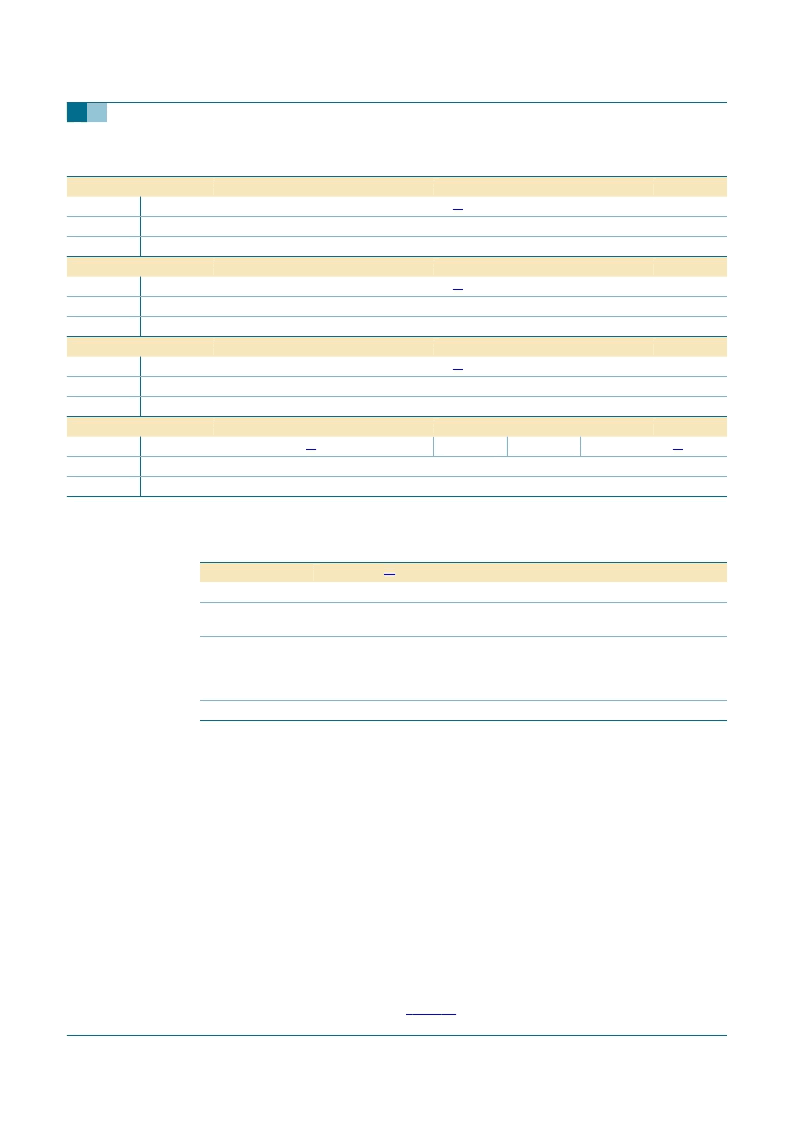

Table 17:

Bit

Symbol

Reset

Access

Bit

Symbol

Reset

Access

Bit

Symbol

Reset

Access

Bit

Symbol

Reset

Access

USBSTS register: bit allocation

31

30

29

28

27

26

25

24

reserved

[1]

0

0

0

0

0

0

0

0

R/W

23

R/W

22

R/W

21

R/W

20

R/W

19

R/W

18

R/W

17

R/W

16

reserved

[1]

0

0

0

0

0

0

0

0

R/W

15

R/W

14

R/W

13

R/W

12

R/W

11

R/W

10

R/W

9

R/W

8

reserved

[1]

0

0

0

1

0

0

0

0

R/W

7

R/W

6

R/W

5

R/W

4

R/W

3

FLR

0

R/W

R/W

2

PCD

0

R/W

R/W

1

R/W

0

reserved

[1]

reserved

[1]

0

0

0

0

0

0

R/W

R/W

R/W

R/W

R/W

R/W

Table 18:

Bit

31 to 4

3

USBSTS register: bit description

Symbol Description

[1]

-

reserved; write logic 0

FLR

Frame List Rollover

: The Host Controller sets this bit to logic 1 when the

Frame List Index rolls over from its maximum value to zero.

PCD

Port Change Detect

: The Host Controller sets this bit to logic 1 when any

port, where the PO bit is cleared, has a change to a one or a FPR bit

changes to a one as a result of a J-K transition detected on a suspended

port.

-

reserved

2

1 to 0

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| ISP2100A | Telecommunication IC |

| ISP2100BN4 | Microprocessor |

| ISP2300 | Controller Miscellaneous - Datasheet Reference |

| ISP2310 | Controller Miscellaneous - Datasheet Reference |

| ISP2312 | Controller Miscellaneous - Datasheet Reference |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| ISP1761ET,518 | 功能描述:USB 接口集成電路 USB 2.0 HS OTG HOST RoHS:否 制造商:Cypress Semiconductor 產(chǎn)品:USB 2.0 數(shù)據(jù)速率: 接口類型:SPI 工作電源電壓:3.15 V to 3.45 V 工作電源電流: 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:WLCSP-20 |

| ISP1761ET,551 | 功能描述:USB 接口集成電路 DO NOT USE ORDER -T OR NO "-" RoHS:否 制造商:Cypress Semiconductor 產(chǎn)品:USB 2.0 數(shù)據(jù)速率: 接口類型:SPI 工作電源電壓:3.15 V to 3.45 V 工作電源電流: 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:WLCSP-20 |

| ISP1761ET,557 | 功能描述:USB 接口集成電路 USB 2.0 HS OTG HOST RoHS:否 制造商:Cypress Semiconductor 產(chǎn)品:USB 2.0 數(shù)據(jù)速率: 接口類型:SPI 工作電源電壓:3.15 V to 3.45 V 工作電源電流: 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:WLCSP-20 |

| ISP1761ETGE | 功能描述:IC USB CTRL HI-SPEED 128TFBGA RoHS:是 類別:集成電路 (IC) >> 接口 - 控制器 系列:- 標(biāo)準(zhǔn)包裝:4,900 系列:- 控制器類型:USB 2.0 控制器 接口:串行 電源電壓:3 V ~ 3.6 V 電流 - 電源:135mA 工作溫度:0°C ~ 70°C 安裝類型:表面貼裝 封裝/外殼:36-VFQFN 裸露焊盤 供應(yīng)商設(shè)備封裝:36-QFN(6x6) 包裝:* 其它名稱:Q6396337A |

| ISP1761ET-S | 功能描述:IC USB OTG CONTROLLER 128TFBGA RoHS:是 類別:集成電路 (IC) >> 接口 - 控制器 系列:- 標(biāo)準(zhǔn)包裝:4,900 系列:- 控制器類型:USB 2.0 控制器 接口:串行 電源電壓:3 V ~ 3.6 V 電流 - 電源:135mA 工作溫度:0°C ~ 70°C 安裝類型:表面貼裝 封裝/外殼:36-VFQFN 裸露焊盤 供應(yīng)商設(shè)備封裝:36-QFN(6x6) 包裝:* 其它名稱:Q6396337A |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。