- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄373063 > K4H560838E-ULB3 (SAMSUNG SEMICONDUCTOR CO. LTD.) 256Mb E-die DDR SDRAM Specification 66 TSOP-II with Pb-Free (RoHS compliant) PDF資料下載

參數(shù)資料

| 型號(hào): | K4H560838E-ULB3 |

| 廠商: | SAMSUNG SEMICONDUCTOR CO. LTD. |

| 英文描述: | 256Mb E-die DDR SDRAM Specification 66 TSOP-II with Pb-Free (RoHS compliant) |

| 中文描述: | 256Mb的電子芯片與DDR SDRAM的規(guī)格鉛66 TSOP-II免費(fèi)(符合RoHS) |

| 文件頁(yè)數(shù): | 17/19頁(yè) |

| 文件大小: | 171K |

| 代理商: | K4H560838E-ULB3 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)當(dāng)前第17頁(yè)第18頁(yè)第19頁(yè)

DDR SDRAM

DDR SDRAM 256Mb F-die (x8, x16)

System Characteristics for DDR SDRAM

The following specification parameters are required in systems using DDR400 devices to ensure proper system perfor-

mance. these characteristics are for system simulation purposes and are guaranteed by design.

Rev. 1.1 August. 2003

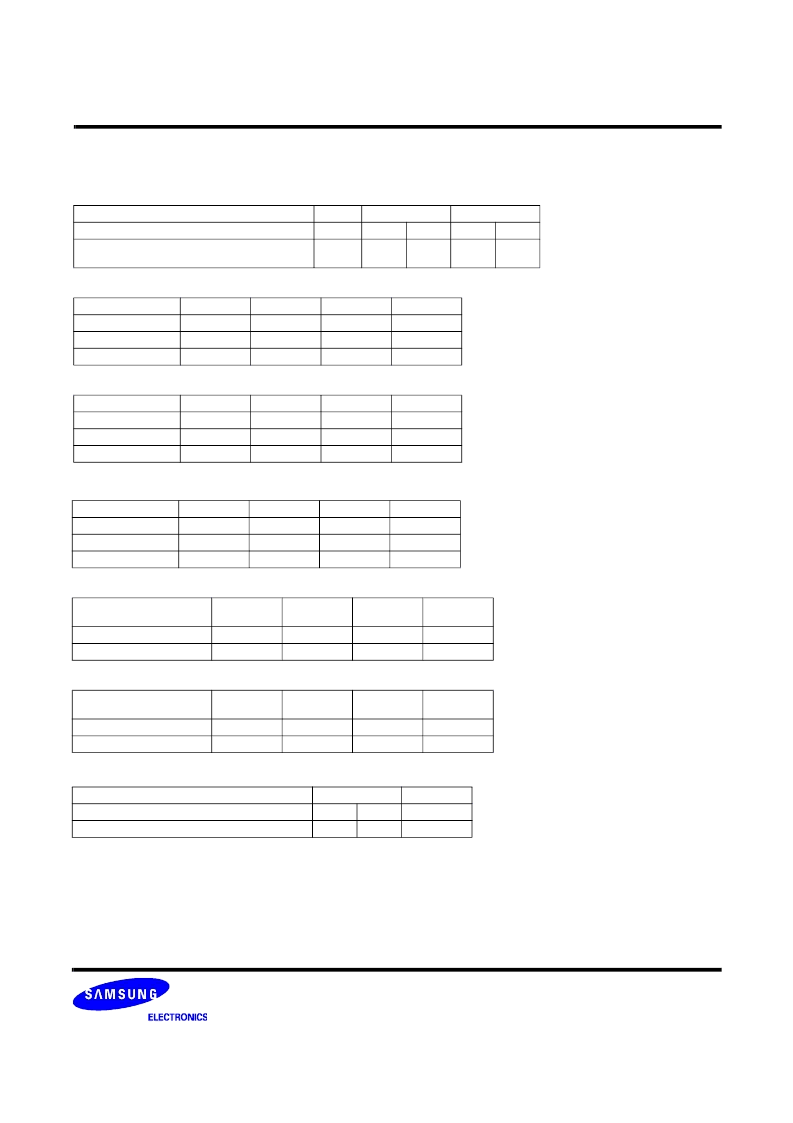

Table 4 : Input/Output Setup & Hold Derating for Rise/Fall Delta Slew Rate

Table 5 : Output Slew Rate Characteristice (X8 Devices only)

Table 6 : Output Slew Rate Characteristice (X16 Devices only)

Table 7 : Output Slew Rate Matching Ratio Characteristics

Delta Slew Rate

tDS

tDH

Units

Notes

+/- 0.0 V/ns

0

0

ps

i

+/- 0.25 V/ns

+50

+50

ps

i

+/- 0.5 V/ns

+100

+100

ps

i

Slew Rate Characteristic

Typical Range

(V/ns)

Minimum

(V/ns)

Maximum

(V/ns)

Notes

Pullup Slew Rate

1.2 ~ 2.5

1.0

4.5

a,c,d,f,g

Pulldown slew

1.2 ~ 2.5

1.0

4.5

b,c,d,f,g

Slew Rate Characteristic

Typical Range

(V/ns)

Minimum

(V/ns)

Maximum

(V/ns)

Notes

Pullup Slew Rate

1.2 ~ 2.5

0.7

5.0

a,c,d,f,g

Pulldown slew

1.2 ~ 2.5

0.7

5.0

b,c,d,f,g

AC CHARACTERISTICS

DDR400

PARAMETER

MIN

MAX

Notes

Output Slew Rate Matching Ratio (Pullup to Pulldown)

-

-

e,k

Table 1 :

Input Slew Rate for DQ, DQS, and DM

Table 2

:

Input Setup & Hold Time Derating for Slew Rate

Table 3 : Input/Output Setup & Hold Time Derating for Slew Rate

AC CHARACTERISTICS

DDR400

PARAMETER

SYMBOL

MIN

MAX

Units

Notes

DQ/DM/DQS input slew rate measured between

VIH(DC), VIL(DC) and VIL(DC), VIH(DC)

DCSLEW

0.5

4.0

V/ns

a, k

Input Slew Rate

tIS

tIH

Units

Notes

0.5 V/ns

0

0

ps

h

0.4 V/ns

+50

0

ps

h

0.3 V/ns

+100

0

ps

h

Input Slew Rate

tDS

tDH

Units

Notes

0.5 V/ns

0

0

ps

j

0.4 V/ns

+75

+75

ps

j

0.3 V/ns

+150

+150

ps

j

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| K4H560838M-TCA2 | 128Mb DDR SDRAM |

| K4H560838M-TCB0 | 128Mb DDR SDRAM |

| K4H560838M-TLA0 | 128Mb DDR SDRAM |

| K4H560838M-TLA2 | 10-Bit, 38 kSPS ADC Serial Out, On-Chip System Clock, 11 Ch. 20-SOIC |

| K4H560838M-TLB0 | 128Mb DDR SDRAM |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| K4H560838E-VC/LA2 | 制造商:SAMSUNG 制造商全稱:Samsung semiconductor 功能描述:256Mb E-die DDR SDRAM Specification 54 sTSOP-II with Pb-Free (RoHS compliant) |

| K4H560838E-VC/LB0 | 制造商:SAMSUNG 制造商全稱:Samsung semiconductor 功能描述:256Mb E-die DDR SDRAM Specification 54 sTSOP-II with Pb-Free (RoHS compliant) |

| K4H560838E-VC/LB3 | 制造商:SAMSUNG 制造商全稱:Samsung semiconductor 功能描述:256Mb E-die DDR SDRAM Specification 54 sTSOP-II with Pb-Free (RoHS compliant) |

| K4H560838E-VCA2 | 制造商:SAMSUNG 制造商全稱:Samsung semiconductor 功能描述:256Mb E-die DDR SDRAM Specification 54 sTSOP-II with Pb-Free (RoHS compliant) |

| K4H560838E-VCB0 | 制造商:SAMSUNG 制造商全稱:Samsung semiconductor 功能描述:256Mb E-die DDR SDRAM Specification 54 sTSOP-II with Pb-Free (RoHS compliant) |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。