- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄373081 > K7I641884M (SAMSUNG SEMICONDUCTOR CO. LTD.) 72Mb DDRII SRAM Specification PDF資料下載

參數(shù)資料

| 型號(hào): | K7I641884M |

| 廠商: | SAMSUNG SEMICONDUCTOR CO. LTD. |

| 英文描述: | 72Mb DDRII SRAM Specification |

| 中文描述: | 72Mb SRAM的規(guī)范條DDRII |

| 文件頁(yè)數(shù): | 3/18頁(yè) |

| 文件大?。?/td> | 424K |

| 代理商: | K7I641884M |

第1頁(yè)第2頁(yè)當(dāng)前第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)

2Mx36 & 4Mx18 DDRII CIO b4 SRAM

K7I643684M

K7I641884M

- 3 -

2Mx36-bit, 4Mx18-bit DDRII CIO b4 SRAM

FEATURES

1.8V+0.1V/-0.1V Power Supply.

DLL circuitry for wide output data valid window and future fre-

quency scaling.

I/O Supply Voltage 1.5V+0.1V/-0.1V for 1.5V I/O,

1.8V+0.1V/-0.1V for 1.8V I/O

.

Pipelined, double-data rate operation.

Common data input/output bus.

HSTL I/O

Full data coherency, providing most current data.

Synchronous pipeline read with self timed late write.

Registered address, control and data input/output.

DDR(Double Data Rate) Interface on read and write ports.

Fixed 4-bit burst for both read and write operation.

Clock-stop supports to reduce current.

Two input clocks(K and K) for accurate DDR timing at clock

rising edges only.

Two input clocks for output data(C and C) to minimize

clock-skew and flight-time mismatches.

Two echo clocks (CQ and CQ) to enhance output data

traceability.

Single address bus.

Byte write function.

Simple depth expansion with no data contention.

Programmable output impedance.

JTAG 1149.1 compatible test access port.

165FBGA(11x15 ball array FBGA) with body size of 15x17mm

& Lead Free

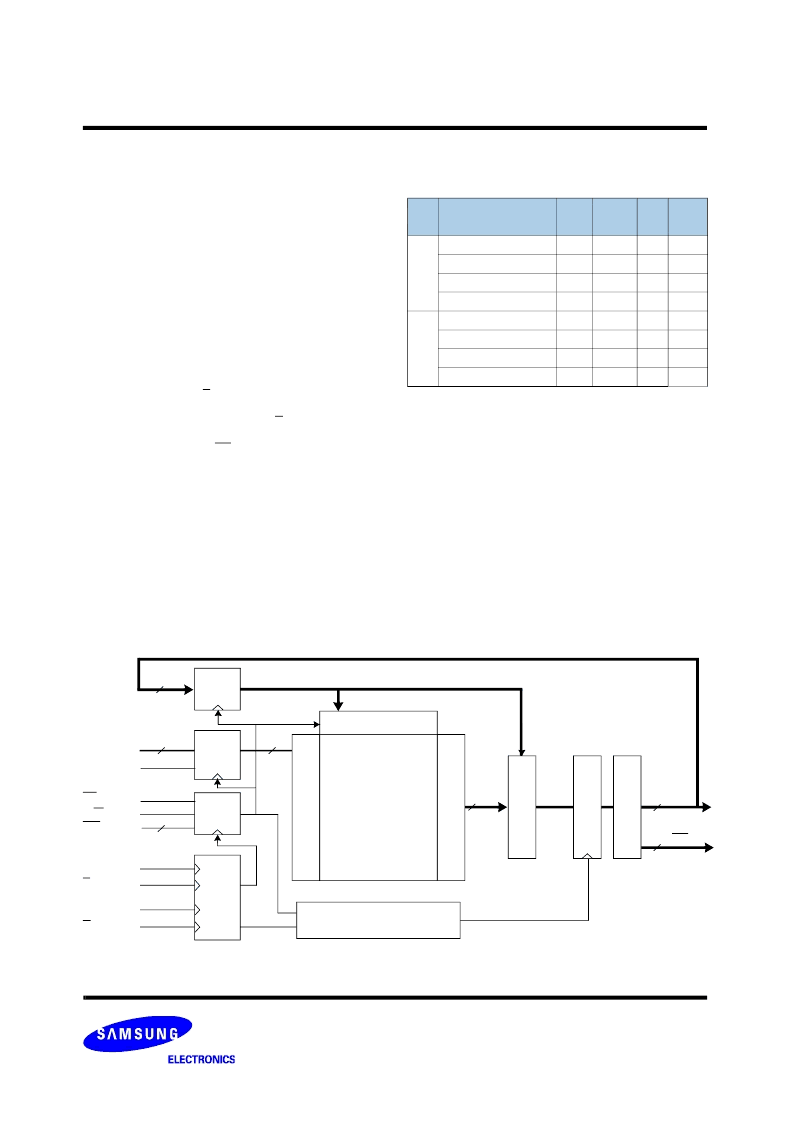

FUNCTIONAL BLOCK DIAGRAM

* -F(E)C(I)

F(E) [Package type]: E-Pb Free, F-Pb

C(I) [Operating Temperature]: C-Commercial, I-Industrial

Org.

Part

Number

Cycle

Time

Access

Time

Unit

RoHS

Avail.

X36

K7I643684M-F(E)C(I)30

3.3

0.45

ns

√

√

K7I643684M-F(E)C(I)25

4.0

0.45

ns

K7I643684M-FC(I)20

5.0

0.45

ns

K7I643684M-FC(I)16

6.0

0.50

ns

X18

K7I641884M-F(E)C(I)30

3.3

0.45

ns

√

√

K7I641884M-F(E)C(I)25

4.0

0.45

ns

K7I641884M-FC(I)20

5.0

0.45

ns

K7I641884M-FC(I)16

6.0

0.50

ns

LD

R/W

BW

X

ADDRESS

A0,A1

C

C

ADD REG

&

BURST

LOGIC

DATA

REG

CLK

GEN

CTRL

LOGIC

2Mx36

(4Mx18)

MEMORY

ARRAY

WRITE DRIVER

K

K

4(or 2)

DQ

SELECT OUTPUT CONTROL

S

W

O

O

O

Notes

: 1. Numbers in ( ) are for x18 device.

19

19 (or 20)

36 (or 18)

36 (or 18)

72

72

(Echo Clock out)

CQ, CQ

36 (or 18)

DDRII SRAM and Double Data Rate comprise a new family of products developed by Cypress, Renesas, IDT, NEC and Samsung technology.

(or 20)

(or 36)

(or 36)

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| K7I641884M-CE25 | 72Mb DDRII SRAM Specification |

| K7I641884M-CE30 | 72Mb DDRII SRAM Specification |

| K7I641884M-CI25 | 72Mb DDRII SRAM Specification |

| K7I641884M-CI30 | 72Mb DDRII SRAM Specification |

| K7I641884M-FC16 | 72Mb DDRII SRAM Specification |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| K7I641884M-CE25 | 制造商:SAMSUNG 制造商全稱:Samsung semiconductor 功能描述:72Mb DDRII SRAM Specification |

| K7I641884M-CE30 | 制造商:SAMSUNG 制造商全稱:Samsung semiconductor 功能描述:72Mb DDRII SRAM Specification |

| K7I641884M-CI25 | 制造商:SAMSUNG 制造商全稱:Samsung semiconductor 功能描述:72Mb DDRII SRAM Specification |

| K7I641884M-CI30 | 制造商:SAMSUNG 制造商全稱:Samsung semiconductor 功能描述:72Mb DDRII SRAM Specification |

| K7I641884M-FC16 | 制造商:SAMSUNG 制造商全稱:Samsung semiconductor 功能描述:72Mb DDRII SRAM Specification |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。