- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄373087 > K9F1208U0 (SAMSUNG SEMICONDUCTOR CO. LTD.) 64M x 8 Bit NAND Flash Memory PDF資料下載

參數(shù)資料

| 型號: | K9F1208U0 |

| 廠商: | SAMSUNG SEMICONDUCTOR CO. LTD. |

| 英文描述: | 64M x 8 Bit NAND Flash Memory |

| 中文描述: | 6400 × 8位NAND閃存 |

| 文件頁數(shù): | 6/41頁 |

| 文件大?。?/td> | 1139K |

| 代理商: | K9F1208U0 |

第1頁第2頁第3頁第4頁第5頁當前第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁

K9F1208U0M-YCB0, K9F1208U0M-YIB0

FLASH MEMORY

6

64M x 8 Bit NAND Flash Memory

The K9F1208U0M is a 64M(67,108,864)x8bit NAND Flash

Memory with a spare 2,048K(2,097,152)x8bit. Its NAND cell

provides the most cost-effective solution for the solid state

mass storage market. A program operation can be performed in

typical 200

μ

s on the 528-byte page and an erase operation can

be performed in typical 2ms on a 16K-byte block. Data in the

page can be read out at 50ns cycle time per byte. The I/O pins

serve as the ports for address and data input/output as well as

command inputs. The on-chip write controller automates all

program and erase functions including pulse repetition, where

required, and internal verification and margining of data. Even

the write-intensive systems can take advantage of the

K9F1208U0M’s extended reliability of 100K program/erase

cycles by providing ECC(Error Correcting Code) with real time

mapping-out algorithm. The K9F1208U0M-YCB0/YIB0 is an

optimum solution for large nonvolatile storage applications such

as solid state file storage and other portable applications requir-

ing non-volatility.

General Description

Features

Voltage Supply : 2.7V~3.6V

Organization

- Memory Cell Array : (64M + 2,048K)bit x 8bit

- Data Register : (512 + 16)bit x8bit multipled by four planes

Automatic Program and Erase

- Page Program : (512 + 16)Byte

- Block Erase : (16K + 512)Byte

528-Byte Page Read Operation

- Random Access : 12

μ

s(Max.)

- Serial Page Access : 50ns(Min.)

Fast Write Cycle Time

- Program time : 200

μ

s(Typ.)

- Block Erase Time : 2ms(Typ.)

Command/Address/Data Multiplexed I/O Port

Hardware Data Protection

- Program/Erase Lockout During Power Transitions

Reliable CMOS Floating-Gate Technology

- Endurance : 100K Program/Erase Cycles

- Data Retention : 10 Years

Command Register Operation

Intelligent Copy-Back Operation

Package :

- K9F1208U0M-YCB0, K9F1208U0M-YIB0 :

48 - Pin TSOP I (12 x 20 / 0.5 mm pitch)

Simultaneous Four Page/Block Program/Erase

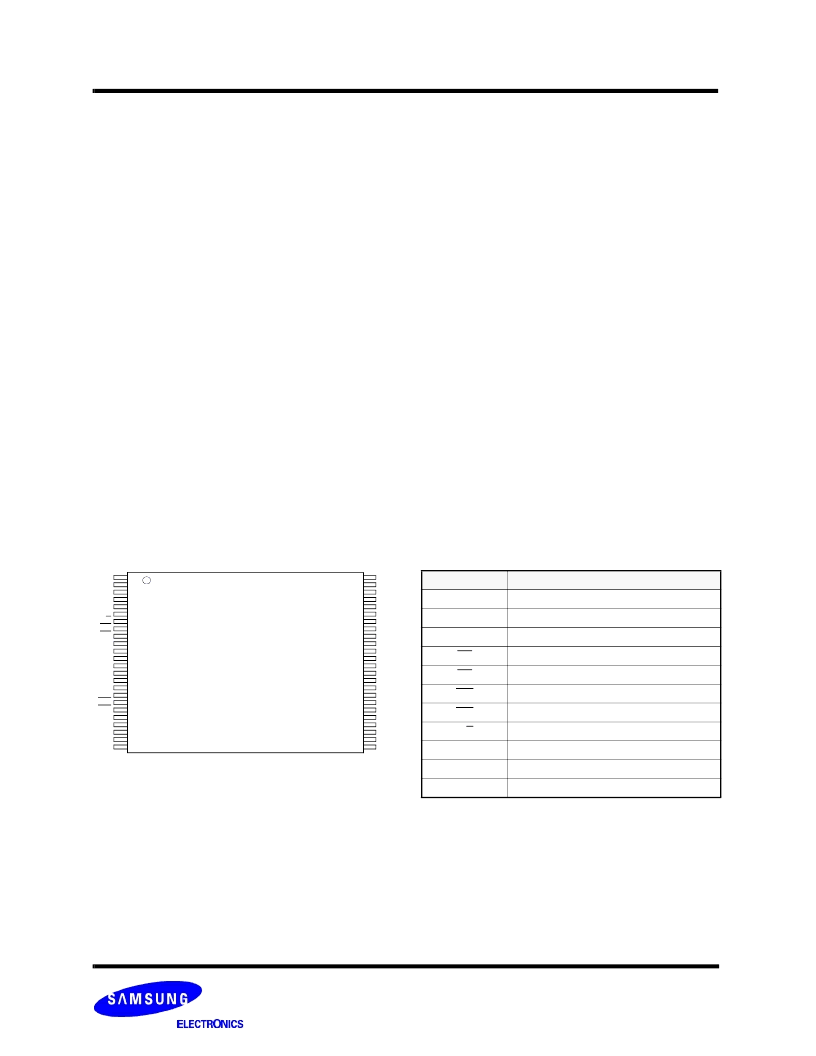

Pin Configuration

NOTE

: Connect all V

CC

and V

SS

pins of each device to common power supply outputs.

Do not leave V

CC

or V

SS

disconnected.

48-pin TSOP1

Standard Type

12mm x 20mm

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

32

31

30

29

28

27

26

25

CE

ALE

WE

N.C

N.C

Pin Name

Pin Function

I/O

0

~ I/O

7

Data Input/Outputs

CLE

Command Latch Enable

ALE

Address Latch Enable

CE

Chip Enable

RE

Read Enable

WE

Write Enable

WP

Write Protect

R/B

Ready/Busy output

V

CC

Power(+2.7V~3.6V)

V

SS

Ground

N.C

No Connection

Pin Description

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| K9F1208U0M-YIB0 | 64M x 8 Bit NAND Flash Memory |

| K9F1208U0M-YCB0 | 64M x 8 Bit NAND Flash Memory |

| K9F1208U0M- | 64M x 8 Bit NAND Flash Memory |

| K9F1216U0A | 64M x 8 Bit , 32M x 16 Bit NAND Flash Memory |

| K9F1208U0A | 64M x 8 Bit , 32M x 16 Bit NAND Flash Memory |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| K9F1208U0A | 制造商:SAMSUNG 制造商全稱:Samsung semiconductor 功能描述:64M x 8 Bit , 32M x 16 Bit NAND Flash Memory |

| K9F1208U0A-F | 制造商:SAMSUNG 制造商全稱:Samsung semiconductor 功能描述:64M x 8 Bit , 32M x 16 Bit NAND Flash Memory |

| K9F1208U0A-P | 制造商:SAMSUNG 制造商全稱:Samsung semiconductor 功能描述:64M x 8 Bit , 32M x 16 Bit NAND Flash Memory |

| K9F1208U0A-V | 制造商:SAMSUNG 制造商全稱:Samsung semiconductor 功能描述:64M x 8 Bit , 32M x 16 Bit NAND Flash Memory |

| K9F1208U0A-VIB0T00 | 制造商:Samsung Semiconductor 功能描述: |

發(fā)布緊急采購,3分鐘左右您將得到回復。