- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄373162 > KM68V2000A (SAMSUNG SEMICONDUCTOR CO. LTD.) 256Kx8 bit Low Power and Low Voltage CMOS Static RAM(256K x 8位低功耗和低電壓CMOS 靜態(tài) RAM) PDF資料下載

參數(shù)資料

| 型號(hào): | KM68V2000A |

| 廠商: | SAMSUNG SEMICONDUCTOR CO. LTD. |

| 英文描述: | 256Kx8 bit Low Power and Low Voltage CMOS Static RAM(256K x 8位低功耗和低電壓CMOS 靜態(tài) RAM) |

| 中文描述: | 256Kx8位低功耗和低電壓的CMOS靜態(tài)RAM(256K × 8位低功耗和低電壓的CMOS靜態(tài)RAM)的 |

| 文件頁(yè)數(shù): | 5/9頁(yè) |

| 文件大小: | 130K |

| 代理商: | KM68V2000A |

CMOS SRAM

KM68V2000A, KM68U2000A Family

Revision 0.0

May 1998

Advance

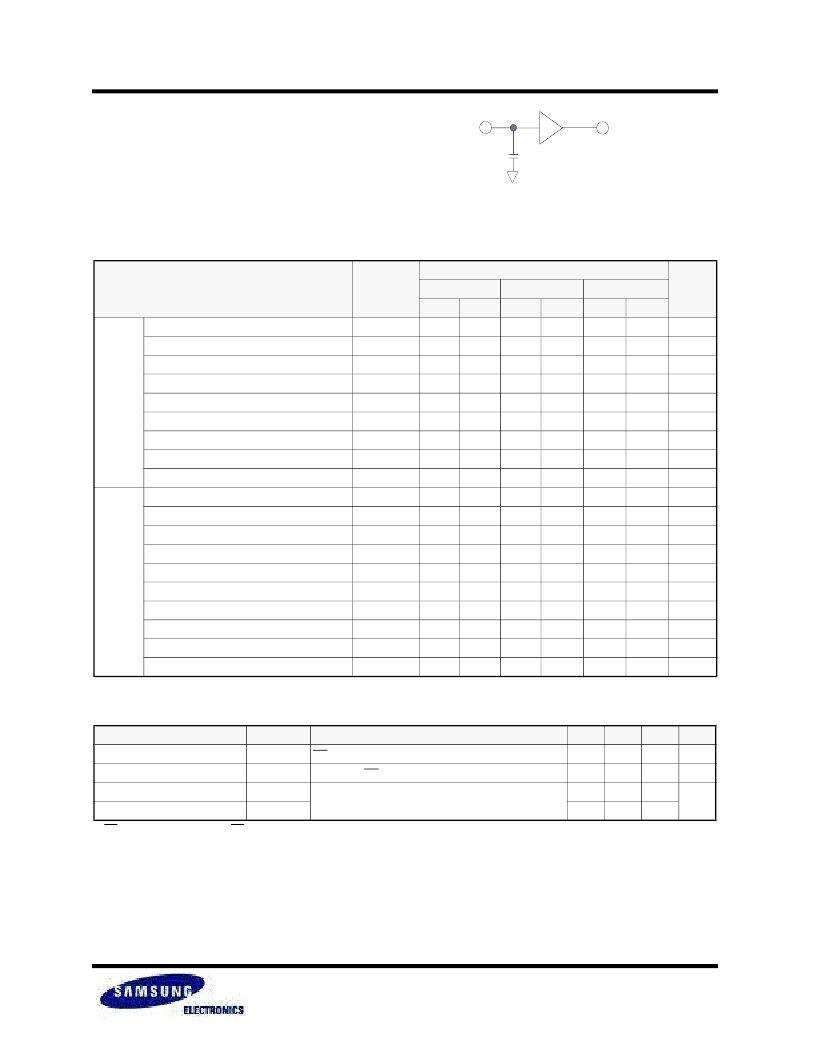

AC CHARACTERISTICS

(KM68V2000A Family : V

CC

=3.0~3.6V, KM68U2000A Family : V

CC

=2.7~3.3V

Commercial Product : T

A

=0 to 70

°

C, Industrial Product : T

A

=-40 to 85

°

C)

Parameter List

Symbol

Speed Bins

Units

70ns

85ns

100ns

Min

Max

Min

Max

Min

Max

Read

Read cycle time

t

RC

70

-

85

-

100

-

ns

Address access time

t

AA

-

70

-

85

-

100

ns

Chip select to output

t

CO1

, t

CO2

-

70

-

85

-

100

ns

Output enable to valid output

t

OE

-

35

-

40

-

50

ns

Chip select to low-Z output

t

LZ

10

-

10

-

10

-

ns

Output enable to low-Z output

t

OLZ

5

-

5

-

5

-

ns

Chip disable to high-Z output

t

HZ

0

25

0

25

0

30

ns

Output disable to high-Z output

t

OHZ

0

25

0

25

0

30

ns

Output hold from address change

t

OH

10

-

15

-

15

-

ns

Write

Write cycle time

t

WC

70

-

85

-

100

-

ns

Chip select to end of write

t

CW

60

-

70

-

80

-

ns

Address set-up time

t

AS

0

-

0

-

0

-

ns

Address valid to end of write

t

AW

60

-

70

-

80

-

ns

Write pulse width

t

WP

55

-

60

-

70

-

ns

Write recovery time

t

WR

0

-

0

-

0

-

ns

Write to output high-Z

t

WHZ

0

25

0

30

0

30

ns

Data to write time overlap

t

DW

30

-

35

-

40

-

ns

Data hold from write time

t

DH

0

-

0

-

0

-

ns

End write to output low-Z

t

OW

5

-

5

-

5

-

ns

C

L

1)

1. Including scope and jig capacitance

AC OPERATING CONDITIONS

TEST CONDITIONS

( Test Load and Input/Output Reference)

Input pulse level : 0.4 to 2.2V

Input rising and falling time : 5ns

Input and output reference voltage :1.5V

Output load(see right) : C

L

=100pF+1TTL

C

L

=30pF+1TTL

DATA RETENTION CHARACTERISTICS

1. CS

1

≥

Vcc-0.2V, CS

2

≥

Vcc-0.2V(CS

1

controlled) or CS

2

≤

0.2V(CS

2

controlled)

2. Industrial Prod

ucts = 15

μ

A

Item

Symbol

Test Condition

Min

Typ

Max

Unit

Vcc for data retention

V

DR

CS

1

≥

Vcc-0.2V

1)

Vcc=3.0V, CS

1

≥

Vcc-0.2V

1)

2.0

-

3.6

V

Data retention current

I

DR

-

0.2

10

2)

μ

A

Data retention set-up time

t

SDR

See data retention waveform

0

-

-

ms

Recovery time

t

RDR

5

-

-

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| KM68U2000 | 256Kx8 bit Low Power and Low Voltage CMOS Static RAM(256K x 8位低功耗和低電壓CMOS 靜態(tài) RAM) |

| KM68V2000 | 256Kx8 bit Low Power and Low Voltage CMOS Static RAM(256K x 8位低功耗和低電壓CMOS 靜態(tài) RAM) |

| KM68U4000A | 512K x8 bit Low Power and Low Voltage CMOS Static RAM(512K x8位低功耗低電壓CMOS 靜態(tài) RAM) |

| KM68V4000A | 512K x8 bit Low Power and Low Voltage CMOS Static RAM(512K x8位低功耗低電壓CMOS 靜態(tài) RAM) |

| KM68U4000B | 512K x8 bit Low Power and Low Voltage CMOS Static RAM(512K x8位低功耗低電壓CMOS 靜態(tài) RAM) |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| KM68V2000ALTGI-7L | 制造商:Samsung Electro-Mechanics 功能描述:256K X 8 STANDARD SRAM, 70 ns, PDSO32 |

| KM68V257C | 制造商:SAMSUNG 制造商全稱:Samsung semiconductor 功能描述:32Kx8 Bit High Speed Static RAM(3.3V Operating), Evolutionary Pin out. |

| KM68V257C-15 | 制造商:SAMSUNG 制造商全稱:Samsung semiconductor 功能描述:32Kx8 Bit High Speed Static RAM(3.3V Operating), Evolutionary Pin out. |

| KM68V257C-17 | 制造商:SAMSUNG 制造商全稱:Samsung semiconductor 功能描述:32Kx8 Bit High Speed Static RAM(3.3V Operating), Evolutionary Pin out. |

| KM68V257E | 制造商:SAMSUNG 制造商全稱:Samsung semiconductor 功能描述:32Kx8 Bit High-Speed CMOS Static RAM (3.3V Operating) |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。