- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄10119 > KSZ8041FTLI TR (Micrel Inc)TXRX PHY 10/100 SGL LP 48TQFP PDF資料下載

參數(shù)資料

| 型號: | KSZ8041FTLI TR |

| 廠商: | Micrel Inc |

| 文件頁數(shù): | 2/58頁 |

| 文件大?。?/td> | 0K |

| 描述: | TXRX PHY 10/100 SGL LP 48TQFP |

| 標(biāo)準(zhǔn)包裝: | 1,000 |

| 類型: | 收發(fā)器 |

| 驅(qū)動器/接收器數(shù): | 1/1 |

| 規(guī)程: | SMII |

| 電源電壓: | 3.135 V ~ 3.465 V |

| 安裝類型: | 表面貼裝 |

| 封裝/外殼: | 48-TQFP |

| 供應(yīng)商設(shè)備封裝: | 48-TQFP(7x7) |

| 包裝: | 帶卷 (TR) |

第1頁當(dāng)前第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁

Micrel, Inc.

KSZ8041TL/FTL

April 2007

10

M9999-042707-1.1

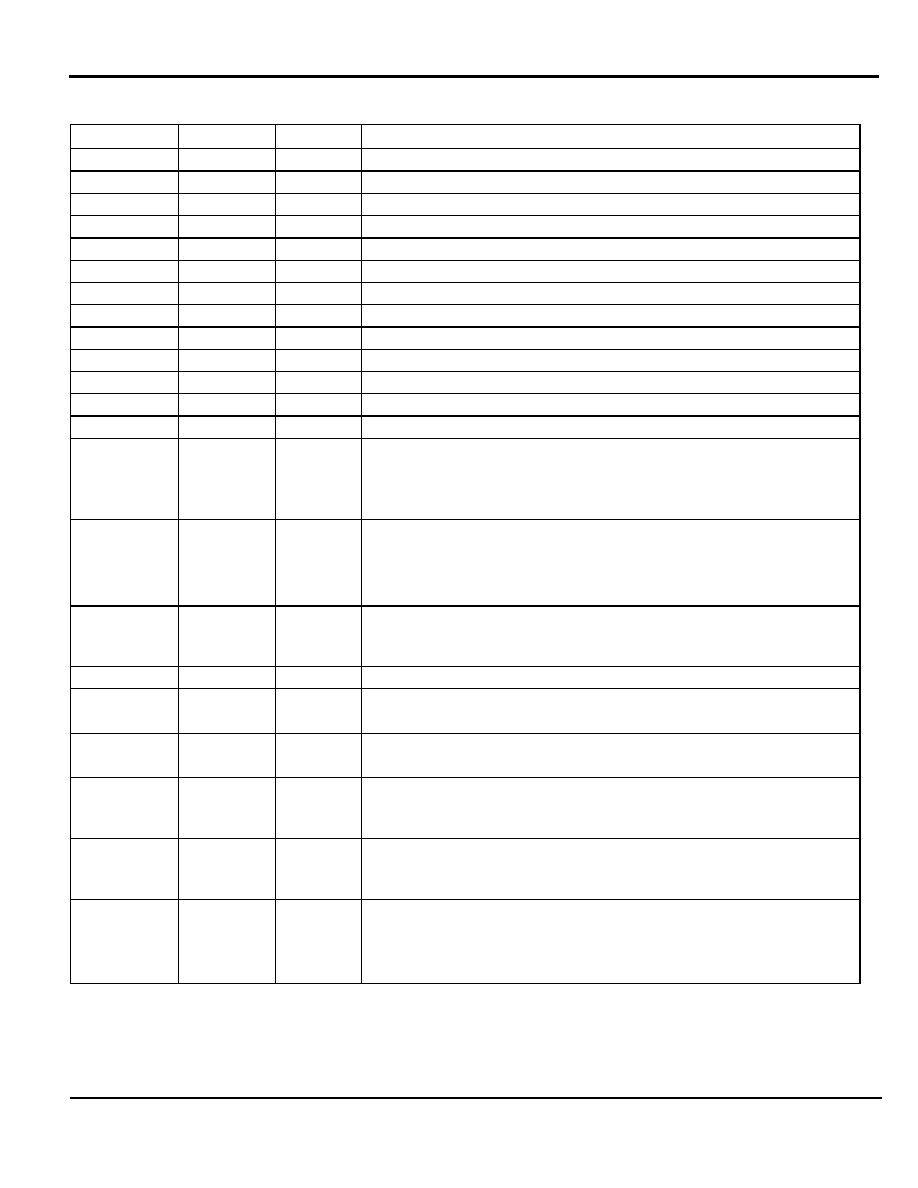

Pin Description

Pin Number

Pin Name

Type

(1)

Pin Function

1

GND

Gnd

Ground

2

GND

Gnd

Ground

3

GND

Gnd

Ground

4

VDDA_1.8

P

1.8V analog VDD

5

VDDA_1.8

P

1.8V analog VDD

6

V1.8_OUT

P

1.8V output voltage from chip

7

VDDA_3.3

P

3.3V analog VDD

8

VDDA_3.3

P

3.3V analog VDD

9

RX-

I/O

Physical receive or transmit signal (- differential)

10

RX+

I/O

Physical receive or transmit signal (+ differential)

11

TX-

I/O

Physical transmit or receive signal (- differential)

12

TX+

I/O

Physical transmit or receive signal (+ differential)

13

GND

Gnd

Ground

14

XO

O

Crystal feedback

This pin is used only in MII mode when a 25 MHz crystal is used.

This pin is a no connect if oscillator or external clock source is used, or if RMII

mode or SMII mode is selected.

15

XI /

REFCLK /

CLOCK

I

Crystal / Oscillator / External Clock Input

MII Mode:

25MHz +/-50ppm (crystal, oscillator, or external clock)

RMII Mode:

50MHz +/-50ppm (oscillator, or external clock only)

SMII Mode:

125MHz +/-100ppm (oscillator, or external clock only)

16

REXT

I/O

Set physical transmit output current

Connect a 6.49K

resistor in parallel with a 100pF capacitor to ground on this

pin. See KSZ8041TL-FTL reference schematics.

17

GND

Gnd

Ground

18

MDIO

I/O

Management Interface (MII) Data I/O

This pin requires an external 4.7K

pull-up resistor.

19

MDC

I

Management Interface (MII) Clock Input

This pin is synchronous to the MDIO data interface.

20

RXD3 /

PHYAD0

Ipu/O

MII Mode:

Receive Data Output[3]

(2)

/

Config Mode:

The pull-up/pull-down value is latched as PHYADDR[0] during

power-up / reset. See “Strapping Options” section for details.

21

RXD2 /

PHYAD1

Ipd/O

MII Mode:

Receive Data Output[2]

(2)

/

Config Mode:

The pull-up/pull-down value is latched as PHYADDR[1] during

power-up / reset. See “Strapping Options” section for details.

22

RXD1 /

RXD[1] /

PHYAD2

Ipd/O

MII Mode:

Receive Data Output[1]

(2)

/

RMII Mode:

Receive Data Output[1]

(3)

/

Config Mode:

The pull-up/pull-down value is latched as PHYADDR[2] during

power-up / reset. See “Strapping Options” section for details.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| IDT72421L25PF | IC FIFO 64X9 SYNC 25NS 32-TQFP |

| VI-2NM-MX-F2 | CONVERTER MOD DC/DC 10V 75W |

| VI-J4T-MX-S | CONVERTER MOD DC/DC 6.5V 75W |

| VI-2NM-MX-F1 | CONVERTER MOD DC/DC 10V 75W |

| LT1039CSW#TRPBF | IC DRIVR/RCVR TRPLE-RS232 18SOIC |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| KSZ8041FTL-S | 功能描述:以太網(wǎng) IC 10/100 PHY Fibre version and SMII RoHS:否 制造商:Micrel 產(chǎn)品:Ethernet Switches 收發(fā)器數(shù)量:2 數(shù)據(jù)速率:10 Mb/s, 100 Mb/s 電源電壓-最大:1.25 V, 3.45 V 電源電壓-最小:1.15 V, 3.15 V 最大工作溫度:+ 85 C 封裝 / 箱體:QFN-64 封裝:Tray |

| KSZ8041MLL | 功能描述:以太網(wǎng) IC 3.3V, 10Base-T/100Base-TX Physical Layer Transceiver with MII Support - Lead Free RoHS:否 制造商:Micrel 產(chǎn)品:Ethernet Switches 收發(fā)器數(shù)量:2 數(shù)據(jù)速率:10 Mb/s, 100 Mb/s 電源電壓-最大:1.25 V, 3.45 V 電源電壓-最小:1.15 V, 3.15 V 最大工作溫度:+ 85 C 封裝 / 箱體:QFN-64 封裝:Tray |

| KSZ8041MLL TR | 功能描述:以太網(wǎng) IC 3.3V, 10Base-T/100Base-TX Physical Layer Transceiver with MII Support - Lead Free RoHS:否 制造商:Micrel 產(chǎn)品:Ethernet Switches 收發(fā)器數(shù)量:2 數(shù)據(jù)速率:10 Mb/s, 100 Mb/s 電源電壓-最大:1.25 V, 3.45 V 電源電壓-最小:1.15 V, 3.15 V 最大工作溫度:+ 85 C 封裝 / 箱體:QFN-64 封裝:Tray |

| KSZ8041MLLI | 功能描述:以太網(wǎng) IC 3.3V, 10Base-T/100Base-TX Physical Layer Transceiver with MII support (Industrial grade, Lead Free) RoHS:否 制造商:Micrel 產(chǎn)品:Ethernet Switches 收發(fā)器數(shù)量:2 數(shù)據(jù)速率:10 Mb/s, 100 Mb/s 電源電壓-最大:1.25 V, 3.45 V 電源電壓-最小:1.15 V, 3.15 V 最大工作溫度:+ 85 C 封裝 / 箱體:QFN-64 封裝:Tray |

| KSZ8041MLLI TR | 功能描述:以太網(wǎng) IC 3.3V, 10Base-T/100Base-TX Physical Layer Transceiver with MII support (Industrial grade, Lead Free) RoHS:否 制造商:Micrel 產(chǎn)品:Ethernet Switches 收發(fā)器數(shù)量:2 數(shù)據(jù)速率:10 Mb/s, 100 Mb/s 電源電壓-最大:1.25 V, 3.45 V 電源電壓-最小:1.15 V, 3.15 V 最大工作溫度:+ 85 C 封裝 / 箱體:QFN-64 封裝:Tray |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。