- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄11591 > KSZ8842-16MBL (Micrel Inc)IC MAC CTLR 2PORT ETH 100-LFBGA PDF資料下載

參數(shù)資料

| 型號(hào): | KSZ8842-16MBL |

| 廠商: | Micrel Inc |

| 文件頁(yè)數(shù): | 74/141頁(yè) |

| 文件大小: | 0K |

| 描述: | IC MAC CTLR 2PORT ETH 100-LFBGA |

| 標(biāo)準(zhǔn)包裝: | 260 |

| 控制器類型: | 以太網(wǎng)開關(guān)控制器 |

| 接口: | PCI |

| 電源電壓: | 3.1 V ~ 3.5 V |

| 工作溫度: | 0°C ~ 70°C |

| 安裝類型: | 表面貼裝 |

| 封裝/外殼: | 100-LBGA |

| 供應(yīng)商設(shè)備封裝: | 100-LFBGA |

| 包裝: | 托盤 |

| 產(chǎn)品目錄頁(yè)面: | 1081 (CN2011-ZH PDF) |

| 配用: | 576-1635-ND - BOARD EVALUATION KSZ8842-16MVL 576-1634-ND - BOARD EVALUATION KSZ8842-16MQL |

| 其它名稱: | 576-3076 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)當(dāng)前第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)第85頁(yè)第86頁(yè)第87頁(yè)第88頁(yè)第89頁(yè)第90頁(yè)第91頁(yè)第92頁(yè)第93頁(yè)第94頁(yè)第95頁(yè)第96頁(yè)第97頁(yè)第98頁(yè)第99頁(yè)第100頁(yè)第101頁(yè)第102頁(yè)第103頁(yè)第104頁(yè)第105頁(yè)第106頁(yè)第107頁(yè)第108頁(yè)第109頁(yè)第110頁(yè)第111頁(yè)第112頁(yè)第113頁(yè)第114頁(yè)第115頁(yè)第116頁(yè)第117頁(yè)第118頁(yè)第119頁(yè)第120頁(yè)第121頁(yè)第122頁(yè)第123頁(yè)第124頁(yè)第125頁(yè)第126頁(yè)第127頁(yè)第128頁(yè)第129頁(yè)第130頁(yè)第131頁(yè)第132頁(yè)第133頁(yè)第134頁(yè)第135頁(yè)第136頁(yè)第137頁(yè)第138頁(yè)第139頁(yè)第140頁(yè)第141頁(yè)

Micrel, Inc.

KSZ8842-16/32 MQL/MVL/MVLI/MBL

October 2007

38

M9999-102207-1.9

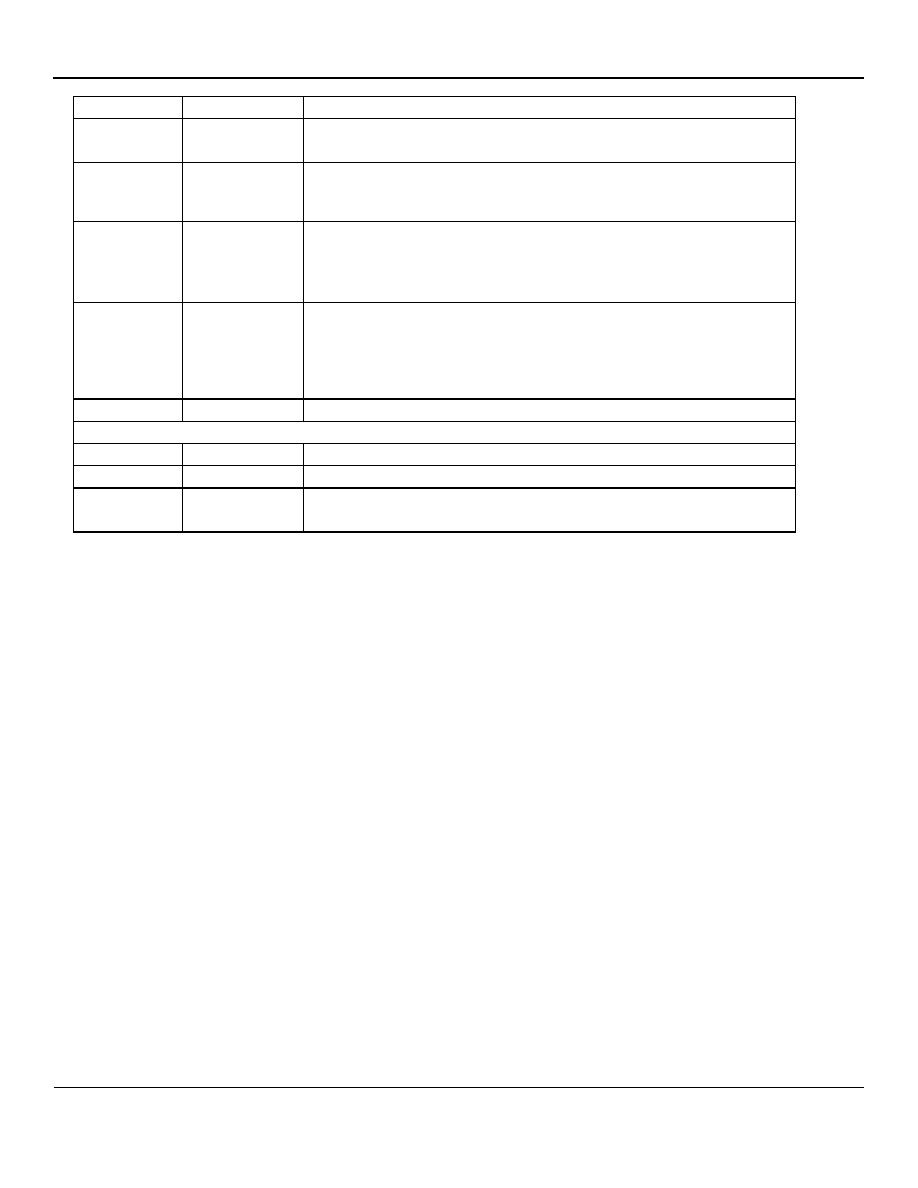

Signal

Type

(1)

Function

CYCLEN

I

For VLBus-like access: used to sample SWR when asserted.

For burst access: used to connect to IOWC# bus signal to indicate burst write.

SWR

I

Write/Read

For VLBus-like access: used to indicate write (High) or read (Low) transfer.

For burst access: used to connect to IORC# bus signal to indicate burst read.

SRDYN

O

Synchronous Ready

For VLBus-like access: exactly the same signal definition of nSRDY in VLBus.

For burst access: insert wait state by the KSZ8842M whenever necessary

during the Data Register access.

RDYRTNN

I

Ready Return

For VLBus-like access: exactly like RDYRTNN signal in VLBus to end the

cycle.

For burst access: exactly like EXRDY signal in EISA to insert wait states. Note

that the wait states are inserted by system logic (memory) not by KSZ8842M.

BCLK

I

Bus Clock

Asynchronous Transfer Signals

RDN

I

Asynchronous Read

WRN

I

Asynchronous Write

ARDY

O

Asynchronous Ready

This signal is asserted (low) to insert wait states.

Note 1: I = Input. O = Output. I/O = Bi-directional.

Table 2. Bus Interface Unit Signal Grouping

Regardless of whether the transfer is synchronous or asynchronous, if the address latch is required, use the rising edge of

ADSN to latch the incoming signals A [15:1], AEN, BE3N, BE2N, BE1N, and BE0N.

Note: Whether the transfer is synchronous or asynchronous, if the local device decoder is used, LDEVN will be asserted

to indicate that the KSZ8842M is successfully targeted. Basically, signal LDEVN is a combinatorial decode of AEN and

A[15:4].

Asynchronous Interface

For asynchronous transfers, the asynchronous dedicated signals RDN (for read) or WRN (for write) toggle, but the

synchronous dedicated signals BCLK, CYCLEN, SWR, and RDYRTNN are de-asserted and stay at the same logic level

throughout the entire asynchronous transfer.

There is no data burst support for asynchronous transfer. All asynchronous transfers are single-data transfers. The BIU,

however, provides flexible asynchronous interfacing to communicate with various applications and architectures. Three

major ways of interfacing with the system (host) are.

Interfacing with the system/host relying on local device decoding and having stable address throughout the whole transfer:

1.

The typical example for this application is ISA-like bus interface using latched address signals as shown in the

Figure 17. No additional address latch is required, therefore ADSN should be connected Low. The BIU decodes

A[15:4] and qualifies with AEN (Address Enable) to determine if the KSZ8842M switch is the intended target. The

host utilizes the rising edge of RDN to latch read data and the BIU will use rising edge of WRN to latch write data.

2.

Interfacing with the system/host relying on local device decoding but not having stable address throughout the

entire transfer: the typical example for this application is EISA-like bus (non-burst) interface as shown in the

Figure 18. This type of interface requires ADSN to latch the address on the rising edge. The BIU decodes latched

A[15:4] and qualifies with AEN to determine if the KSZ8842M switch is the intended target. The data transfer is

the same as the first case.

3.

Interfacing with the system/host relying on central decoding (KSZ8842-32 mode only).

The typical example for this application is for an embedded processor having a central decoder on the system

board or within the processor. Connecting the chip select (CS) from system/host to DATACSN bypasses the local

device decoder. When the DATACSN is asserted, it only allows access to the Data Register in 32 bits and BE3N,

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| PIC16F630-E/P | IC MCU FLASH 1KX14 14DIP |

| V72A48C400BF | CONVERTER MOD DC/DC 48V 400W |

| VNC2-48L1B-REEL | IC USB HOST/DEVICE CTRL 48-LQFP |

| V72A48C400BL3 | CONVERTER MOD DC/DC 48V 400W |

| V72A48C400B3 | CONVERTER MOD DC/DC 48V 400W |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| KSZ8842-16MBL-EVAL | 制造商:MICREL 制造商全稱:Micrel Semiconductor 功能描述:2-Port Ethernet Switch with Non-PCI Interface |

| KSZ8842-16MBLI | 功能描述:以太網(wǎng) IC 2-Port Ethernet Switch + Generic (8, 16-Bit) Bus Interface (I-Temp, Lead Free) RoHS:否 制造商:Micrel 產(chǎn)品:Ethernet Switches 收發(fā)器數(shù)量:2 數(shù)據(jù)速率:10 Mb/s, 100 Mb/s 電源電壓-最大:1.25 V, 3.45 V 電源電壓-最小:1.15 V, 3.15 V 最大工作溫度:+ 85 C 封裝 / 箱體:QFN-64 封裝:Tray |

| KSZ8842-16MBLI TR | 功能描述:以太網(wǎng) IC 2-Port Ethernet Switch + Generic (8, 16-Bit) Bus Interface (I-Temp, Lead Free) RoHS:否 制造商:Micrel 產(chǎn)品:Ethernet Switches 收發(fā)器數(shù)量:2 數(shù)據(jù)速率:10 Mb/s, 100 Mb/s 電源電壓-最大:1.25 V, 3.45 V 電源電壓-最小:1.15 V, 3.15 V 最大工作溫度:+ 85 C 封裝 / 箱體:QFN-64 封裝:Tray |

| KSZ8842-16MQL | 功能描述:以太網(wǎng) IC 2-Port Ethernet Switch/Repeater + Generic (8, 16-bit) bus interface(Lead Free) RoHS:否 制造商:Micrel 產(chǎn)品:Ethernet Switches 收發(fā)器數(shù)量:2 數(shù)據(jù)速率:10 Mb/s, 100 Mb/s 電源電壓-最大:1.25 V, 3.45 V 電源電壓-最小:1.15 V, 3.15 V 最大工作溫度:+ 85 C 封裝 / 箱體:QFN-64 封裝:Tray |

| KSZ8842-16MQL-EVAL | 功能描述:以太網(wǎng)開發(fā)工具 KSZ8842-16MQL Evaluation Board RoHS:否 制造商:Micrel 產(chǎn)品:Evaluation Boards 類型:Ethernet Transceivers 工具用于評(píng)估:KSZ8873RLL 接口類型:RMII 工作電源電壓: |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。