- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄358741 > LAN9117-MD (STANDARD MICROSYSTEMS CORP) HIGH PERFORMANCE SINGLE-CHIP 10/100 NON-PCI ETHERNET CONTROLLER PDF資料下載

參數(shù)資料

| 型號(hào): | LAN9117-MD |

| 廠商: | STANDARD MICROSYSTEMS CORP |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | HIGH PERFORMANCE SINGLE-CHIP 10/100 NON-PCI ETHERNET CONTROLLER |

| 中文描述: | 1 CHANNEL(S), 100M bps, LOCAL AREA NETWORK CONTROLLER, PQFP100 |

| 封裝: | TQFP-100 |

| 文件頁(yè)數(shù): | 31/131頁(yè) |

| 文件大小: | 1531K |

| 代理商: | LAN9117-MD |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)當(dāng)前第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)第85頁(yè)第86頁(yè)第87頁(yè)第88頁(yè)第89頁(yè)第90頁(yè)第91頁(yè)第92頁(yè)第93頁(yè)第94頁(yè)第95頁(yè)第96頁(yè)第97頁(yè)第98頁(yè)第99頁(yè)第100頁(yè)第101頁(yè)第102頁(yè)第103頁(yè)第104頁(yè)第105頁(yè)第106頁(yè)第107頁(yè)第108頁(yè)第109頁(yè)第110頁(yè)第111頁(yè)第112頁(yè)第113頁(yè)第114頁(yè)第115頁(yè)第116頁(yè)第117頁(yè)第118頁(yè)第119頁(yè)第120頁(yè)第121頁(yè)第122頁(yè)第123頁(yè)第124頁(yè)第125頁(yè)第126頁(yè)第127頁(yè)第128頁(yè)第129頁(yè)第130頁(yè)第131頁(yè)

High Performance Single-Chip 10/100 Non-PCI Ethernet Controller

Datasheet

SMSC LAN9117

31

Revision 1.1 (05-17-05)

DATASHEET

3.8

General Purpose Timer (GP Timer)

The General Purpose Timer is a programmable block that can be used to generate periodic host

interrupts. The resolution of this timer is 100uS.

The GP Timer loads the GPT_CNT Register with the value in the GPT_LOAD field and begins counting

down when the TIMER_EN bit is set to a ‘1.’ On a reset, or when the TIMER_EN bit changes from

set ‘1’ to cleared ‘0,’ the GPT_CNT field is initialized to FFFFh. The GPT_CNT register is also initialized

to FFFFh on a reset. Software can write the pre-load value into the GPT_LOAD field at any time; e.g.,

before or after the TIMER_EN bit is asserted. The GPT Enable bit TIMER_EN is located in the

GPT_CFG register.

Once enabled, the GPT counts down either until it reaches 0000h or until a new pre-load value is

written to the GPT_LOAD field. At 0000h, the counter wraps around to FFFFh, asserts the GPT

interrupt status bit and the IRQ signal if the GPT_INT_EN bit is set, and continues counting. The GPT

interrupt status bit is in the INT_STS Register. The GPT_INT hardware interrupt can only be set if the

GPT_INT_EN bit is set. GPT_INT is a sticky bit (R/WC); i.e., once the GPT_INT bit is set, it can only

be cleared by writing a ‘1’ to the bit.

3.9

EEPROM Interface

LAN9117 can optionally load its MAC address from an external serial EEPROM. If a properly

configured EEPROM is detected by LAN9117 at power-up, hard reset or soft reset, the ADDRH and

ADDRL registers will be loaded with the contents of the EEPROM. If a properly configured EEPROM

is not detected, it is the responsibility of the host LAN Driver to set the IEEE addresses.

The LAN9117 EEPROM controller also allows the host system to read, write and erase the contents

of the Serial EEPROM. The EEPROM controller supports most “93C46” type EEPROMs configured for

128 x 8-bit operation.

3.9.1

MAC Address Auto-Load

On power-up, hard reset or soft reset, the EEPROM controller attempts to read the first byte of data

from the EEPROM (address 00h). If the value A5h is read from the first address, then the EEPROM

controller will assume that an external Serial EEPROM is present. The EEPROM controller will then

access the next EEPROM byte and send it to the MAC Address register byte 0 (ADDRL[7:0]). This

process will be repeated for the next five bytes of the MAC Address, thus fully programming the 48-

bit MAC address. Once all six bytes have been programmed, the “MAC Address Loaded” bit is set in

the E2P_CMD register. A detailed explanation of the EEPROM byte ordering with respect to the MAC

address is given in

Section 5.4.3, "ADDRL—MAC Address Low Register," on page 100

.

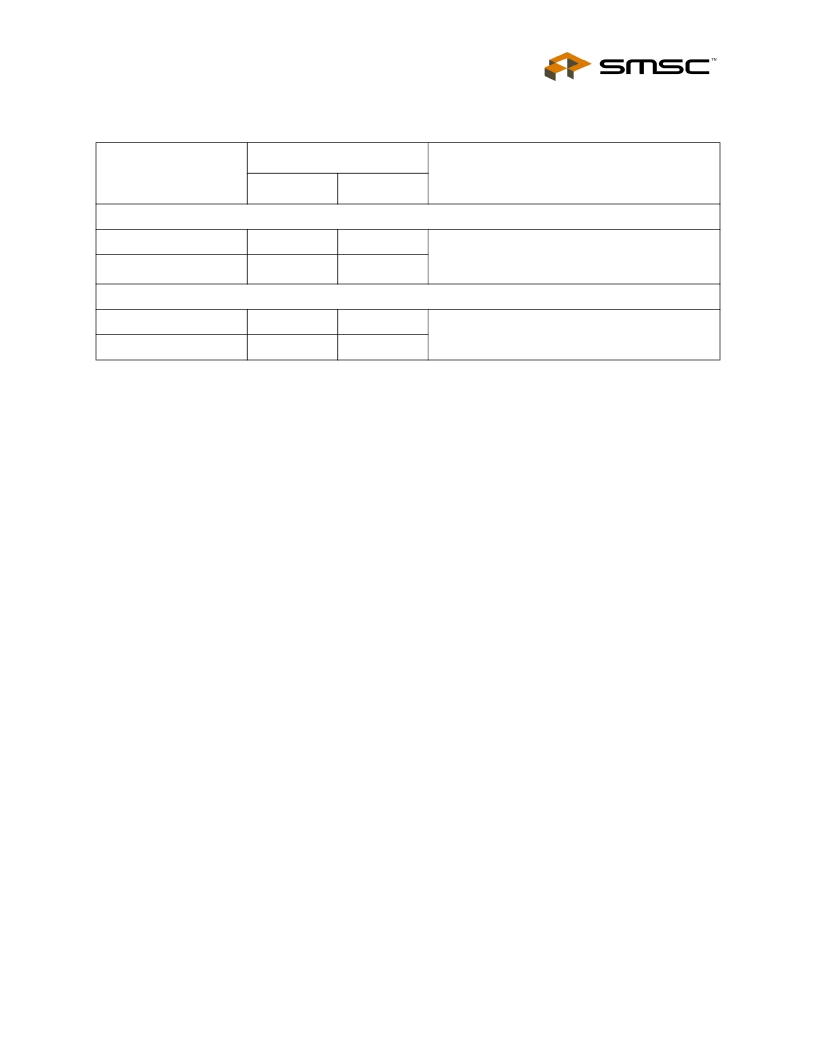

Table 3.7 Byte Lane Mapping

MODE OF OPERATION

DATA PINS

DESCRIPTION

D[15:8]

D[7:0]

Mode 0 (Big Endian Register equal to 0xFFFFFFFF)h

A1 = 0

Byte 3

Byte 2

Note:

This mode can be used by 32-bit

processors operating with an external 16-

bit bus.

A1 = 1

Byte 1

Byte 0

Mode 1 (Big Endian Register not equal to 0xFFFFFFFF)h

A1 = 0

Byte 1

Byte 0

Note:

This mode can also be used by native 16-

bit processors.

A1 = 1

Byte 3

Byte 2

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| LAN9117-MT | HIGH PERFORMANCE SINGLE-CHIP 10/100 NON-PCI ETHERNET CONTROLLER |

| LAN9118 | HIGH PERFORMANCE SINGLE CHIP 10/100NON PCI ETHERNET CONTROLLER |

| LAN9118-MD | HIGH PERFORMANCE SINGLE CHIP 10/100NON PCI ETHERNET CONTROLLER |

| LAN9118-MT | HIGH PERFORMANCE SINGLE CHIP 10/100NON PCI ETHERNET CONTROLLER |

| LAN91C100-FD-SS | FEAST Fast Ethernet Controller with Full Duplex Capability |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| LAN9117-MT | 功能描述:以太網(wǎng) IC HiPerfrm Sngl-Chip 10/100 Ethrnt RoHS:否 制造商:Micrel 產(chǎn)品:Ethernet Switches 收發(fā)器數(shù)量:2 數(shù)據(jù)速率:10 Mb/s, 100 Mb/s 電源電壓-最大:1.25 V, 3.45 V 電源電壓-最小:1.15 V, 3.15 V 最大工作溫度:+ 85 C 封裝 / 箱體:QFN-64 封裝:Tray |

| LAN9118 | 制造商:SMSC 制造商全稱:SMSC 功能描述:High Performance Single-Chip 10/100 Non-PCI Ethernet Controller |

| LAN9118_05 | 制造商:SMSC 制造商全稱:SMSC 功能描述:High Performance Single-Chip 10/100 Non-PCI Ethernet Controller |

| LAN9118_07 | 制造商:SMSC 制造商全稱:SMSC 功能描述:High Performance Single-Chip 10/100 Non-PCI Ethernet Controller |

| LAN9118-MD | 功能描述:以太網(wǎng) IC HiPerfrm Sngl-Chip 10/100 Ethrnt RoHS:否 制造商:Micrel 產(chǎn)品:Ethernet Switches 收發(fā)器數(shù)量:2 數(shù)據(jù)速率:10 Mb/s, 100 Mb/s 電源電壓-最大:1.25 V, 3.45 V 電源電壓-最小:1.15 V, 3.15 V 最大工作溫度:+ 85 C 封裝 / 箱體:QFN-64 封裝:Tray |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。