- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄358741 > LAN91C100FD (SMSC Corporation) FEAST FAST ETHERNET CONTROLLER WITH FULL DUPLEX CAPABILITY PDF資料下載

參數(shù)資料

| 型號: | LAN91C100FD |

| 廠商: | SMSC Corporation |

| 英文描述: | FEAST FAST ETHERNET CONTROLLER WITH FULL DUPLEX CAPABILITY |

| 中文描述: | 宴快速以太網(wǎng)控制器以全雙工能力 |

| 文件頁數(shù): | 26/79頁 |

| 文件大小: | 585K |

| 代理商: | LAN91C100FD |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁當(dāng)前第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁

FEAST Fast Ethernet Controller with Full Duplex Capability

Rev.

10/14/2002

Page 26

SMSC DS – LAN91C100FD Rev. D

PRELIMINARY

PRMS - Promiscuous mode. When set receives all frames. Does not receive its own transmission unless

it is in Full Duplex!

RX_ABORT - This bit is set if a receive frame was aborted due to length longer than 2K bytes. The frame

will not be received. The bit is cleared by RESET or by the CPU writing it low.

Reserved - Must be 0.

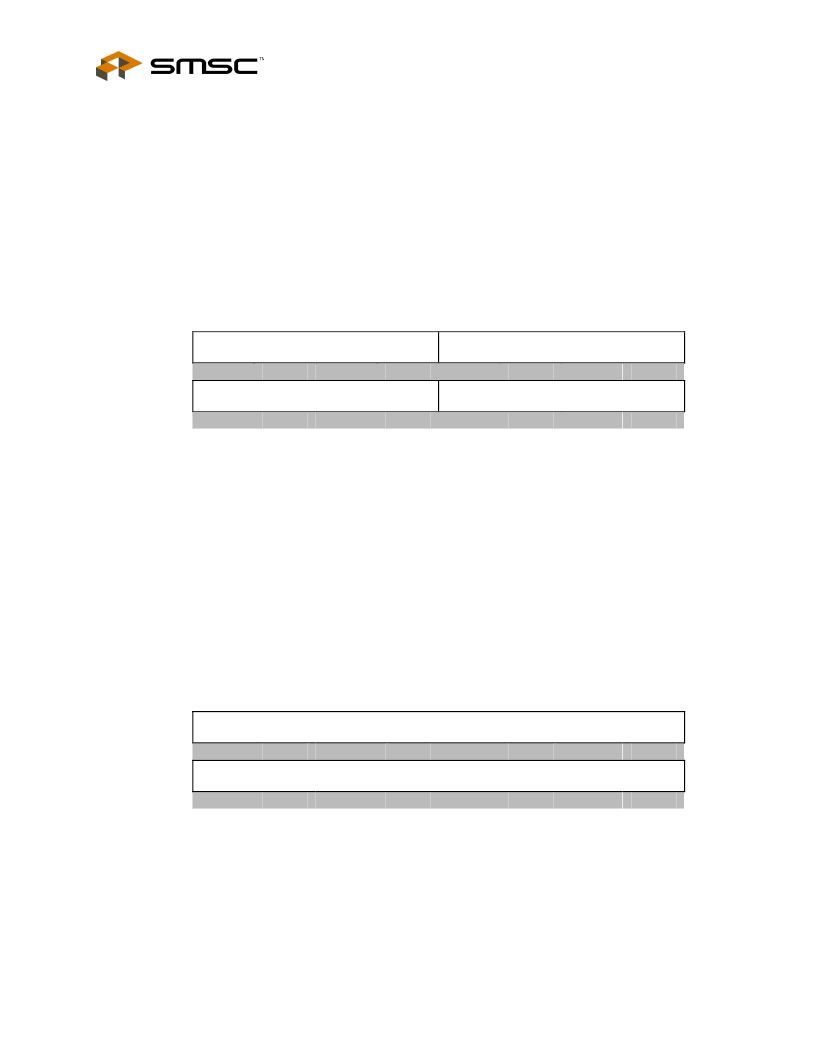

BANK 0

OFFSET

6

NAME

TYPE

SYMBOL

ECR

COUNTER REGISTER

READ ONLY

Counts four parameters for MAC statistics. When any counter reaches 15 an interrupt is issued. All

counters are cleared when reading the register and do not wrap around beyond 15.

HIGH

BYTE

LOW

BYTE

NUMBER OF EXC. DEFFERED TX

NUMBER OF DEFFERED TX

0

0

0

0

0

0

0

0

MULTIPLE COLLISION COUNT

SINGLE COLLISION COUNT

0

0

0

0

0

0

0

0

Each four bit counter is incremented every time the corresponding event, as defined in the EPH STATUS

REGISTER bit description, occurs. Note that the counters can only increment once per enqueued transmit

packet, never faster, limiting the rate of interrupts that can be generated by the counters. For example if a

packet is successfully transmitted after one collision the SINGLE COLLISION COUNT field is incremented

by one. If a packet experiences between 2 to 16 collisions, the MULTIPLE COLLISION COUNT field is

incremented by one. If a packet experiences deferral the NUMBER OF DEFERRED TX field is

incremented by one, even if the packet experienced multiple deferrals during its collision retries.

The COUNTER REGISTER facilitates maintaining statistics in the AUTO RELEASE mode where no

transmit interrupts are generated on successful transmissions.

Reading the register in the transmit service routine will be enough to maintain statistics.

BANK 0

OFFSET

8

NAME

TYPE

SYMBOL

MIR

MEMORY INFORMATION

REGISTER

READ ONLY

HIGH

BYTE

LOW

BYTE

FREE MEMORY AVAILABLE (IN BYTES * 256 * M)

1

1

1

MEMORY SIZE (IN BYTES *256 * M)

1

1

1

1

1

1

1

1

1

1

1

1

1

FREE MEMORY AVAILABLE - This register can be read at any time to determine the amount of free

memory. The register defaults to the MEMORY SIZE upon reset or upon the RESET MMU command.

MEMORY SIZE - This register can be read to determine the total memory size.

All memory related information is represented in 256 * M byte units, where the multiplier M is determined

by the MCR upper byte.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| LAN91C100FDREVD | FEAST FAST ETHERNET CONTROLLER WITH FULL DUPLEX CAPABILITY |

| LAN91C100FDREVB | FEAST FAST ETHERNET CONTROLLER WITH FULL DUPLEX CAPABILITY |

| LAN91C100FDTQFP | FEAST FAST ETHERNET CONTROLLER WITH FULL DUPLEX CAPABILITY |

| LAN91C100 | FEAST⑩ Fast Ethernet Controller |

| LAN91C110 | FEAST FAST ETHERNET CONTROLLER FOR PCMCIA AND GENERIC 16-BIT APPLICATIONS |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| LAN91C100-FD | 制造商:SMSC 制造商全稱:SMSC 功能描述:FEAST Fast Ethernet Controller with Full Duplex Capability |

| LAN91C100FD(208PQFP) | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:LAN Node Controller |

| LAN91C100FD(208TQFP) | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:LAN Node Controller |

| LAN91C100FD_06 | 制造商:SMSC 制造商全稱:SMSC 功能描述:FEAST Fast Ethernet Controller with Full Duplex Capability |

| LAN91C100FD_0601 | 制造商:SMSC 制造商全稱:SMSC 功能描述:FEAST Fast Ethernet Controller with Full Duplex Capability |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。