- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄30751 > LM4548VHX/NOPB (NATIONAL SEMICONDUCTOR CORP) SPECIALTY CONSUMER CIRCUIT, PQFP48 PDF資料下載

參數(shù)資料

| 型號: | LM4548VHX/NOPB |

| 廠商: | NATIONAL SEMICONDUCTOR CORP |

| 元件分類: | 消費家電 |

| 英文描述: | SPECIALTY CONSUMER CIRCUIT, PQFP48 |

| 封裝: | 7 X 7 MM, 1.40 MM HEIGHT, TQFP-48 |

| 文件頁數(shù): | 17/17頁 |

| 文件大小: | 328K |

| 代理商: | LM4548VHX/NOPB |

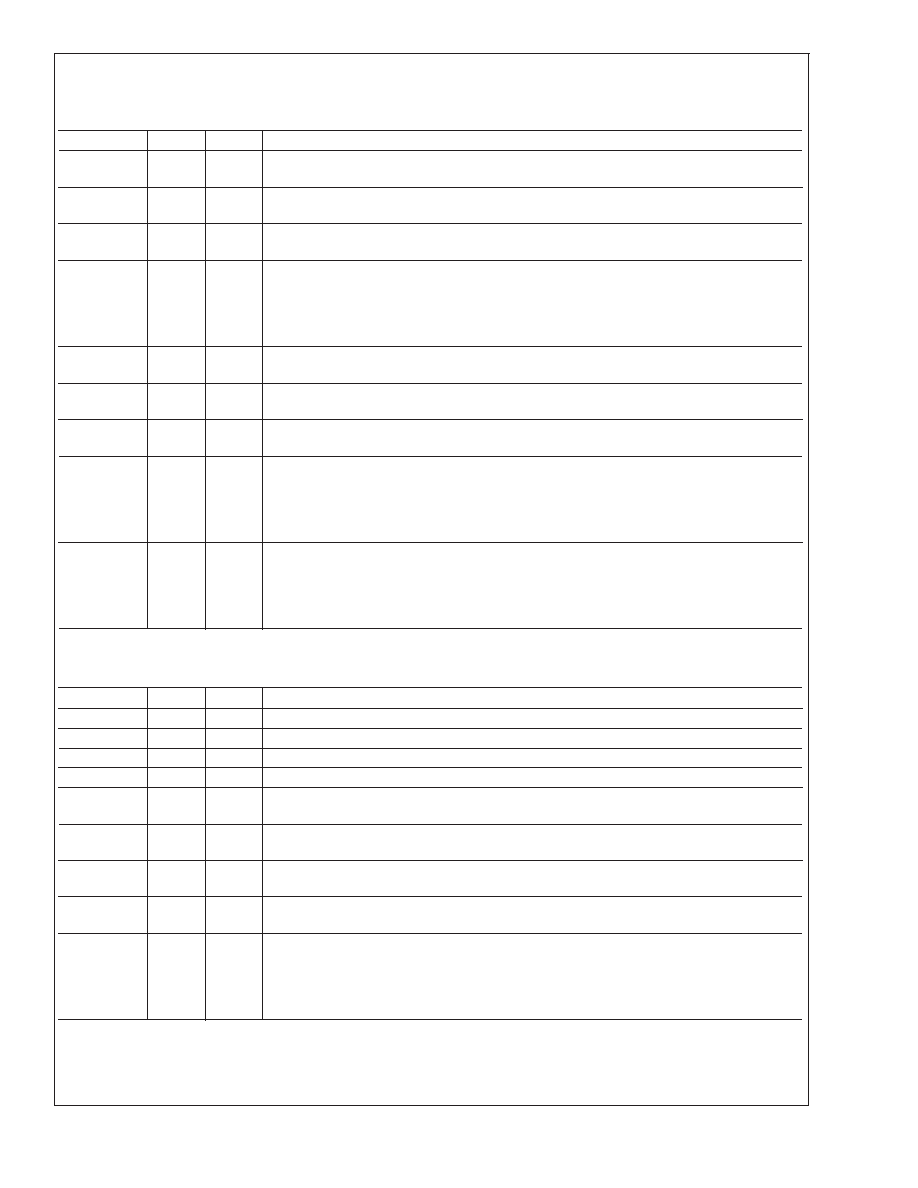

Pin Description (Continued)

Digital I/O and Clocking

Name

Pin

I / O

Functional Description

XTL_IN

2

I

24.576 MHz crystal input. Use a fundamental-mode type crystal. When operating from a

crystal, a 1M

resistor must be connected across pins 2 and 3.

XTL_OUT

3

O

24.576 MHz crystal output. When operating from a crystal, a 1M

resistor must be

connected across pins 2 and 3.

SDATA_OUT

5

I

This data stream contains both control data and DAC audio data. This input is sampled by

the LM4548 on the falling edge of BIT_CLK.

BIT_CLK

6

I/O

OUTPUT when in Primary Codec Mode: This pin outputs a 12.288 MHz clock which is

derived (internally divided by two) from the 24.576MHz crystal input (XTL_IN).

INPUT when in Secondary Codec Mode (Multiple Codec configurations only): 12.288MHz

clock is to be supplied from an external source, such as from the BIT_CLK of a Primary

Codec.

SDATA_IN

8

O

This data stream contains both control data and ADC audio data. This output is clocked out

by the LM4548 on the rising edge of BIT_CLK.

SYNC

10

I

48kHz sync pulse which signifies the beginning of both the SDATA_IN and SDATA_OUT

serial streams. SYNC must be synchronous to BIT_CLK.

RESET#

11

I

This active low signal causes a hardware reset which returns the control registers to their

default conditions.

ID0

45

I

ID0 and ID1 set the codec address for multiple codec use where ID0 is the LSB. Connect

these pins to DVdd or GND as required. If these pins are not connected (NC), they default

to Master Codec setting (same as connecting both pins to GND). These pins are of the

same polarity as their internal ID0, ID1 registers. If pin 45 is connected to GND, then ID0 will

be set to

″0″ internally. Connection to DVdd corresponds to a ″1″ internally.

ID1

46

I

ID0 and ID1 set the codec address for multiple codec use where ID1 is the MSB. Connect

these pins to DVdd or GND as required. If these pins are not connected (NC), they default

to Master Codec setting (same as connecting both pins to GND). These pins are of the

same polarity as their internal ID0, ID1 registers. If pin46 is connected to GND, then ID1 will

be set to

″0″ internally. Connection to DVdd corresponds to a ″1″ internally.

Power Supplies and References

Name

Pin

I / O

Functional Description

AVDD

25

I

Analog supply.

AVSS

26

I

Analog ground.

DVDD

1,9

I

Digital supply.

DVSS

4,7

I

Digital ground.

VREF

27

O

Nominal 2.2V reference output. Not intended to sink or source current. Bypassing of this pin

should be done with short traces to maximize performance.

VREFOUT

28

O

Nominal 2.2V reference output. Can source up to 5mA of current and can be used to bias a

microphone.

AFILT1

29

O

This pin is not used and should be left open (NC). However, a capacitor to ground on this

pin is permitted - it will not affect performance.

AFILT2

30

O

This pin is not used and should be left open (NC). However, a capacitor to ground on this

pin is permitted - it will not affect performance.

3DP, 3DN

33,34

O

These pins are used to complete the National 3D Sound circuit. Connect a 0.022F

capacitor between pins 3DP and 3DN. The National 3D Sound can be turned on and off via

bit D13 in control register 20h. This is a fixed-depth type stereo enhance circuit, thus writing

to register 22h has no effect. If National 3D Sound is not needed, then these pins should be

left as no connect (NC).

LM4548

www.national.com

9

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| LM4549AVH/NOPB | SPECIALTY CONSUMER CIRCUIT, PQFP48 |

| LM4550VH/NOPB | SPECIALTY CONSUMER CIRCUIT, PQFP48 |

| LM4550VHX/NOPB | SPECIALTY CONSUMER CIRCUIT, PQFP48 |

| LM4560VJG | SPECIALTY CONSUMER CIRCUIT, PQFP100 |

| LM4651N/NOPB | 170 W, 1 CHANNEL, AUDIO AMPLIFIER, PDIP28 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| LM4549 | 制造商:NSC 制造商全稱:National Semiconductor 功能描述:AC ’97 Rev 2.1 Codec with Sample Rate Conversion and National 3D Sound |

| LM4549A | 制造商:NSC 制造商全稱:National Semiconductor 功能描述:AC ’97 Rev 2.1 Codec with Sample Rate Conversion and National 3D Sound |

| LM4549AVH | 制造商:Rochester Electronics LLC 功能描述:AC97 REV2.1 CODEC - Bulk 制造商:OC White Company 功能描述:Audio Codec 2ADC / 2DAC 18-Bit 48-Pin LQFP Tray |

| LM4549AVH WAF | 制造商:Texas Instruments 功能描述: |

| LM4549AVH/NOPB | 制造商:Texas Instruments 功能描述:Audio Codec 2ADC / 2DAC 18-Bit 48-Pin LQFP Tray |

發(fā)布緊急采購,3分鐘左右您將得到回復。