- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄358934 > LPC47M14X (SMSC Corporation) 128 PIN ENGANCED SUPER I/O CONTROLLER WITH AN LPC INTERFACE AND USB HUB PDF資料下載

參數(shù)資料

| 型號(hào): | LPC47M14X |

| 廠商: | SMSC Corporation |

| 英文描述: | 128 PIN ENGANCED SUPER I/O CONTROLLER WITH AN LPC INTERFACE AND USB HUB |

| 中文描述: | 128引腳ENGANCED超級(jí)I / O與LPC接口和USB集線器控制器 |

| 文件頁數(shù): | 127/205頁 |

| 文件大?。?/td> | 1219K |

| 代理商: | LPC47M14X |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁第122頁第123頁第124頁第125頁第126頁當(dāng)前第127頁第128頁第129頁第130頁第131頁第132頁第133頁第134頁第135頁第136頁第137頁第138頁第139頁第140頁第141頁第142頁第143頁第144頁第145頁第146頁第147頁第148頁第149頁第150頁第151頁第152頁第153頁第154頁第155頁第156頁第157頁第158頁第159頁第160頁第161頁第162頁第163頁第164頁第165頁第166頁第167頁第168頁第169頁第170頁第171頁第172頁第173頁第174頁第175頁第176頁第177頁第178頁第179頁第180頁第181頁第182頁第183頁第184頁第185頁第186頁第187頁第188頁第189頁第190頁第191頁第192頁第193頁第194頁第195頁第196頁第197頁第198頁第199頁第200頁第201頁第202頁第203頁第204頁第205頁

SMSC DS – LPC47M14X

Page 127

Rev. 03/19/2001

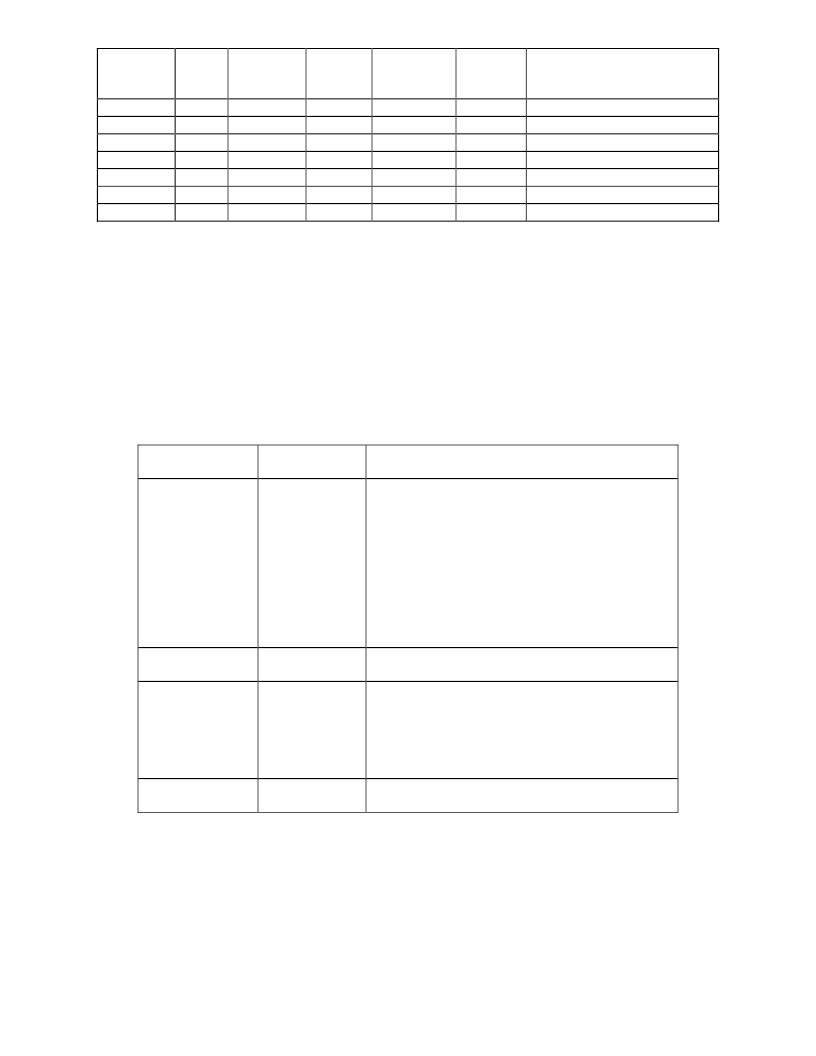

REGISTER

OFFSET

(hex)

TYPE

R

R/W

R/W

R/W

R/W

R/W

R

HARD

RESET

VCC POR

-

-

-

-

-

-

-

VTR POR

0x00

0x00

0x00

0x00

0x00

0x00

-

SOFT

RESET

REGISTER

5A

5B

5C

5D

5E

5F

60-7F

-

-

-

-

-

-

-

-

-

-

-

-

-

-

Fan2 Tachometer Register

Fan1 Preload Register

Fan2 Preload Register

LED1

LED2

Keyboard Scan Code

Reserved – reads return 0

Note 1:

This register is read-only when GP43 register bit [3:2] = 01 and the GP43 pin is high.

Note 2:

Bits [3:2] of this register are reset (cleared) on VCC POR and Hard Reset (and VTR POR).

Note 3:

Bit 3 of this register is reset (cleared) on VCC POR and Hard Reset (and VTR POR).

Note 4:

The parallel port interrupt defaults to 1 when the parallel port activate bit is cleared.

Note 5:

Bits 2 and 3 of the PME_STS4 and SMI_STS4 registers, and bit 3 of the PME_STS5 register may be set on a

VCC POR. If GP32, GP33 and GP53 are configured as input, then their corresponding PME and SMI status bits will be

set on a VCC POR

Also, GP32 and GP33

pins revert to their non-inverting GPIO

input

function when VCC is removed

from the part. These GPIOs cannot be used for PME wakeup when the part is under VTR power (VCC=0).

The following registers are located at an offset from (PME_BLK) the address programmed into the base I/O address

register for Logical Device A.

Table 59 – PME, SMI, GPIO, FAN Register Description

NAME

REG OFFSET

(hex)

DESCRIPTION

PME_STS

Default = 0x00

on VTR POR

00

(R/W)

Bit[0] PME_Status

= 0 (default)

= 1 Set when LPC47M14x would normally assert the

nIO_PME signal, independent of the state of the

PME_En bit.

Bit[7:1] Reserved

PME_Status is not affected by Vcc POR, SOFT RESET

or HARD RESET.

Writing a “1” to PME_Status will clear it and cause the

LPC47M14x to stop asserting nIO_PME, in enabled.

Writing a “0” to PME_Status has no effect.

Reserved – reads return 0

N/A

01

(R)

02

(R/W)

PME_EN

Default = 0x00

on VTR POR

Bit[0] PME_En

= 0 nIO_PME signal assertion is disabled (default)

= 1 Enables LPC47M14x to assert nIO_PME signal

Bit[7:1] Reserved

PME_En is not affected by Vcc POR, SOFT RESET or

HARD RESET

Reserved – reads return 0

N/A

03

(R)

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| LPC47M14B-NC | GE KIT:CAT5 VGA VIDEO 4CHSPLITTER & 3 LR REMOTES |

| LPC47M14D-NC | POS LASER SCANNER CABLE B |

| LPC47M14F-NC | DEVICE BOX 1 3/8"DX3/4"LX SCA- |

| LPC47M14G-NC | Electrical Duct/Raceway Fitting; |

| LPC47M14J-NC | 4 PR 568B RJ45 STR UTP CASHD-ST54PVU-568B-BG-015 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| LPC47M14X-NC | 制造商:SMSC 制造商全稱:SMSC 功能描述:128 PIN ENGANCED SUPER I/O CONTROLLER WITH AN LPC INTERFACE AND USB HUB |

| LPC47M14Y-NC | 制造商:SMSC 制造商全稱:SMSC 功能描述:128 PIN ENGANCED SUPER I/O CONTROLLER WITH AN LPC INTERFACE AND USB HUB |

| LPC47M14Z-NC | 制造商:SMSC 制造商全稱:SMSC 功能描述:128 PIN ENGANCED SUPER I/O CONTROLLER WITH AN LPC INTERFACE AND USB HUB |

| LPC47M157-NC | 制造商:Rochester Electronics LLC 功能描述:- Bulk 制造商:SMSC 功能描述: |

| LPC47M172 | 制造商:SMSC 制造商全稱:SMSC 功能描述:Advanced I/O Controller with Motherboard GLUE Logic |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。