- 您現(xiàn)在的位置:買賣IC網 > PDF目錄377665 > LS845 (Linear Integrated Systems) ULTRA LOW NOISE LOW DRIFT MONOLITHIC DUAL N-CHANNEL JFET PDF資料下載

參數(shù)資料

| 型號: | LS845 |

| 廠商: | Linear Integrated Systems |

| 英文描述: | ULTRA LOW NOISE LOW DRIFT MONOLITHIC DUAL N-CHANNEL JFET |

| 中文描述: | 超低噪音低漂移整體式雙N溝道結型場效應管 |

| 文件頁數(shù): | 1/2頁 |

| 文件大小: | 32K |

| 代理商: | LS845 |

Linear Integrated Systems

Linear Integrated Systems

4042 Clipper Court, Fremont, CA 94538 TEL: (510) 490-9160 FAX: (510) 353-0261

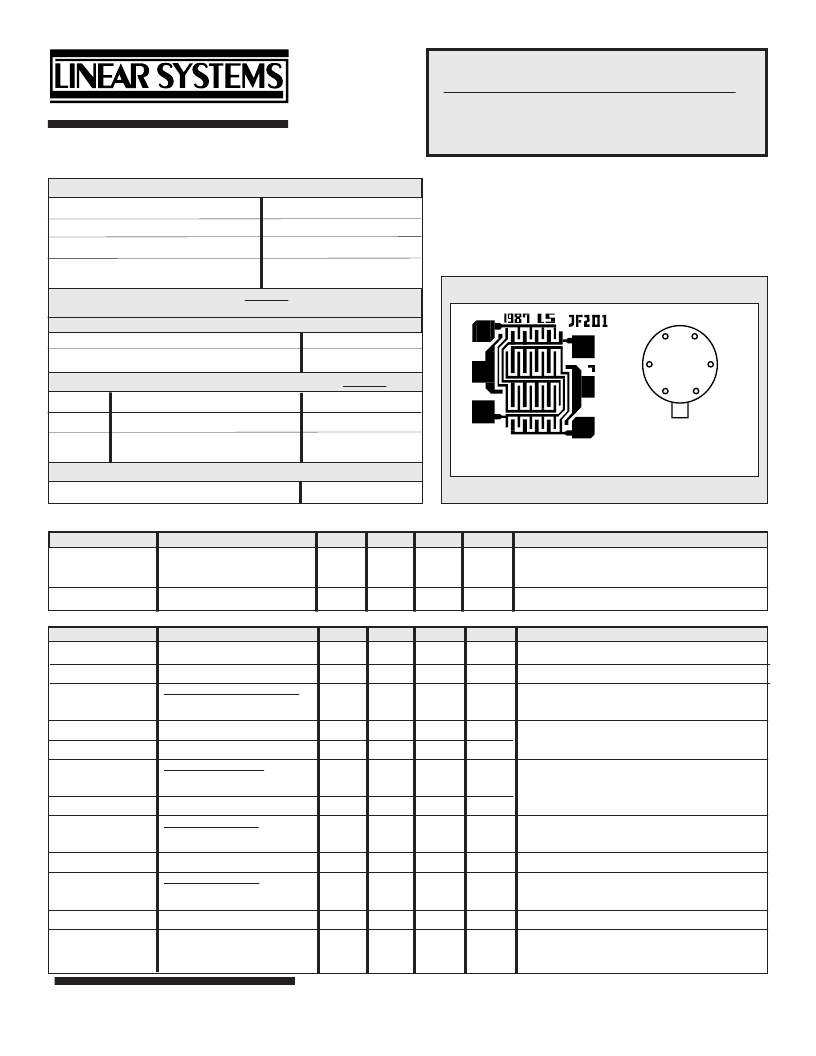

1 7

S1

3

BOTTOM VIEW

2

6

31 X 32 MILS

D1

G1

S2

S1

G2

D2

G1

S2

G2

D1

D2

FEATURES

ULTRA LOW NOISE

e

n

= 3nV/

√

Hz TYP.

I

G

= 15pA TYPs.

|

V

GS1-2

/

T|= 5

μ

V/

°

C max.

IV

GS1-2

I= 1mV max.

LOW LEAKAGE

LOW DRIFT

ULTRA LOW OFFSET VOLTAGE

ABSOLUTE MAXIMUM RATINGS NOTE 1

@ 25

°

C (unless otherwise noted)

Maximum Temperatures

Storage Temperature

Operating Junction Temperature

-65

°

to +150

°

C

+150

°

C

Maximum Voltage and Current for Each Transistor NOTE 1

-V

GSS

-V

DSO

-I

G(f)

Gate Voltage to Drain or Source

Drain to Source Voltage

Gate Forward Current

60V

60V

50mA

Maximum Power Dissipation

Device Dissipation @ Free Air - Total

400mW @ +125

°

C

ELECTRICAL CHARACTERISTICS @ 25

°

C (unless otherwise noted)

SYMBOL

CHARACTERISTICS

|

V

GS1-2

/

T| max. Drift vs. Temperature

LS843 LS844 LS845 UNITS CONDITIONS

5

10

25

μ

V/

°

C

V

DG

= 10V

T

A

= -55

°

C to +125

°

C

V

DG

= 10V

I

D

= 500

μ

A

|V

GS1-2

| max.

Offset Voltage

1

5

15

mV

I

D

= 500

μ

A

LS843 LS844 LS845

ULTRA LOW NOISE LOW DRIFT

MONOLITHIC DUAL

N-CHANNEL JFET

SYMBOL

BV

GSS

BV

GGO

CHARACTERISTICS

Breakdown Voltage

Gate-to-Gate Breakdown

TRANSCONDUCTANCE

Full Conduction

Typical Conduction

Mismatch

DRAIN CURRENT

Full Conduction

Mismatch at Full Conduction

GATE VOLTAGE

Pinchoff Voltage

Operating Range

GATE CURRENT

Operating

High Temperature

Reduced VDG

At Full Conduction

MIN. TYP. MAX. UNITS CONDITIONS

60

--

--

60

--

--

V

V

V

DS

= 0

I

G

= 1nA

I

D

= 1nA

I

D

= 0

I

S

= 0

Y

fss

Y

fs

|Y

fs1-2

/Y

fs

|

1500

1000

--

--

1500

0.6

--

--

3

μ

mho

μ

mho

%

V

DG

= 15V

V

DG

= 15V

V

GS

= 0

I

D

= 500

μ

A

f= 1kHz

I

DSS

|I

DSS1-2

/I

DSS

|

1.5

--

5

1

15

5

mA

%

V

DG

= 15V

V

GS

= 0

V

GS

(off) or V

P

V

GS

1

0.5

--

--

3.5

3.5

V

V

V

DS

= 15V

V

DS

= 15V

I

D

= 1nA

I

D

= 500

μ

A

-I

G

-I

G

-I

G

-I

GSS

--

--

--

--

15

--

5

--

50

50

30

100

pA

nA

pA

pA

V

DG

= 15V

V

DG

= 15V

V

DG

= 3V

V

DG

= 15V

I

D

= 500

μ

A

I

D

= 500

μ

A

I

D

= 500

μ

A

V

DS

= 0

T

A

= +125

°

C

相關PDF資料 |

PDF描述 |

|---|---|

| LS843 | ULTRA LOW NOISE LOW DRIFT MONOLITHIC DUAL N-CHANNEL JFET |

| LS846 | LOW NOISE, LOW LEAKAGE SINGLE N-CHANNEL JFET |

| LS86 | Quad 2-Input Exclusive OR Gate |

| LSFA02-422-800K0 | 400MHz Band SAW Filter of Low power consumption |

| LSFA02-440-400K0 | 400MHz Band SAW Filter of Low power consumption |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| LS845_PDIP | 制造商:MICROSS 制造商全稱:MICROSS 功能描述:MONOLITHIC DUAL N-CHANNEL JFET |

| LS845_SOIC | 制造商:MICROSS 制造商全稱:MICROSS 功能描述:MONOLITHIC DUAL N-CHANNEL JFET |

| LS845_SOT-23 | 制造商:MICROSS 制造商全稱:MICROSS 功能描述:MONOLITHIC DUAL N-CHANNEL JFET |

| LS845_TO-71 | 制造商:MICROSS 制造商全稱:MICROSS 功能描述:MONOLITHIC DUAL N-CHANNEL JFET |

| LS845_TO-78 | 制造商:MICROSS 制造商全稱:MICROSS 功能描述:MONOLITHIC DUAL N-CHANNEL JFET |

發(fā)布緊急采購,3分鐘左右您將得到回復。