- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄369842 > LSIFC929 LSIFC929 dual channel fibre solutions PDF資料下載

參數(shù)資料

| 型號(hào): | LSIFC929 |

| 英文描述: | LSIFC929 dual channel fibre solutions |

| 中文描述: | LSIFC929雙通道光纖解決方案 |

| 文件頁數(shù): | 16/144頁 |

| 文件大?。?/td> | 1496K |

| 代理商: | LSIFC929 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁當(dāng)前第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁第122頁第123頁第124頁第125頁第126頁第127頁第128頁第129頁第130頁第131頁第132頁第133頁第134頁第135頁第136頁第137頁第138頁第139頁第140頁第141頁第142頁第143頁第144頁

1-4

Introduction

efficiency. Special attention has been given to the design to accelerate

context switching and link utilization.

The LSIFC909 includes a 64-bit, 66 MHz PCI interface to the host

environment. This high speed (528 Mbytes/s), industry standard interface

provides sufficient bandwidth to the host CPU and system memory to

support full duplex FC data rates. The host interface design minimizes

the time spent on the PCI bus for nondata moving activities such as

initialization, command, and error recovery. In addition, the host interface

has the inherent flexibility to support the OEM implementation tradeoffs

between CPU, PCI, and I/O bandwidth.

The high level of integration in the LSIFC909 Controller enables low cost

FC implementations.

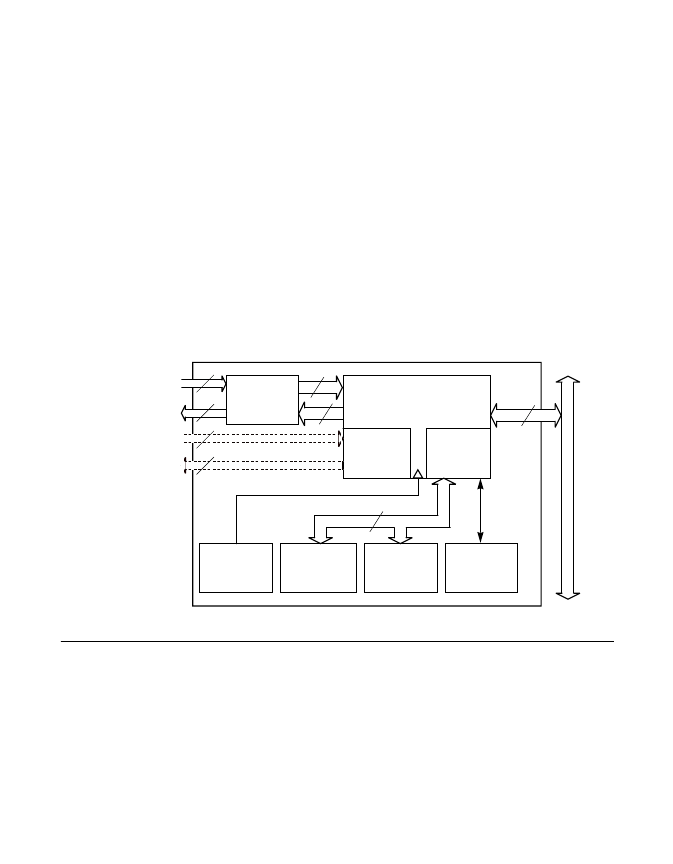

Figure 1.1

shows a typical configuration

incorporating the LSIFC909 Controller to implement a FC NL_Port.

Figure 1.1

LSIFC909 Typical Implementation

1.3 Hardware Overview

In today’s fast growing server, RAID, and workstation marketplaces,

higher levels of performance, scalability, and reliability are required to

stay competitive in the SAN market.

2

External

Transceiver

2

LSIFC909

Integrated

Transceiver

Memory

Controller

10

10

2

2

Serial

EEPROM

(2 Kbyte)

Flash

(1 Mbyte)

SSRAM

(1 Mbyte typ.)

Clock

(106 MHz)

32

PCI Bus

32/64

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。