- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄1933 > LTC1064CSW#TRPBF (Linear Technology)IC FILTR BUILDNG BLK QUAD 24SOIC PDF資料下載

參數(shù)資料

| 型號(hào): | LTC1064CSW#TRPBF |

| 廠商: | Linear Technology |

| 文件頁數(shù): | 14/20頁 |

| 文件大小: | 0K |

| 描述: | IC FILTR BUILDNG BLK QUAD 24SOIC |

| 標(biāo)準(zhǔn)包裝: | 1,000 |

| 濾波器類型: | 通用開關(guān)電容器 |

| 頻率 - 截止或中心: | 140kHz |

| 濾波器數(shù): | 4 |

| 濾波器階數(shù): | 8th |

| 電源電壓: | ±2.37 V ~ 8 V |

| 安裝類型: | 表面貼裝 |

| 封裝/外殼: | 24-SOIC(0.295",7.50mm 寬) |

| 供應(yīng)商設(shè)備封裝: | 24-SOIC |

| 包裝: | 帶卷 (TR) |

LTC1064

3

1064fb

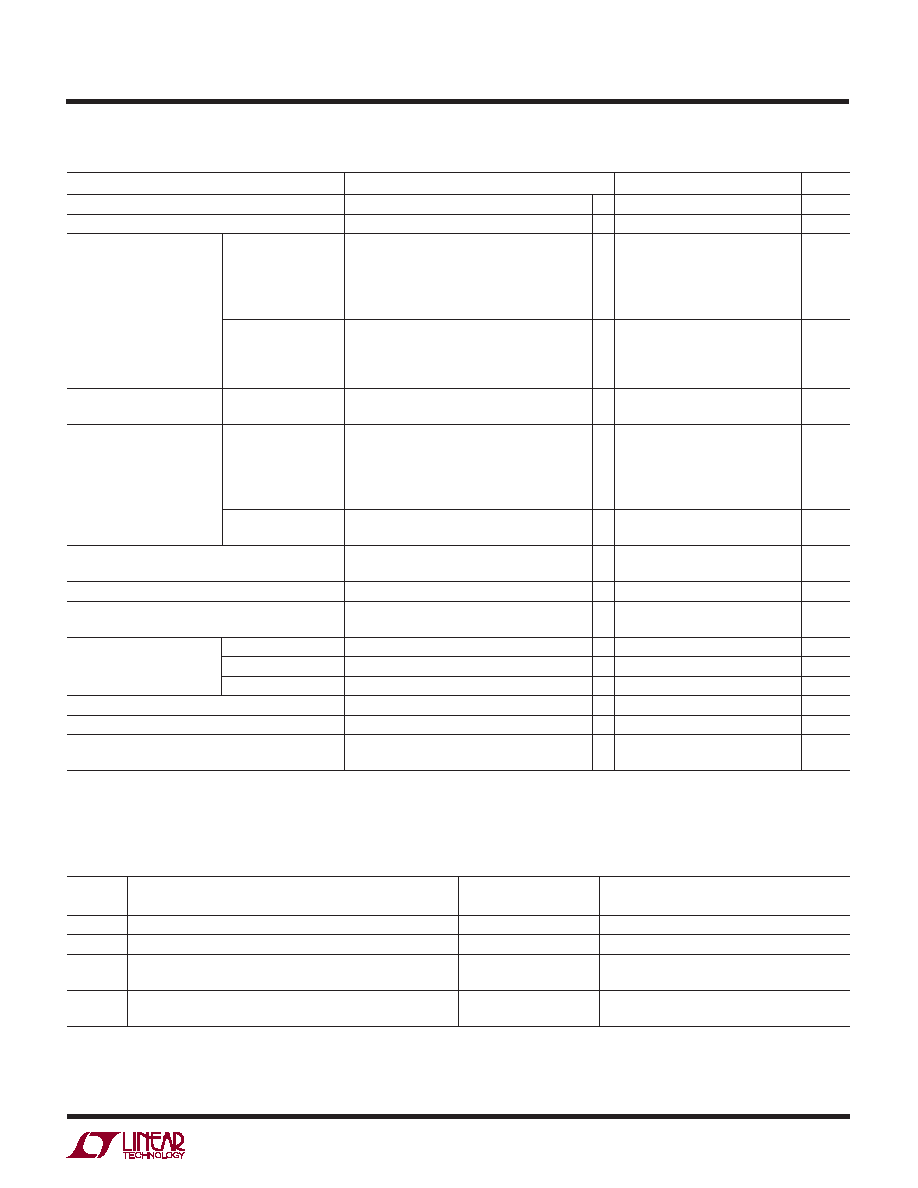

ELECTRICAL CHARACTERISTICS (Complete Filter) The ● denotes the specifications which apply over the full

operating temperature range, otherwise specifications are at VS = ±5V, TA = 25°C, TTL clock input level, unless otherwise specified.

Note 1: Absolute Maximum Ratings are those values beyond which the life

of a device may be impaired.

PARAMETER

CONDITIONS

MIN

TYP

MAX

UNITS

Center Frequency Range, fO

VS = ±8V, Q ≤ 3

0.1 to 140

kHz

Input Frequency Range

0 to 1

MHz

Clock-to-Center Frequency

LTC1064

fCLK = 1MHz, fO = 20kHz, Pin 17 High

50

± 0.3

%

Ratio, fCLK/fO

LTC1064A (Note 2)

Sides A, B, C: Mode 1,

●

50

± 0.8

%

R1 = R3 = 5k, R2 = 5k, Q = 10,

Sides D: Mode 3, R1 = R3 = 50k

●

50

± 0.9

%

R2 = R4 = 5k

LTC1064

Same as Above, Pin 17 Low, fCLK = 1MHz

100

± 0.3

%

LTC1064A (Note 2)

fO = 10kHz

Sides A, B, C

●

100

± 0.8

%

Side D

●

100

± 0.9

Clock-to-Center Frequency

LTC1064

fCLK = 1MHz

0.4

%

Ratio, Side-to-Side Matching

LTC1064A (Note 2)

●

1%

Clock-to-Center Frequency

LTC1064

fCLK = 4MHz, fO = 80kHz, Pin 17 High

50

± 0.6

%

Ratio, fCLK/fO (Note 3)

LTC1064A (Note 2)

Sides A, B, C: Mode 1, VS = ±7.5V

50

± 1.3

%

R1 = R3 = 50k, R2 = 5k, Q = 5

Side D: Mode 3, R1 = R3 = 50k

R2 = R4 = 5k, fCLK = 4MHz

LTC1064

Same as Above, Pin 17 Low

100

± 0.6

%

LTC1064 A (Note 2)

fCLK = 4MHz, fO = 40kHz

100

± 1.3

%

Q Accuracy

Sides A, B, C: Mode 1, Q = 10

●

±26

%

Side D: Mode 3, fCLK = 1MHz

●

±38

%

fO Temperature Coefficient

Mode 1, 50:1, fCLK < 2MHz

±1

ppm/

°C

Q Temperature Coefficient

Mode 1, 100:1, fCLK < 2MHz

±5

ppm/

°C

Mode 3, fCLK < 2MHz

±5

ppm/

°C

DC Offset Voltage

VOS1 (Table 1)

fCLK = 1MHz, 50:1 or 100:1

●

215

mV

VOS2 (Table 1)

fCLK = 1MHz, 50:1 or 100:1

●

345

mV

VOS3 (Table 1)

fCLK = 1MHz, 50:1 or 100:1

●

345

mV

Clock Feedthrough

fCLK < 1MHz

0.2

mVRMS

Maximum Clock Frequency

Mode 1, Q < 5, VS ≥ ±5V

7

MHz

Power Supply Current

912

23

mA

●

26

mA

VOSN

VOSBP

VOSLP

MODE

PINS 2, 11, 14, 23

PINS 3, 10, 15, 22

PINS 4, 9, 16, 21

1VOS1 [(1/Q) + 1 + HOLP] – VOS3/Q

VOS3

VOSN – VOS2

1b

VOS1 [(1/Q) + 1 + (R2/R1)] – VOS3/Q

VOS3

~(VOSN – VOS2)[1 + (R5/R6)]

2VOS1 [(1 + (R2/R1) + (R2/R3) + (R2/R4) – VOS3(R2/R3)]

VOS3

VOSN – VOS2

× [R4/(R2 + R4)] + VOS2[R2/(R2 + R4)]

3VOS2

VOS3

VOS1[1 + (R4/R1) + (R4/R2) + (R4/R3)]

– VOS2(R4/R2) – VOS3(R4/R3)

Table 1. Output DC Offsets, One 2nd Order Section

Note 2: Contact LTC Marketing.

Note 3: Not tested, guaranteed by design.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| LTC1065IN8#PBF | IC FILTR 5TH ORDR LOWPASS 8-DIP |

| LTC1066-1CSW#TRPBF | IC FILTR 8TH ORDR LOWPASS 18SOIC |

| LTC1067CGN#TRPBF | IC FILTR BLDNGBLK R-R DUAL16SSOP |

| LTC1068-25IG#TRPBF | IC FILTR BUILDNG BLK QUAD 28SSOP |

| LTC1069-1IN8#PBF | IC FILTR 8TH ORDER LOWPASS 8-DIP |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| LTC1064M | 制造商:LINER 制造商全稱:Linear Technology 功能描述:Low Noise, Fast, Quad Universal Filter Building Block |

| LTC1064MJ | 制造商:LINER 制造商全稱:Linear Technology 功能描述:Low Noise, Fast, Quad Universal Filter Building Block |

| LTC1065 | 制造商:LINER 制造商全稱:Linear Technology 功能描述:DC Accurate, Clock-Tunable Linear Phase 5th Order Bessel Lowpass Filter |

| LTC1065_09 | 制造商:LINER 制造商全稱:Linear Technology 功能描述:DC Accurate, Clock-Tunable Linear Phase 5th Order Bessel Lowpass Filter |

| LTC1065C | 制造商:LINER 制造商全稱:Linear Technology 功能描述:DC Accurate, Clock-Tunable Linear Phase 5th Order Bessel Lowpass Filter |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。