- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄377801 > M13S128168A-7.5AB (Elite Semiconductor Memory Technology Inc.) 2M x 16 Bit x 4 Banks Double Data Rate SDRAM PDF資料下載

參數(shù)資料

| 型號(hào): | M13S128168A-7.5AB |

| 廠商: | Elite Semiconductor Memory Technology Inc. |

| 英文描述: | 2M x 16 Bit x 4 Banks Double Data Rate SDRAM |

| 中文描述: | 200萬(wàn)× 16位× 4個(gè)銀行雙倍數(shù)據(jù)速率SDRAM |

| 文件頁(yè)數(shù): | 12/49頁(yè) |

| 文件大?。?/td> | 1513K |

| 代理商: | M13S128168A-7.5AB |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)當(dāng)前第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)

ES MT

M13S128168A

Elite Semiconductor Memory Technology Inc.

Publication Date : Jun. 2007

Revision : 1.8 12/49

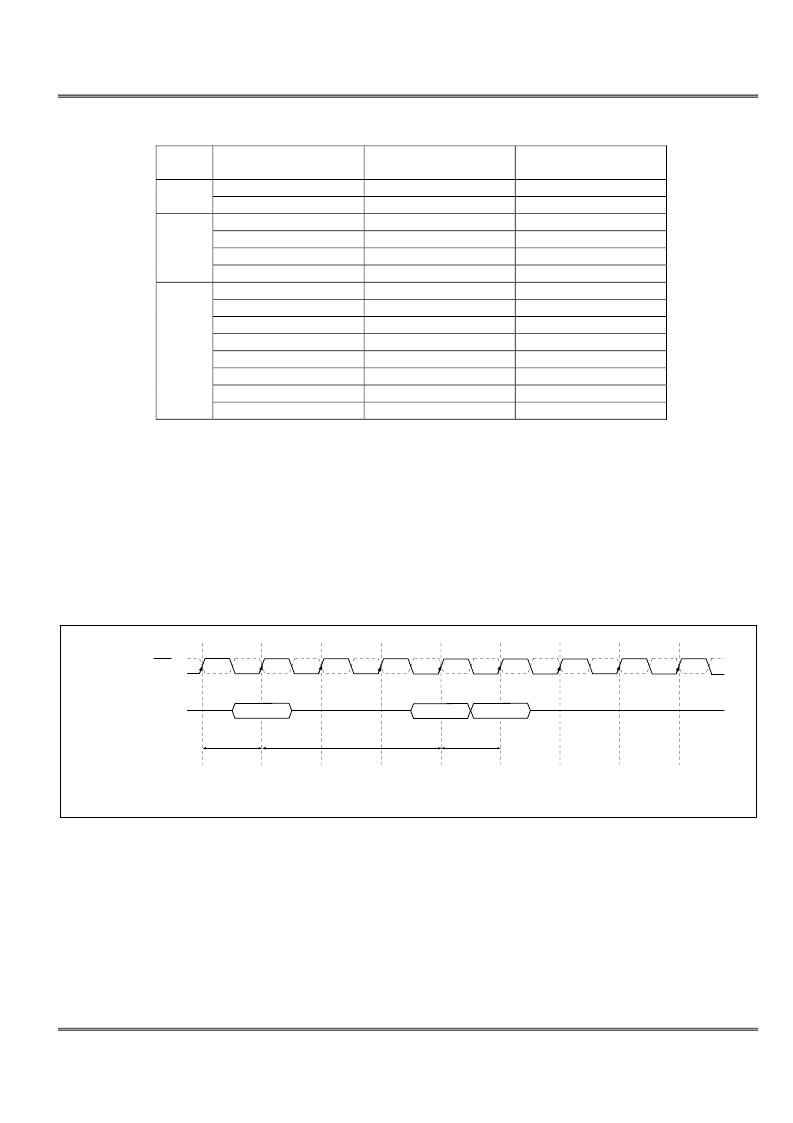

Burst Address Ordering for Burst Length

Starting

Address (A2, A1,A0)

xx0

xx1

x00

x01

x10

x11

000

0, 1, 2, 3, 4, 5, 6, 7

001

1, 2, 3, 4, 5, 6, 7, 0

010

2, 3, 4, 5, 6, 7, 0, 1

011

3, 4, 5, 6, 7, 0, 1, 2

100

4, 5, 6, 7, 0, 1, 2, 3

101

5, 6, 7, 0, 1, 2, 3, 4

110

6, 7, 0, 1, 2, 3, 4, 5

111

7, 0, 1, 2, 3, 4, 5, 6

Burst

Length

Sequential Mode

Interleave Mode

0, 1

1, 0

0, 1

1, 0

2

0, 1, 2, 3

1, 2, 3, 0

2, 3, 0, 1

3, 0, 1, 2

0, 1, 2, 3

1, 0, 3, 2

2, 3, 0, 1

3, 2, 1, 0

4

0, 1, 2, 3, 4, 5, 6, 7

1, 0, 3, 2, 5, 4, 7, 6

2, 3, 0, 1, 6, 7, 4, 5

3, 2, 1, 0, 7, 6, 5, 4

4, 5, 6, 7, 0, 1, 2, 3

5, 4, 7, 6, 1, 0, 3, 2

6, 7, 4, 5, 2, 3, 0, 1

7, 6, 5, 4, 3, 2, 1, 0

8

DLL Enable / Disable

The DLL must be enabled for normal operation. DLL enable is required during power-up initialization, and upon returning to

normal operation after having disabled the DLL for the purpose of debug or evaluation (upon exiting Self Refresh Mode, the DLL is

enable automatically). Any time the DLL is enabled, 200 clock cycles must occur before a READ command can be issued.

Output Drive Strength

The normal drive strength for all outputs is specified to be SSTL_2, Class II. M13S128168A also support a weak drive strength

option, intended for lighter load and/or point-to-point environments.

Mode Register Set

*1 : MRS can be issued only at all banks precharge state.

*2 : Minimum t

RP

is required to issue MRS command.

0

1

2

3

4

5

6

7

8

CO MM AN D

t

C K

Al l B a n k s

R e g Mo d e

CoAn y

t

R P

* 2

* 1

CLK

CLK

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| M13S128324A | 1M x 32 Bit x 4 Banks Double Data Rate SDRAM |

| M13S2561616A | 4M x 16 Bit x 4 Banks Double Data Rate SDRAM |

| M13S2561616A-4TG | 4M x 16 Bit x 4 Banks Double Data Rate SDRAM |

| M13S2561616A-5TG | 4M x 16 Bit x 4 Banks Double Data Rate SDRAM |

| M13S2561616A-6TG | 4M x 16 Bit x 4 Banks Double Data Rate SDRAM |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| M13S128324A | 制造商:ESMT 制造商全稱(chēng):Elite Semiconductor Memory Technology Inc. 功能描述:1M x 32 Bit x 4 Banks Double Data Rate SDRAM |

| M13S128324A_09 | 制造商:ESMT 制造商全稱(chēng):Elite Semiconductor Memory Technology Inc. 功能描述:1M x 32 Bit x 4 Banks Double Data Rate SDRAM |

| M13S128324A_1 | 制造商:ESMT 制造商全稱(chēng):Elite Semiconductor Memory Technology Inc. 功能描述:1M x 32 Bit x 4 Banks Double Data Rate SDRAM |

| M13S128324A-3.6BG | 制造商:ESMT 制造商全稱(chēng):Elite Semiconductor Memory Technology Inc. 功能描述:1M x 32 Bit x 4 Banks Double Data Rate SDRAM |

| M13S128324A-4BG | 制造商:ESMT 制造商全稱(chēng):Elite Semiconductor Memory Technology Inc. 功能描述:1M x 32 Bit x 4 Banks Double Data Rate SDRAM |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。