- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄377801 > M13S64164A-5TG (ELITE SEMICONDUCTOR MEMORY TECHNOLOGY INC) 1M x 16 Bit x 4 Banks Double Data Rate SDRAM PDF資料下載

參數(shù)資料

| 型號: | M13S64164A-5TG |

| 廠商: | ELITE SEMICONDUCTOR MEMORY TECHNOLOGY INC |

| 元件分類: | DRAM |

| 英文描述: | 1M x 16 Bit x 4 Banks Double Data Rate SDRAM |

| 中文描述: | 4M X 16 DDR DRAM, 0.7 ns, PDSO66 |

| 封裝: | 0.400 X 0.875 INCH, 0.65 MM PITCH, LEAD FREE, TSOP2-66 |

| 文件頁數(shù): | 21/49頁 |

| 文件大小: | 1526K |

| 代理商: | M13S64164A-5TG |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁當前第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁

ES MT

Preliminary

M13S64164A

Elite Semiconductor Memory Technology Inc.

Publication Date : Jul. 2007

Revision : 0.3 21/49

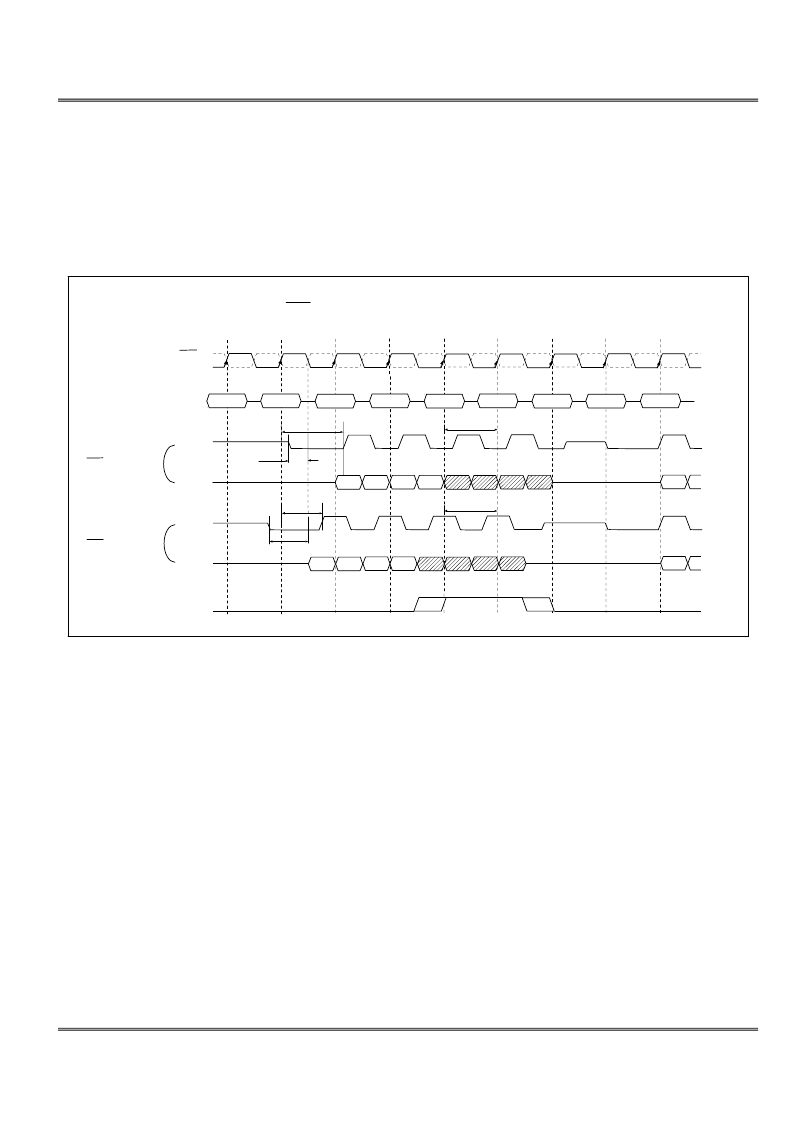

Write Interrupted by a Read & DM

A burst write can be interrupted by a read command of any bank. The DQ’s must be in the high impedance state at least one

clock cycle before the interrupting read data appear on the outputs to avoid data contention. When the read command is registered,

any residual data from the burst write cycle must be masked by DM. The delay from the last data to read command (t

WTR

) is

required to avoid the data contention DRAM inside. Data that are presented on the DQ pins before the read command is initiated

will actually be written to the memory. Read command interrupting write can not be issued at the next clock edge of that of write

command.

<Burst Length = 8, CAS Latency = 3>

The following functionality established how a Read command may interrupt a Write burst and which input data is not written into

the memory.

1. For Read commands interrupting a Write burst, the minimum Write to Read command delay is 2 clock cycles. The case where

the Write to Read delay is 1 clock cycle is disallowed.

2. For read commands interrupting a Write burst, the DM pin must be used to mask the input data words which immediately

precede the interrupting Read operation and the input data word which immediately follows the interrupting Read operation.

3. For all cases of a Read interrupting a Write, the DQ and DQS buses must be released by the driving chip (i.e., the memory

controller) in time to allow the buses to turn around before the SDRAM drives them during a read operation.

4. If input Write data is masked by the Read command, the DQS inputs is ignored by the SDRAM.

5. It is illegal for a Read command interrupt a Write with autoprecharge command.

C A S L at e n c y= 3

0

1

2

3

4

5

6

7

8

CO M M AN D

DQS

DQ 's

C A S L at e n c y= 3

DQS

DQ 's

NOP

NOP

NOP

NOP

Read

NOP

NOP

NOP

t

D Q S S m a x

D i n 0 Di n 1

W RITE

t

W P R E S

t

W T R

D i n 2

D i n 3

Di n 4 Di n 5 D i n 6 D in 7

Dout 0 Dout 1

t

D Q S S m i n

D i n 0 D in 1

t

W P R E S

t

W T R

Di n 2

D i n 3 D i n 4 Di n 5 D i n 6 D i n 7

Dout 0 Dout 1

D M

C L K

C L K

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| M13S64164A-6TG | 1M x 16 Bit x 4 Banks Double Data Rate SDRAM |

| M14256 | Memory Card IC 256K Bit Serial IIC Bus EEPROM(256K位串行IIC總線EEPROM) |

| M145026 | REMOTE CONTROL ENCODER/DECODER CIRCUIT |

| M145026B1 | REMOTE CONTROL ENCODER/DECODER CIRCUIT |

| M145026D | REMOTE CONTROL ENCODER/DECODER CIRCUIT |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| M13S64164A-5TIG | 制造商:ESMT 制造商全稱:Elite Semiconductor Memory Technology Inc. 功能描述:1M x 16 Bit x 4 Banks Double Data Rate SDRAM |

| M13S64164A-6BG | 制造商:ESMT 制造商全稱:Elite Semiconductor Memory Technology Inc. 功能描述:1M x 16 Bit x 4 Banks Double Data Rate SDRAM |

| M13S64164A-6BIG | 制造商:ESMT 制造商全稱:Elite Semiconductor Memory Technology Inc. 功能描述:1M x 16 Bit x 4 Banks Double Data Rate SDRAM |

| M13S64164A-6TG | 制造商:ESMT 制造商全稱:Elite Semiconductor Memory Technology Inc. 功能描述:1M x 16 Bit x 4 Banks Double Data Rate SDRAM |

| M13S64164A-6TIG | 制造商:ESMT 制造商全稱:Elite Semiconductor Memory Technology Inc. 功能描述:1M x 16 Bit x 4 Banks Double Data Rate SDRAM |

發(fā)布緊急采購,3分鐘左右您將得到回復。