- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄358972 > M24C64-MN3 (意法半導(dǎo)體) 16-Bit Transparent D-Type Latch With 3-State Outputs 48-SSOP -40 to 85 PDF資料下載

參數(shù)資料

| 型號(hào): | M24C64-MN3 |

| 廠商: | 意法半導(dǎo)體 |

| 英文描述: | 16-Bit Transparent D-Type Latch With 3-State Outputs 48-SSOP -40 to 85 |

| 中文描述: | 64Kbit和32Kbit串行IC總線的EEPROM |

| 文件頁(yè)數(shù): | 25/26頁(yè) |

| 文件大?。?/td> | 394K |

| 代理商: | M24C64-MN3 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)當(dāng)前第25頁(yè)第26頁(yè)

25/26

M24C64, M24C32

REVISION HISTORY

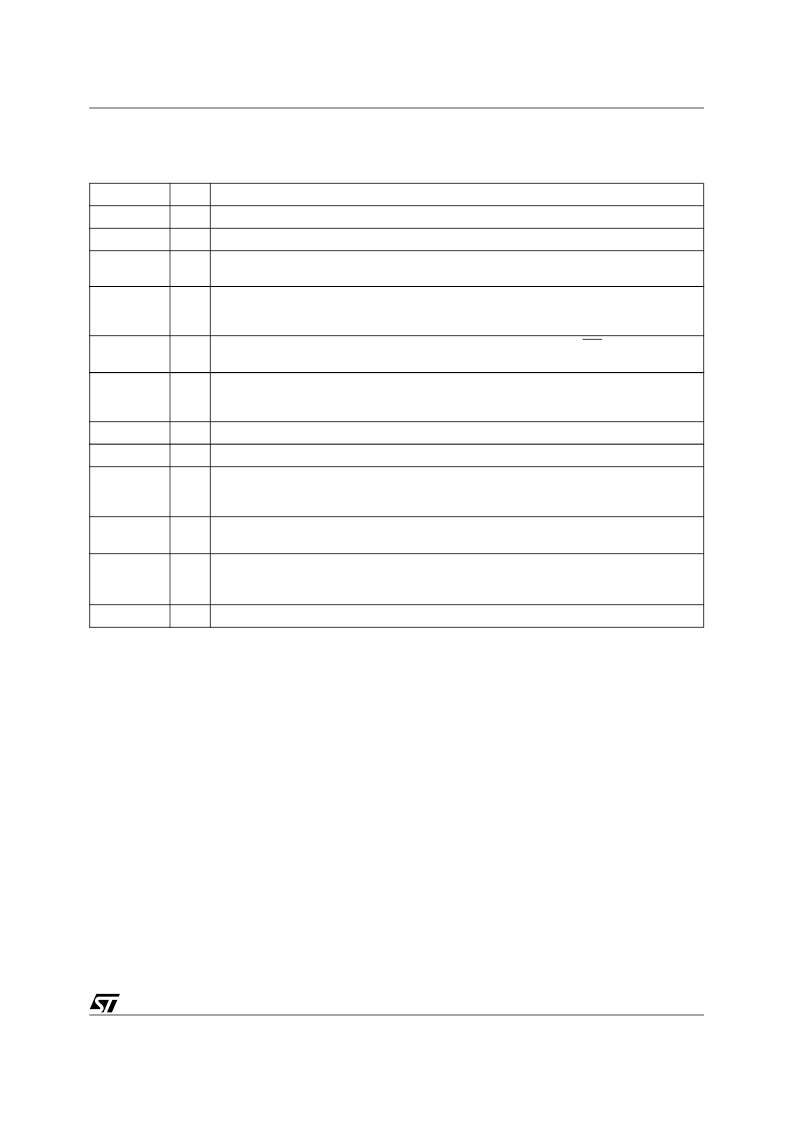

Table 23. Document Revision History

Date

Rev.

Description of Revision

22-Dec-1999

2.3

TSSOP8 package in place of TSSOP14 (pp 1, 2, OrderingInfo, PackageMechData).

28-Jun-2000

2.4

TSSOP8 package data corrected

31-Oct-2000

2.5

References to Temperature Range 3 removed from Ordering Information

Voltage range -S added, and range -R removed from text and tables throughout.

20-Apr-2001

2.6

Lead Soldering Temperature in the Absolute Maximum Ratings table amended

Write Cycle Polling Flow Chart using ACK illustration updated

References to PSDIP changed to PDIP and Package Mechanical data updated

16-Jan-2002

2.7

Test condition for I

LI

made more precise, and value of I

LI

for E2-E0 and WC added

-R voltage range added

02-Aug-2002

2.8

Document reformatted using new template.

TSSOP8 (3x3mm2 body size) package (MSOP8) added.

5ms write time offered for 5V and 2.5V devices

04-Feb-2003

2.9

SO8W package removed. -S voltage range removed

27-May-2003

2.10

TSSOP8 (3x3mm2 body size) package (MSOP8) removed

22-Oct-2003

3.0

Table of contents, and Pb-free options added. Minor wording changes in Summary

Description, Power-On Reset, Memory Addressing, Write Operations, Read Operations.

V

IL

(min) improved to -0.45V.

01-Jun-2004

4.0

Absolute Maximum Ratings for V

IO

(min) and V

CC

(min) improved. Soldering temperature

information clarified for RoHS compliant devices. Device Grade clarified

04-Nov-2004

5.0

Product List summary table added. Device Grade 3 added. 4.5-5.5V range is Not for New

Design. Some minor wording changes. AEC-Q100-002 compliance. t

NS

(max) changed.

V

IL

(min) is the same on all input pins of the device. Z

WCL

changed.

05-Jan-2005

6.0

UFDFPN8 package added. Small text changes.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| M24C64-MN3P | 16-Bit Transparent D-Type Latch With 3-State Outputs 48-SSOP -40 to 85 |

| M24C64-MN3T | 16-Bit Transparent D-Type Latch With 3-State Outputs 56-BGA MICROSTAR JUNIOR -40 to 85 |

| M24C64-MN3TP | 16-Bit Edge-Triggered D-Type Flip-Flop With 3-State Outputs 48-TSSOP -40 to 85 |

| M24C64-MN6 | The CAT24FC02 is a 2-kb Serial CMOS EEPROM internally organized as 256 words of 8 bits each |

| M24C64-MN6P | 16-Bit Edge-Triggered D-Type Flip-Flop With 3-State Outputs 48-TVSOP -40 to 85 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| M24C64-MN6 | 功能描述:電可擦除可編程只讀存儲(chǔ)器 5.5V 64K (8Kx8) RoHS:否 制造商:Atmel 存儲(chǔ)容量:2 Kbit 組織:256 B x 8 數(shù)據(jù)保留:100 yr 最大時(shí)鐘頻率:1000 KHz 最大工作電流:6 uA 工作電源電壓:1.7 V to 5.5 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:SOIC-8 |

| M24C64MN6T | 制造商:ST MICRO 功能描述:* 制造商:STMicroelectronics 功能描述: |

| M24C64-MN6T | 制造商:STMicroelectronics 功能描述: |

| M24C64-MW6 | 功能描述:電可擦除可編程只讀存儲(chǔ)器 5.5V 64K (8Kx8) RoHS:否 制造商:Atmel 存儲(chǔ)容量:2 Kbit 組織:256 B x 8 數(shù)據(jù)保留:100 yr 最大時(shí)鐘頻率:1000 KHz 最大工作電流:6 uA 工作電源電壓:1.7 V to 5.5 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:SOIC-8 |

| M24C64-MW6T | 功能描述:電可擦除可編程只讀存儲(chǔ)器 5.5V 64K (8Kx8) RoHS:否 制造商:Atmel 存儲(chǔ)容量:2 Kbit 組織:256 B x 8 數(shù)據(jù)保留:100 yr 最大時(shí)鐘頻率:1000 KHz 最大工作電流:6 uA 工作電源電壓:1.7 V to 5.5 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:SOIC-8 |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。